ся одними из выходов устройства, введены мультиплексор, формирователь тестовых сигналов, группы элементов ИЛИ, дешифратор, пятый элемент Н, третья группа элементов И, элемент НЕ, группа элементов НЕ и блок местного управления, одни из выходов которого подключены ко входам блokoв ламяти, а другие - к управляющим входам регистров и пятого элемента И, входы мультиплексора соединены с выходами блоков памяти, а выходы подключены к другим входам схемы сравнения и являются информационными выходами устройства, выходы схемы сравнения соединены со входами элементов ИЛИ групп, выходы которых подключены ко входам первого регистра и входам элементов НЕ группы, выходы которых соединены со входами пятого элемента И, выход которого подключен ко входам второго и третьего регистров, одни из входов дешифратора соединены с выходами первого, второго ичетвертого элементов И,, другой вход подключен к выходу элемента НЕ, вход которого соединен с выходом третьего элемента И, одни из входов элементов И третьей группы подключены к выходам третьего регистра, другие входы элементов И первой группы подключены к выходу элемента ИЛИ,одни из выходов дешифратора соединены со входам элемента ИЛИ и другими входами элементов И второй и третьей групп, другие выходы дешифратора, выходы элементов И третьей группы и выходы формирования тестовьох сигналов являются другими . выходами усГройства, входами которого являются входы блока местного управления и формирователя тестовых сигналов.

Кроме того, блок местного управ-, ления содержит триггеры, элементы И-НЕ, дополнительные элементы И, дополнительный элемент НЕ, регистр числа, регистр адреса и последовательно соединенные элементы задержки, выходы которых под ключены к одним из входов триггеров,причем выходы первого и BTOporb триггеров соединены с одними из входов элементов И-НЕ, выходы третьего тригхера подключены к одному из входов первого дополнительного- элемента И, входы Второго дополнительного элемента., И соединены с выходами элементов, И-НЕ, один из входов третьего дополнительного элемента И подключен к выходу дополнительного элемента НЕ, а выход - к другому входу четвертого триггера, одни из входов регистра . адреса и регистра числа и входы дополнительного элемента НЕ и одного из элементов задержки объединены и являются одним из входов блока, дру.гими входами которого являются другие входы первого, второго и третьего триггеров, элементов И-НЕ, первого и третьего дополнительных элементов И, регистра адреса и регистра числа, выходами блока являются выходы первого и второго дополнительных элементов И, третьего триггера, регистра числа и регистра адреса.

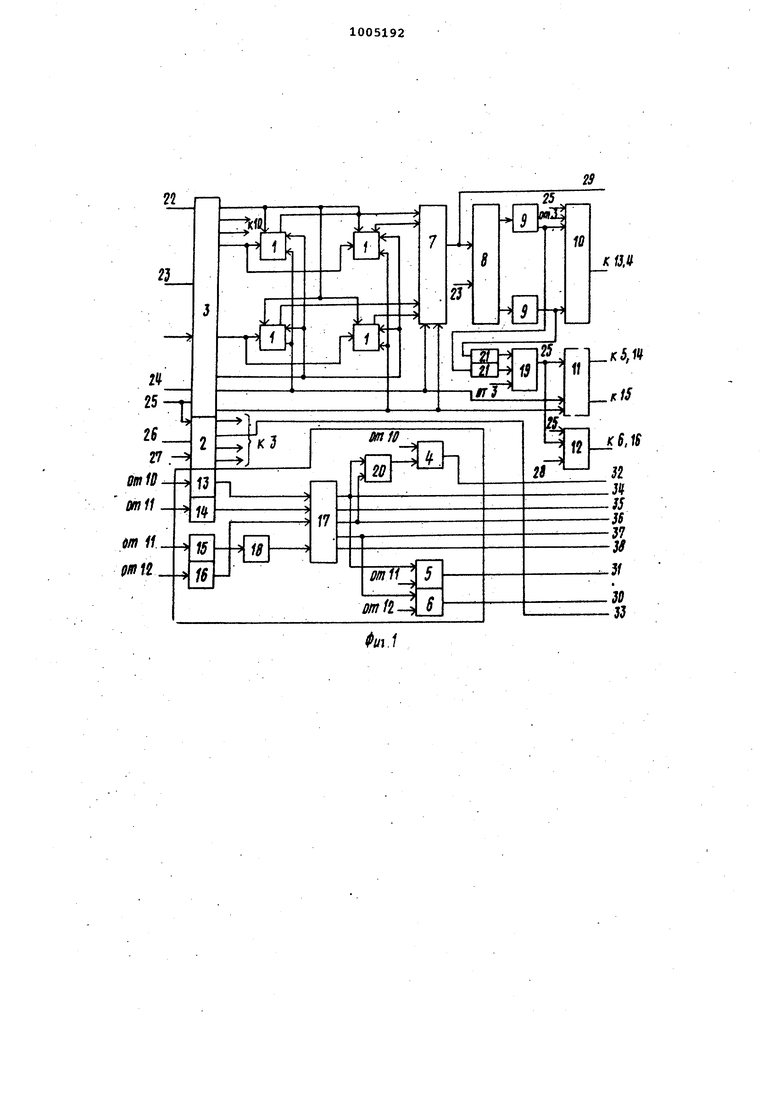

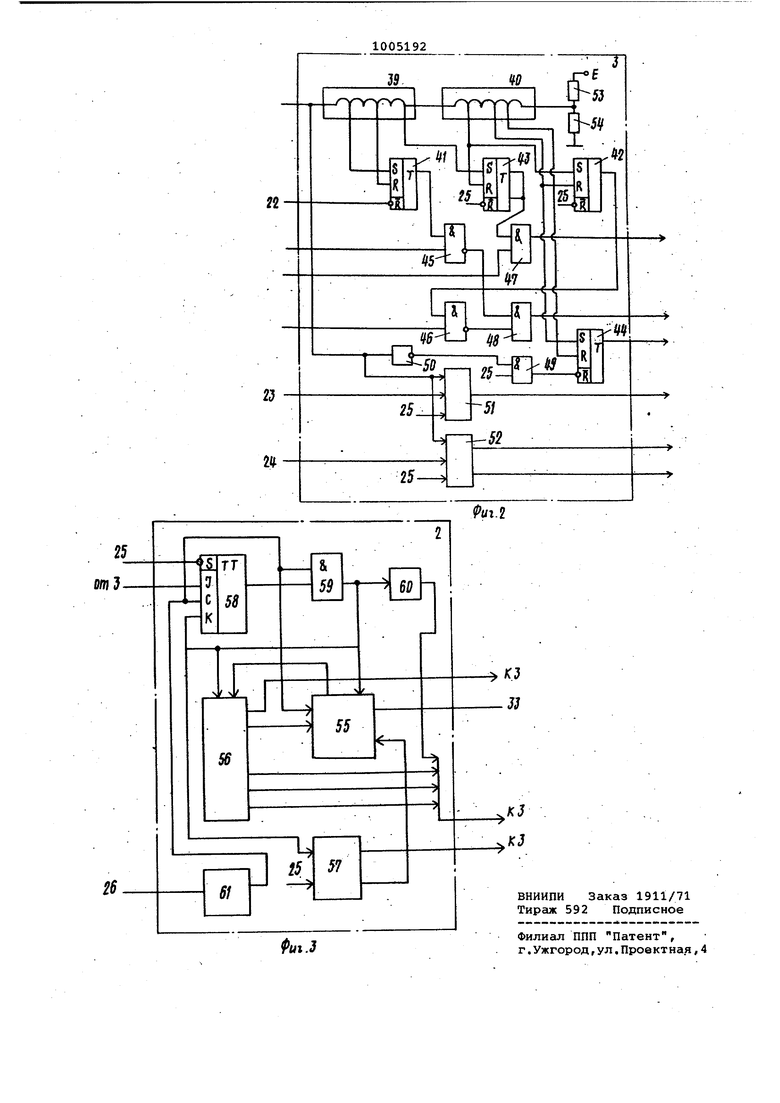

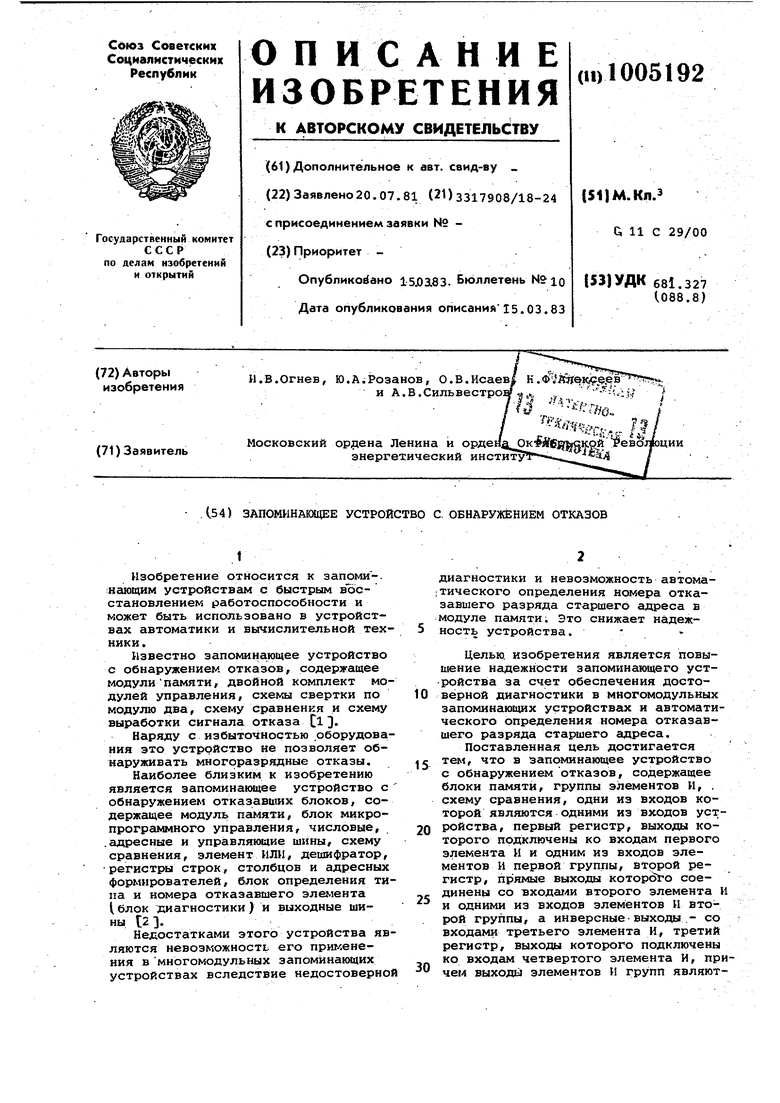

На фиг. 1 схематически изображено запоминающее устройство ; на фиг. 2 - блок местного управления ; на фиг. 3 - формирователь тестовых сигналов.

-. Запоминающее устройство содержит (,фиг. 1) п-разрядные блоки 1 памя ги, чзрганизованные в матрицу, состоящую из 1 строк и j столбцов, формирователь 2 тестовых сигналов, блок 3 местного управления, первую 4, вторую 5 и третью б группы элеметов И, мультиплексор 7,. схему 8 сранения, группы элементов ИЛИ 9-, i разрядный первый регистр l6,j -, разрядный второй регистр 11, 10, j-разрядный второй регистр 11/ N-разрядный третий регистр 12 (где N - количество слов в блоке 1 памяти), первый 13, второй 14, третий 15 и четвертый элементы И 16, дешифратор 17, элемент НЕ 18, пятый элемент И 19, элемент ИЛИ 20, труппу элементов НЕ 21, входы 22-28 и выходы 29-38.

Блок 3 местного управления содержит (фиг. 2) элементы 39, 40 задержки, первый 41, второй 42, третий 43 и четвертый 44 триггеры, первый 45 и второй 46 элементы И-НЕ, первый 47, второй 48 и третий 49 дополнительные элементы И, дополнительный элемент НЕ 50, регистр 51 числа, регистр 52 адреса, делитель на резисторах 53 и 54.

Формирователь 2 тестовых сигналов (фиг. 3) содержит блок 55 микропрограммного управления, постоянный накопитель 56, счетчик 57 адреса, пятый триггер 58, четвертый дополнительный элемент И 59, дополнительный элемент 60 задержки и генератор 61 синхроимпульсов.

Устройство работает в двух режимах .

В рабочем режиме в цикле записи по сигналам Обращение и Запись, поступающим на вход 22, блок 3 вырабатывает сигнал Запись, обеспечивает прием информации и адреса на регистры 51 и 52 из процессора и Их выдачу на соответствующие входы блоков 1..

В цикле считывания по сигналам Обращение и Считыв.ание блок 3 вырабатывает сигнал Строб считывания, обеспечивает прием адреса на регистр 52 из процессора и его выдачу на адресные входы блоков 1 памяти. Считанное слово через мультиплексор 7 выдается на выход 29 устройства. .

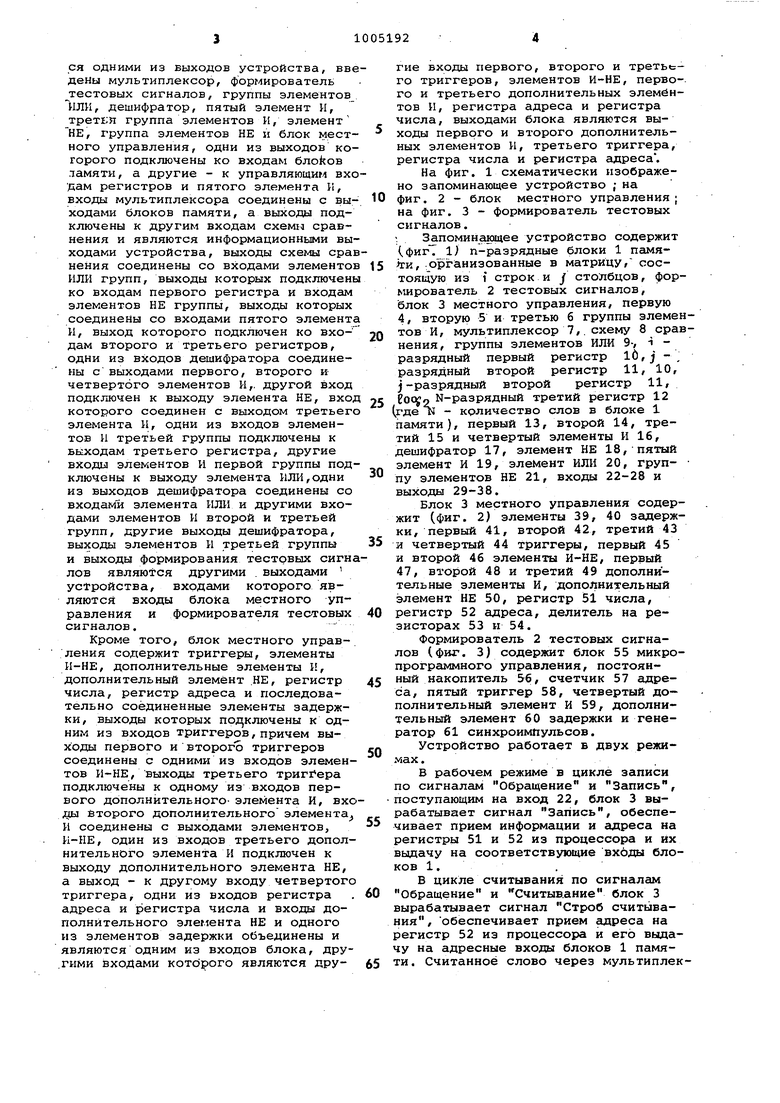

В режиме диагностирования в устг ройстве.проводится циклическая перезапись и считывание по всем адресам .набора тестовьох слов; пример которых для разрядности.слова, равной 8, приведен в табл. 1.

,Таблица

Разряды

Обозначение

тестового О j1 I 2 1 3 1 4 I 5 i6 1 7 ..LL.lJ-L-Li-

11001100 01 100 1 1 0

1 0 1 1 001 1

Тип цикла (запись или считывание), адрес и набор тестовых слов задаются формирователем 2. Количество тестовых слов должно быть не менее трех для определения отказов адресных шин, так как в этом случае по адресам, кратным 2, записываются разные тест-слова.

В каждом такте работы устройства осуществляется запись и считывание последовательности тестовых слов, причем в-каждом последующем такте осуществляется запись тестовой последовательности, циклически СДБИнутой на один адрес до достижения первоначального положения. Алгоритм работы устройства при количестве адресов, равном 8 иллюстрируется таблицей 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Запоминающее устройство с само-КОНТРОлЕМ | 1979 |

|

SU834771A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

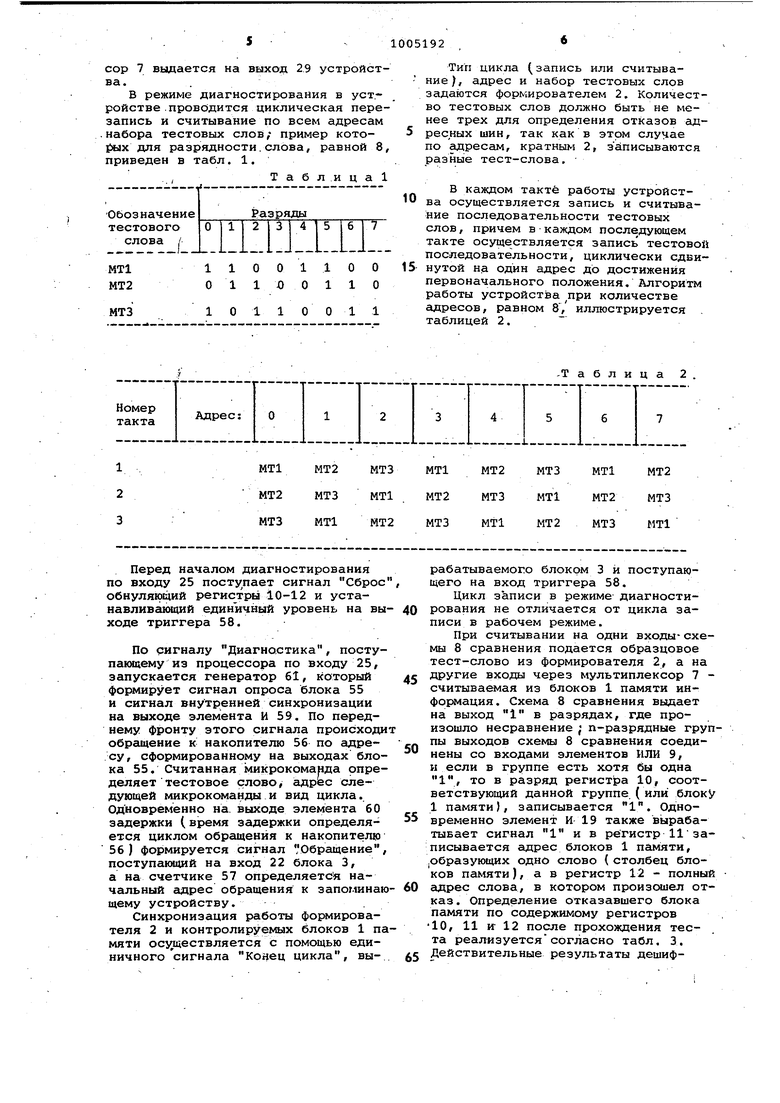

Перед началом диагностирования по входу 25 поступает сигнал Сброс обнуляющий регистры 10-12 и устанавливающий единичный уровень на вы ходе триггера 58. По сигналу Диагностика, поступающему из процессора по входу 25, запускается генератор 61, который формирует сигнал опроса блока 55 и сигнал внутренней синхронизации на выходе элемента И 59. По переднему фронту этого сигнала происходи обращение к накопителю 56 по адресу, сформированному на выходах блока 55. Считанная микрокоманда определяет тестовое слово, адрес следующей микрокоманды и вид цикла. Одновременно на. выходе элемента 60 задержки (время задержки определяется циклом обращения к накопителю 56) формируется сигнал Обращение поступакиций на вход 22 блока 3, а на счетчике 57 определяется начальный сщрес обращения к запоминаю щему устройству.. Синхронизация работы формирователя 2 и контролируе11влх блоков 1 п мяти осуществляется с помощью единичного сигнала Конец цикла, вы-Таблица 2 рабатываемого блоком 3 и поступающего на вход триггера 58. Цикл записи в режиме- диагностирования не отличается от цикла записи в рабочем режиме. При считывании на одни входы-схемы 8 сравнения подается образцовое тест-слово из формирователя 2, а на другие входы через мультиплексор 7 считываемая из блоков 1 памяти информация. Схема 8 сравнения выдает на выход 1 в разрядах, где произошло несравнение ; п-разрядные группы выходов схемы 8 сравнения соединены со входами элементов ИЛИ 9, и если в группе есть хотя бы одна 1, то в разряд регистра 10, соответствующий данной группе, ( или блоку 1 памяти), записывается 1. Одновременно элемент И 19 также вырабатывает сигнал 1 и в регистр 11записывается адрес блоков 1 пам;яти, .образующих одно слово (столбец блоков памяти), а в регистр 12 - полный адрес слова, в котором произошел отказ . Определение отказавшего блока памяти по содержимому регистров 10, 11 и 12 после прохождения теста реализуетсясогласно табл. 3. Действительные результаты дешифрации на выходах 30-32, 34-38 идентифицируются сигналом Конец диагЕсть нули Все единицы

Все единицы Есть нули

Все единицы В табл. 3 указаны значения прямых выходов соответствующих регистров, в каждой строке задаются условия, которые должны выполняться одновременно. Содержимое регистров анализируется на элементах И 13-16 с последующей дешифрацией дешифратором 17 в соответствии с табл. 3. Если а устройстве не обнаружено неисправностей, то все инверсные выходы эегистра 11 равны , и элеменз: И 15 через элемент НЕ 18 выдает запрет на дешифратор 17, обеспечивая нулевое состояние всех выходов. При отказе блоков 1 памяти возбу дается выход 34, сигнал 1 на этом выходе разрешает выдачу содержимцго регистра 10 и регистра 11, составля ющих номер отказавших блоков 1, через элементы И 4, 5 на выходы 32,31 При возникновении неисправнс5сти в блоке 3 на одних адресных выходах в.озбуждается выход 37 устройства и содержимое регистра 12, определяющее номер отказавшего выхода через элементы И б, выдается на выход 30 ; на других адресных выходах возбуждается выход 35 ; на информационных выходах возбуждается выход 36 устройства и содержимое регистра 10 через элементы И 4 выдается на выход 32, определяя номер отказавшего разряда j на выходах управления блока 3 возбуждается выход 38 устройства. При исправном состоянии запоминающего устройства все выходы устностики, вырабатываемым формирователем 2 на выходе 33.

Таблица 3

Есть нули

Безразлично

Есть нули

Все единицы

Есть нули

Безразлично

Безразлично

Все единицы

Все единицы

Все единицы ройства находятся в состоянии логи- ческого О. Таким образом, предлагаемое уст-, ройство по сравнению с прототипом позволяет обеспечить достоверную диагностику в многомодульных запоминающ;их устройствах и автоматическое определение отказавшего разряда старшего адреса, без увеличения времени диагностирования, при этом объем оборудования, обеспечивающего локализацию неисправностей в запоминающем устройстве, сокращается: например, для разрядности слова 32 и экономия составит 21 корпус микросхем серии К 155. Экономический эффект от внедрения предлагаемого устройства определяется уменьшением стоимости ремонта многомодульных запоминающих устройств за счет автоматизации процесса их диагностирования. Формула изобретения 1. Запоминающее устройство с обнаружением отказов, содержащее памяти,группы элементов И, схему сравнения, одни из входов которой являются одними из входов устройства, первый регистр,выходы которого подключены ко входам первого элемента И и одним из входов элементов И первой группы, второй регистр, прямые выходы которого соединены со входами второго элемента И

и одними из входов элементов и второй группы,, а инверсные выходы - со входами третьего элемента И, третий . регистр, выходы которого подключены ко входам четвертого элемента И, причем выходы элементов И групп являются одними из выходов устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены мультиплексор, формирователь тестовых сигналов, группы элементов ИЛИ, дешифратор, пятый элемент И, третья группа элементов И, элемент НЕ, группа элементов НЕ и блок местного управления, одни из выходов которого подключены ко входам блоков памяти, а другие к управляющим входам регистров и пятого элемента И, входы мультиплексора соединены с выходами блоков памяти, а выходы подключены к другим входам схемы сравнения и являются информационнь 1и выходами устройства, выходы схемы сравнения соединены со входами элементов ИЛИ групп, выходы которых подключены ко входам первого регистра и входам элементов НЕ группы, выходы которых соединены со входами пятого элемента И, выход которого подключен ко входам второго и третьего регистров, одни КЗ входов дешифратора соединены с выходами первого, второго и четвертого элементов И, другой вход подключен к выходу элемента НЕ, вход которого соединен с выходом третьего элемента И, одни из входов элементов И третьей группы подключены к выходам третьего регистра, другие входы элементов И первой группы подключены к выходу Элемента ИЛИ, одни из выходов дешифратора соединены со входами элемента ИЛИ к другими входами элементов И и второй и третьей групп другие выходы дешифратора, выходы элементов И третьей группы и выходы

формирователя тестовых сигналов являются другими выходами устройства, входами которого являются входы блока местного управления и формирователя тестовых сигналов.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1983-03-15—Публикация

1981-07-20—Подача