Изобретение относится к технике автематического регупирювания и управления, в частности к астатическим системам автоматического регулирования, может быть использовано, например, в устройствах автоматического регулирования технологических процессов, в устройствах позкционкровйния cTaisKoB с програк мным управлением, в прецеаионных координатографах, в которых выходной сигнал датчика регулируемого параметра представлен в частотно-импульсной форме. Известны следящие системы уттравл© ния перилещением, имеющие компаратор скорости подачи, сравнивающий частотны сигнал, пропорциональный ошибке системы с программируемой частотой. Следящая система содержит программный блок, командный регистр, фиксирующий требуемое значение положения подвижного объекта, и блок программируемой частоты, подкЛоченные к программному блоку, регист фиксирующий величину перемвцения, компаратор кодов командного регистра и регистра, фиксирукядего величину перемещения, генератор частоты, пропорциональный ощибке, получаемой в компарагоре кодов, частотный селектор, подключенный к последовательно соединенным исполнительному устройству и датчику регулируемого параметра, соединенному с регистром фиксации величины перемещения. Данное устройство имеет недостаточную точность регулирования. Из известных устройств наиболее близким по технической сущности и достигаемому результату является цифровая следящая система регулирования, содержащая программный блок, датчик регулируемого параметра, первые выходы которьос подключены к входам элемента несовпаденияг последовательно соединенные первый эл&мейт ИЛИ и элемент задерлоси, первый интегратор, счетный вход которого подключен к выходу элемента задержки, элемент вьщеления нулевого значения первого интегратора, подключенный к вьосодам разрядов этого интегратора, блок выбора направления счетных импульсов, блок установки знака первого интегратора, первый и второй элементы совпадения, соединенные первыми входами соответствен Но с первыми и вторыми выходами блока выбора направления счетных импульсов, вторыми - С выходом; элемента вьщеленйя нулевого значения первого интеграто ра, а выходы первого и второго элемента совпадения соединены cdofёётстеенйо с первым и вторым входом блока установки знака первого интегратора, генератор импульсов, соединенный со счетчиком импульсов, каждый разряд которого подключен к вторрму элементу ИЛИ через элемент И, второй вход которого подключен к соо ветствующим вьгжодам ipaajemoB первого интегратора, второй ин тегратор, подключенный через исполйй- тельное устройство-к датчику регулируем го параметра.Известная цифровая сЛ(ёдящаясйЬтема регул1фОвашя имеет ограниченную област применения. Такйя система работает с частотными сигналами, знак Которых ос. тается неизменным, что йе позболйет использовать ciicTeJwty регулирования в качестве систем управления пёремёшеяие г, например, прецизионных коор динатографах в станках с программным управлением. В этой систетле одинаковые состоздяюяей управлякяцего сигнала, соответствующей интегралу отклонения регул1фу« ого п аметра, представляются рааличйьа и кодами, гго приводит при переходе сод жнмого первого интегратора через нулевое згючение к yBienH4eH«K) вре мёнк перехойяого процесса, снижению динамической точности и устойчивости си- с.темы. ;-,. ,.;, - . ., - - ; Кроме того, необходйм&сгь cyJfitMHpo вания позиционных кодов й Шмпб йТвто ро|Ч интезграторов ттребует кспользовашш испОтште;к ном устройстве параллельногх) многозарядного сумматора. Л Цель изофетення - расщирение области применения системь и повышение качества регулирования. Для этого в предлагаемую следящую систему дополнительно введены .третий и четвертый элементы совпадения, элемент в ьаделения нулейОгО значения второгс интегратора, блок выбора режимов и усганоб1Ш ШШ1:Ж Bfopird иететр элемент ИЛИ и блок форШ|: В(9ния счетных импульсов, первый и второй взводы )1юго поЫлйчЙны к вШ1аШй

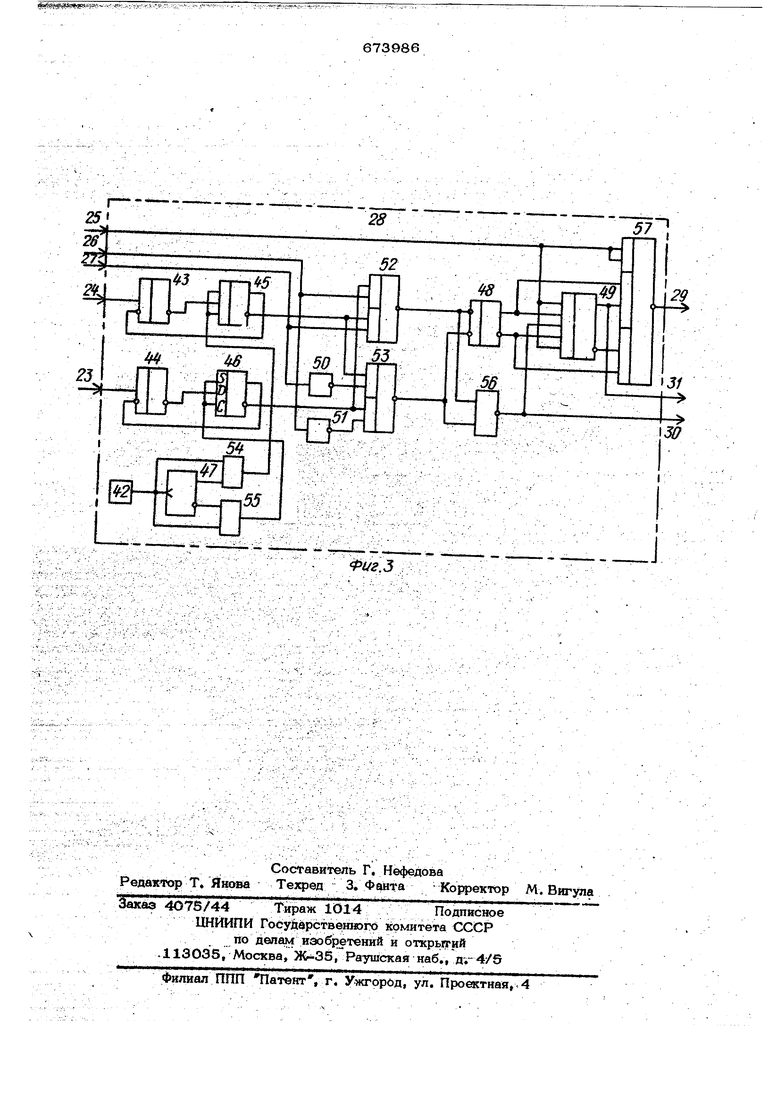

673986 элемента несовпадения, третий и четвертый - к дополнительньпл (знаковым) выходам программного блока и датчика регулируемого параметра, а два выхода подключены к двум входам блока выбора направления счетных импульсов и двум входам перЕюго элемента ИЛИ, соединенного с третьи си входами первого и второго элементов совпадения, третий элемент ИЛИ подключен первым входом к выходу элемента выделения нулевого значения первого интегратора, а выходом - к управляющему входу первого интегратора, третий ичетв 1фтый элементы совпадения 1т6дключены первыми входами соответст- венво к первому и второму выходам блока выбора направления счетных имгГульсов, вторыми входами - соответственно к первому и второму выходам блока устанрвки знака первого интегратора, а выходами соответственно к второму и третьему входам третьего элемента ИЛИ, первый и второй выходы блока выбора режимов работы и установки знака BTqpoг6 интегратора подключены к управляющему та счетному входам второго интегратора, третий - к исполнительному устройству, а входы - к первому выходу блока выбора направления счетных импульсов, к первому выходу блока установки знака интегратора, к выходам и второго элементов ИЛИ и к выходу элемей а вьщеления нулевого значе ния второго интегратора, подключеш1ого к выходам разрядов второго интегратора. На фиг. 1 приведена функциональная схема предлагаемой следящей систа 1ы регулирования; на фиг. 2 - при щипиальная схйла блока формирования счётных импульсов; на фиг. 3 - принципиальная cxeiMa блока вь1бора режима работьт и устано1вки знака второго интегратора. Цифровая следящая система регулиро- вания {фиг. 1) содержит программный блок 1, датчик 2 регулируемого парамвт ра, элемент несовпадения 3, &IOK 4 фор мирования счетных импульсов, блок 5 выбора направлшия счетных импульсов, элемент ИЛИ б, элементы совпадения 7 и 8, Ьлемёнт задержки 9, интехратчэр 10, элемент ИЛИ II, элемент 12 вьюеления нулевого значения интегратора 10, элементы совпадения 13 и 14, блок 15 установки ;энака интегратора 1О, 16 импульсов, счетчик 17, элемент ИЛИ 18, элемент И 19, исполнительное устрой ство 20, интегратор 21, элемент 22 вы- деления нулевого значения интегратора 21, входы 23-27 блока 28 выбора режима работы и установки знака интегратора 21, выходы 29-31 блока 28. Блок 4 формирования счетных импульсов (фиг. 2) содержитинверторы 32 и 33, логические элементы 34 и 35, входы 36-39 и выходы 40 и 41. Блок 28 выбора режима работы и установки знака второго интегратора (фиг.З) включает в себя генератор 42 HMnyjibcpBf триггеры 43-49, инверторы 50 и 51, логические элементы И 54 и 55, элемент ИЛИ 56 и элемент И-ИЛИ 57. Цифровая следящая система регулирования работает следующим образом. Два сигнала, один из которьк соответствует заданному значе тю параметра, фор мируемому программным блоком 1, а дру гой - значению параметра, формируемому .датчиком 2, поступают на оба входа элемента несовпадения И, при помощи которого исключается совпадение импульсов, прищедщих в одинаковой фазе. Далее обе импульсные последовательности, а таюхе знаки импульсных последовательностей поступают на входы 37, 38, 36 и 39 блока 4 формирования счетных импульсов Если знаки последовательностей 1шп:ульсов программного блока 1 и датчика 2 олииаковы, то блок 4 формирует импульсы, которые присутствуют на обоиос выходах 4О и 41. Бел знаки различны, то блок 4 форирует импульсы, которые присутствуют только на одном, из вькодов 4О или 41. Обе импульснью последовательности, получающиеся на выходах 40 к 41 блока 4, при помощи элемента ИЛИ 6 совмещаются в единую последовательность импуш сов Знак выходных импульсов определяет блок 5 выбора направления счетных импульсов. Счетные импульсы элемента ИЛИ 6 через 3 Швржки 9 поступают на вход интегратора 1О и зацисьгеаются п ним. Режим работы интегратора 1О опредепяет выждной сигнал элемента ИЛИ Ц. Режим работы интегратора 10 опредепяется не только выходным сигналом блока выбора направления счетных импульсов, но и сигналами блока 15 установки знака HHt|rpatx)pa 10 И элемента 12 вьщелеиия нулевого значения первого интегратора. В таблице приведены режимы работы интегратора Ю в зависимости от знаков сигналов блоков 5 и 15 и значения содержимого интегратора Ю.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ РЕГУЛЯТОР | 1971 |

|

SU318017A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Цифровая следящая система управленияпЕРЕМЕщЕНиЕМ Об'ЕКТА | 1979 |

|

SU798726A1 |

| Устройство для измерения артериального давления крови | 1985 |

|

SU1426537A1 |

| Программная следящая система | 1981 |

|

SU1108394A1 |

| Дискриминатор временного сдвигадВуХ КОгЕРЕНТНыХ СлучАйНыХ СигНАлОВ | 1979 |

|

SU807314A1 |

| Следящий привод | 1982 |

|

SU1166055A1 |

| Измеритель физических величин | 1984 |

|

SU1234760A1 |

| Устройство регулирования и стабилизации мощности | 1987 |

|

SU1578703A1 |

| Система регулирования частоты вращения судовой турбины | 1981 |

|

SU964198A1 |

В цифровом интеграторе 10 производится алгебраическое j суммирование входных импульсов с числом соответс-рв кяяим интегралу рассогласования (ошиб1:и).

В момент перехода содержимого йнTerpatopa 10 через нуль режим вычитание интегратора 10 изменяется на режим суммирование.

Величина Интетрапа рассогласоваиня всегда представлена в прямом пб&яийон- ном коде. Знак интетрала рассогласования (ошибки) регистрирует блок усташ вки знака интегратора Ю. Значение оцшбки преобразуется генератором 16, счетчиком 17 и элементами И 19 и ИЛИ 18 в последовательность импульсов с частотой, пропорциональной ошибке. Так как

одинаковые, но различные по знаку значения ошибок представлены одинаковым прямым позиционным кодом, то значения частоты, пропорциональные этим ощибкам, одинаковы.

Частотные последовательности: импуль сов с выхода элементов ИЛИ 18 и 6, а также знаки частотных последовательностей с выходов блоков 15 и 5 поступают в блок 28 выбора режима работы и установки знака интегратЪра 21. Блок 28 производит алгефаичёскоё суммирование частотных импульсных последовательносте элементов 6 и 18 с помощью логических элементов 52, 53. Так как импульсные последовательности элементов 6 и 18 несинхронны, то блок 28 при помощи двух синхронизаторов, вьшолненных на триггерах 43, 45 и 44, 46, а также им . пульснего генератора 42, счетгюго триггера 47 и схем И 54 и 55 производит временную привязку импульсов элементо 6 и 18 к с/даинутым на полпер юда импульсам, формируемым элементами 54 и 55, что необходимо для исключения сбоя в работе интегратора 21. Импульсы элементов 52 и 53 поступают на логический элемент ИЛИ 56, гд происходит их суммирование, а также на триггер 48, в котором определяется зна направления импульсов, поступающих через элемент ИЛИ 56 на вход второгх ин тегратора. Производя далее интегрирование этого сигнала вторым интегратором 21, получают на его выходе регулирующее воздействие у , равное сумме двух составляющих у, и у, , пропорцискальных интегралу и двойному интегралу отклонения регулируемого параметра, У f(iMt+ k,|5c(t) dt. Меняя частоту импульсного ген атора 16, можно изменять модуль составляющей регулируемого воздействия у Режим работы интегратора 21 (Ю) определяется в зависимости от состояния триггеров 48 и 49, формирующих с игналы в ыбора нйправления счетных импульсов и установки знака интегратора 21, а также значения содержимого его разрядов. Он может быть определен ,как для интегратора 10 из приведенной таблицы. Знак регулирующего воздействия у с триггера 49 поступает в исполнительное устройство 5О. В установившемся режиме (t)dt.dt, так как x(t) б и Jx (i) dt О , т.е. 3 а время переходного процесса происходит полная компенсация всех ошибок. Благодаря тому, 4to дйя одинаковы: : по величине, но различ1Ь 1х по знаку ошибок рассогласования величина интеграла рассогласования всегда представляется одним и тем же прямым дозиционным кодом, происходит линейное иа енение сигнала управления, что уменьшает перер гуэтирование и время переходного процесса в системе. Возможнс(сть работы со знакопеременными частотными сигналами датчика регу лируемого параметра и программного биока существенно расширяет область прим&8нения предлагаемой следящей системы регулирования. Формула изобретения Ци4ровая следящая система регулиро- вания, содержащая программный блок, датчик регулируемого параметра, первые выходы которых подключ ены к входам элемента несовпадения, последовательно со&диненные первый элемент ИЛИ и элемент задержк, первый интегратор, счетный вход которого подключен к выходу элемента задержки, элемент вьщеления нулевого значения первого интегратора, подключенный к выходам этого интегратора, блок выбора направления счетных импульсов, блок установки знака первого интегратора, первый и второй элементьг совпадения, соединенные входами соответственно с первыми и вторь1ми выходами блока выбора направления счетных импульсов, вторыми - с выходом элемента вьщеления нулевого значения первого интегратора, а выжды первого и второго элемента совпадения соединены соответственно с первым и вторым входом блока установки знака первого интегратора, генератор импульсов, соединенный со счетчиком импульсов, каждый разряд которого подключен к второму элементу ИЛИ через элемент И, второй вход которого подключен к соответствующим выходам разрядов первого интегратора, второй интегратор, подключенный через исполнительное устройство к датчику регулируемого параметра, отличающаяся тем, что, с целью расширения области применения и повышения качества регулирования, она содерхсит третий и четвертый элементы совпадения, элемент вьщеления нулевого значения второго интегратора, блок выбора режимов работы и установки знака второго интегратора, третий элемент ИДИ и блок формирования счетных импульсов, первый и второй входы которого подключены к выходам элемента несовпадения, третий и четвертый - к дополнительным (знаковым) выходам программного бпока и датчика регулируемого параметра , а два выхода подключены к двум входам блока выбора направления счетных импульсов и двум входам первого элемента ИЛИ, соединенного с третьими входами первого и второго элементов совпадения, третий элемент ИЛИ подключен первым входом к выходу элемента выделения нулевого значения первого

интегратора, a выходом - к управляющему входу первого интегратора, третий и четвертый элементы совпадения, подключены первыми входами соответственно к первому и второму выходам блока выбора направлени Я счетных импульсов, вторыми входами - соответственно .к первому и второму выходам блока установки знака первого интегратора, а выходами собтветственнэ к второму и третье {у входам третьего элемента ИЛИ,, первый и второй выходы блока выбора режимов работы и

673986

установки знака ёГербгб интегра тора пой- ключены к управляющему и счетному входам второго HHTerpatopa, третий выход к исполнительному устройству, а входы к первому выходу блока выбора направления счетных ймпуЛБСов, к пербому выходу блока установки первого интегратора, к выходам первого и второго элементов ИЛИ, и к выходу элемента вьшеления нулевого значения второго интетт атора, подключенного к вьЬсодам разрядов второго интегратора.

Фиг.З

Авторы

Даты

1979-07-15—Публикация

1976-12-20—Подача