Изобретение относится к устройствам авто-матического цифрового регулирования, в частности к астатическим регуляторам, применяемым в системах автоматического регулирования технологических процессов, например, для непрерывного смещения.

Известны цифровые регуляторы, содержащие программное устройство и датчик регулируемого параметра через элемент несовпадения, элемент «ИЛИ и элемент временной задержки, соединенные с интегратором, подключенным ,к цифровому исполнительному устройству и к блоку выбора направления записи импульсов в интегратор.

Предлагаемый регулятор отличается тем, что он содержит второй интегратор, соединенный с исполнительным устройством, блок установки знака первого интегратора, два выхода которого связаны с исполнительным -устройством, элементы «И-НЕ, «И и «ИЛИ, импульсный генератор, соединенный со счетчиком, каждый разряд которого через элемент «И подключен к дополнительному элементу «ИЛИ, связанному со вторым интегратором, Вторые 1ВХОДЫ элемеитов «И подключены .к разрядам первого интегратора таким образом, что старшему разряду счетчика .соответствует младший разряд интегратора, а все разряды интегратора соединены со входом элемента «И-НЕ через два элемента «И, подключенных к схеме установки Знака первого интегратора. При этом вторые входы последних элементов «И связаны с выходами блока выбора направления .записи импульсов iB первый интегратор.

Это повышает динамическую точность ре| гулятора.

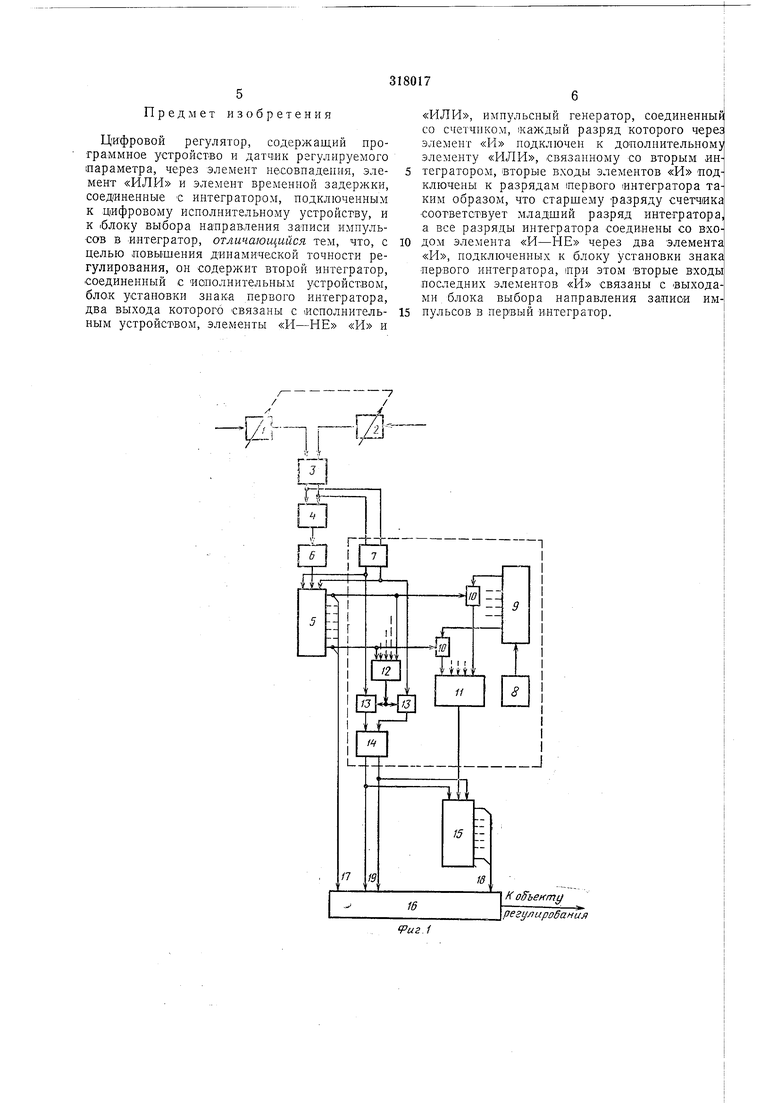

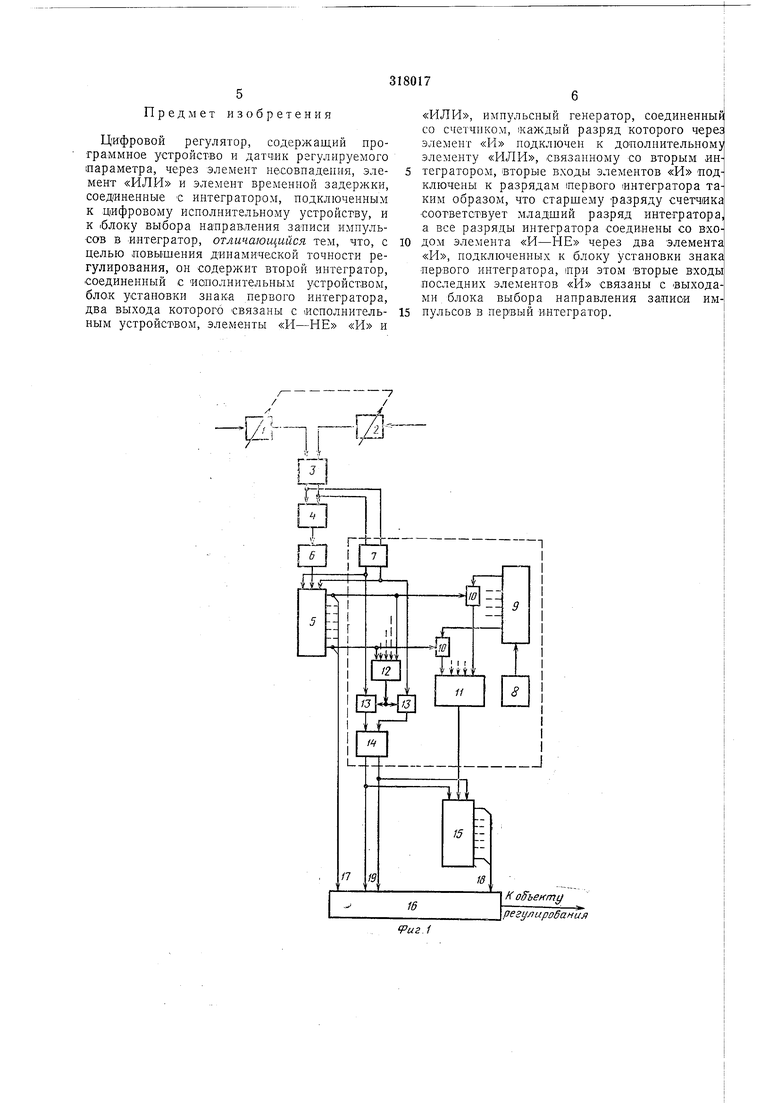

На фиг. 1 приведена функциональная схе| ма предлагаемого регулятора, где обозначе

но: 1-программное устройство; 2 - датчи регулируемого параметра; 3 - элемент несо впадения на два входа, предназначенный дл исключения фазового совпадения импульсо программы и датчика; 4 - логический элг

мент «ИЛИ для совмещения импульсов про граммы и датчика; 5 - первый интегратор формирующий интегральную составляющу регулирующего воздействия;, 5 - элемент вре менной задержки; 7-блок выбора направ

ления записи импульсов в первый интегратор 8 - импульсный генератор; Р -счетчик; 10-логические элементы «И на два входа; 11логический элемент 12 - логически элемент «И-НЕ ; 13 - логические, Схемы

«И на два входа; 14 - блок установки зна ка первого интегратора (одновременно уст, навливающий направление записи второг интегратора); 15 - второй интегратор,, фор мирующий составляющую регулирующег,

тегралу; 16 - цифровое исполнительное усгройство; 17 - ВХОД интегральной составляющей регулирующего воздействия; 18 - вход составляющей регулирующего воздействия, пропорциональной двойному интегралу отклонения (ошибки); 19 - шины устанав ки знака .интегральной составляющей регулирующего воздействия.

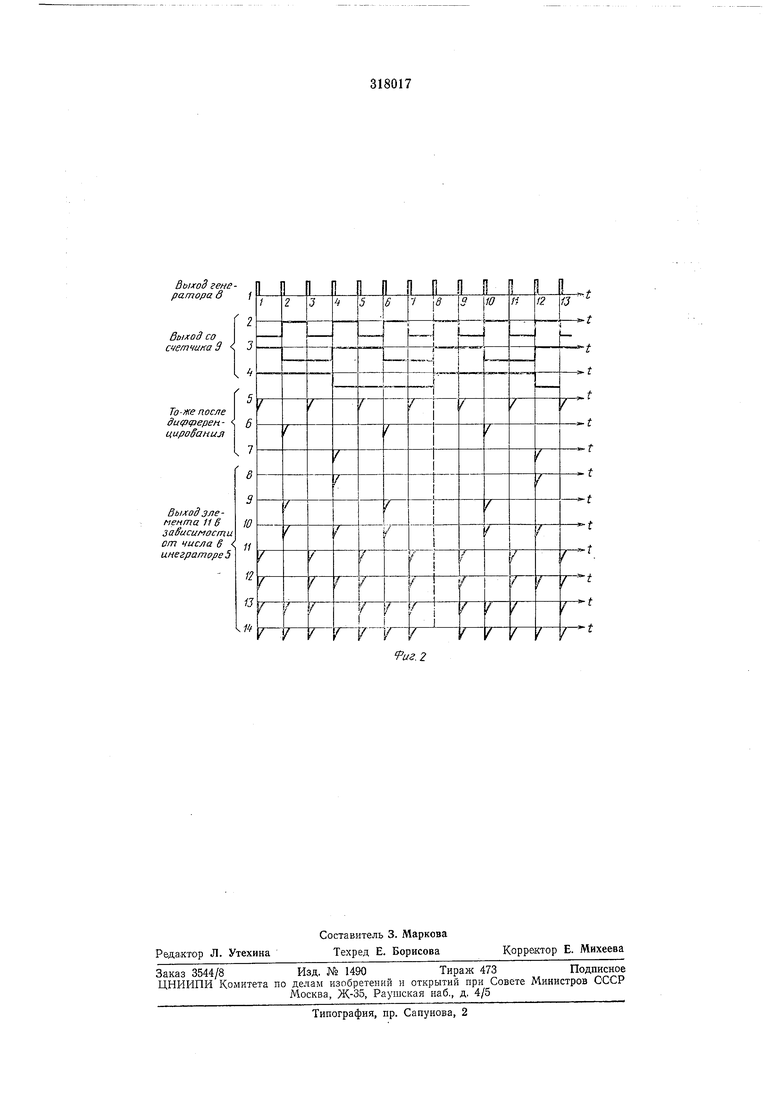

На фиг. 2 приведены диаграммы, поясняющие pa6oty основного узла, состоящего из блоков .

На .выходе этого узла (выход элемента //) получается импульсная последовательность, частота которой прямо пропорциональна величине числа, записываемого первым интегратором 5, т. е. величина интеграла ошибки. Производя далее интегрирование этого сигнала вторым интегратором 15, получим на его выходе соста1вляющую регулирующего воздействия, прямо пропорциональную двойному интегралу ошибки.

Устройство работает следующим образом.

Два сигнала, соответствующие один заданному значению параметра (программа), другой измеренному значению параметра (датчик) , поступают на оба входа элемента несовпадешия 3, с помощью которого исключается совпадение импульсов, прищедших в одинаковой фазе. Импульсы, пришедшие одновременно на оба входа, либо взаимно уничтожаются, либо автоматически сдвигаются. Это необходимо для исключения сбоя в работе первого интегратора. Далее обе импульсные последовательности с помощью элемента «ИЛИ 4 совмещаются в единую последовательность им1пульсов. Причем знак каждого импульса этой последовательности устанавливается с помощью блока выбора направления записи импульсов в первый интегратор 7. Импульсы с элемента 4 через элемент временной задержки 6 поступают на вход интегратора 5 и записываются в нем. Таким образом, подготовка блока выбора направления счета предшествует счету поступающих на вход интегратора им1пульсов, что исключает сбой в работе интегратора и повышает надежность его работы.

В цифровом интеграторе 5 производится суммирование импульсов одного знака и вычитание импульсов другого знака, т. е. выделение интеграла рассогласования (ошибки), величина которого в цифровом позиционном коде подается на вход 17 исполнительного устройства 16 для отработки.

Одновременно импульсы с генератора 8 подаются на вход счетчика 9 и подсчитываются (см. диаграммы на фиг. 2).

На диаграммах приведена работа трехразрядного счетчика 9 и трехразрядного выходного устройст1ва интегратора 5, работающих в двоичном коде.

фронтам перепадов, поступают через элемент «И 10 на вход элемента «ИЛИ //. Элементы «И 10 управляются потенциалами с выходов разрядов интегратора 5, но в обратном порядке. Таким образом, меньшему числу в интеграторе 5 (меньшая ошибка) соответствует больший коэффициент деления счетчика 9 и меньшая частота на выходе элемента // и наоборот большему числу -большая

частота на выходе элемента 11. Причем, как видно из диаграмм 8-14, эта зависимость прямо пропорциональна. Числоимпульсная последовательность с вьгхода элемента 11 поступает на вход интзгратора 15, в .котором

производится их суммирование. Величина получаемой суммы (числа в интеграторе /5) прямо пропорциональна двойному .интегралу отклонения (оши|бки). Меняя частоту генератора 8 можно изменять модуль этого числа,

т. е. устанавливать коэффициент пропорциональности (/Ci) составляющей регулир.ующего воздействия, пропорциональной двойному интегралу отклонения, величина которого в цифровом позиционном коде подается на

вход 18 исполнительного устройства 16 для отработки.

Выходы всех ра13рядов интегратора 5 подключены к элементу «И-НЕ 12, выход с которого управляет двумя логическими схемами «И 13, через которые сигналы с блока 7 поступают на бло.к 14.

Элемент 12 срабатывает только при .нулевом числе в интеграторе 5. В этом случае (при совпадении всех нулей на входах элемента совпадения 12) выдается сигнал «разрешения обоим схемам 13. Поэтому в зависимости от знака первого поступившего импульса блок 7 устанавливает направление записи этого импульса в первом интегратора

и направление записи во втором интеграторе с помощью блока 14. Поскольку потенциалы на выходе блока 14 меняются только в момент перехода числа в интеграторе через нуль, то они характеризуют собой знак этих

чисел. Сигнал, поступающий по шинам 19 в исполнительное устройство 16, устанавливает знак интегральной составляющей регулирующего воздействия (с первого интегратора). Таким образом, общее регулирующее воздействие, поступающее .на цифровое исполнительное устройство, равно сумме двух составляющих

y y,-{.y k x((}dt + k, l x(f)dtdt,

пропорциональных интегралу и двойному интегралу отклонения регулируемого параметра. При наличии замкнутой обратной связи в установившемся режиме

,x(t)dfdt,

Предмет изобретения

Цифровой регулятор, содержащий программное устройство и датчик регулируемого параметра, через элемент несовпадения, элемент «ИЛИ и элемент временной задержки, соединенные с интегратором, нодключенным к цифровому исполнительному устройству, и к блоку выбора направления записи импульсов в интегратор, отличающийся тем, что, с целью повышения дина лической точности регулирования, он содержит второй интегратор, соединенный с исполнительным устройством, бло.к установки знака первого интегратора, два выхода которого связаны с .исполнительным устройством, элементы «И-НЕ «И и

«ИЛИ, импульсный генератор, соединенный со счетчиком, каждый разряд которого через элемент «И подключен к дополнительному элементу «Р1ЛИ, связанному со вторым интегратором, 1вторые входы элементов «И подключены к разрядам первого интегратора таким образом, что старшему разряду счетчика соответствует младший разряд интегратора, а все разряды интегратора соединены со входом элемента «И-НЕ через два элемента «И, подключенных к блоку установки знака первого интегратора, при этом вторые входы последних элементов «И связаны с выходами блока выбора направления записи импульсов в первый интегратор.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая следящая система регулирования | 1976 |

|

SU673986A1 |

| Устройство для программного управления | 1976 |

|

SU566241A1 |

| Автоматический регулятор возбуждения для синхронной машины | 1981 |

|

SU1020954A1 |

| Цифровая система управления | 1984 |

|

SU1234811A1 |

| Устройство для регулирования расходажидКОСТи | 1979 |

|

SU842728A1 |

| Цифровая следящая система управленияпЕРЕМЕщЕНиЕМ Об'ЕКТА | 1979 |

|

SU798726A1 |

| Реверсивный цифро-аналоговый интегратор-преобразователь | 1984 |

|

SU1247833A1 |

| Устройство для измерения тока | 1984 |

|

SU1255944A1 |

| Устройство для регулирования расходов компонентов при смешении | 1977 |

|

SU696422A1 |

| Цифровой следящий привод | 1983 |

|

SU1151925A1 |

регулиробания

ВыхоЗ генератора в

Вшход со с тчина 9

То-же после дисрдзеренциро§анил

Выход элемента а 6 зависимости от числа 6 инегратрреЗ

Авторы

Даты

1971-01-01—Публикация