йены через элемент И с выходом старшего разряда, а выходы элементов ИЛИНЕ каждого последующего разряда и первых элементов ИЛИ-НЕ триггеров тех же разрядов соединены через элементы И с выходными шинами {эегистра для аналого-цифрового преобразователя поразрядного уравновешивания f 2.

Недостатком устройства является малое быстродействие и неустойчивость в Ьаботе, вызванное ограничениями, накладываемыми на цифроаналоговые преобразователи (время срабатывания цифроаналогового преобразователя должно быть значительно меньше времени рассасывани неосновных носителей транзисторов регисра).

Целью изобретения является повышени быстродействия и упрощение схемьи

Указанная цель достигается тем, что регистр для аналого-цифрового преобразователя поразрядного уравновешивания, содержащий разряды, первый вход каждого из которых, кроме первого разряда, соединен с первым выходом предыдущего раз ряда, второй вход - со вторым выходом последующего разряда, третий вход - с первой шиной, четвертый вход - с соотЬетствующей тактовой шиной, содержит

Д-триггер и элемент 2И, первый вход ко торого соединен с инверсным выходом Д-триггера, второй вход - со второй шиной, выход - со вторым входом последнего разряда регистра, первый вьусод которого соединен со входом Д-триггера, примем первый вход первого разряда соединен с его вторым выходом. Каждый разряд регистра содержит R- S триггер на элементах 2ИЛИ-НЕ, прямой выход которого соединен с первым входом элемента ЗИ, инверсный вых.од - с первым . входом первого элемента 2И, вход сбро- са - с выходом второго элемента-21, вход установки - с первым входом разряда, второй вход разряда соединен со вторыми входами элемента ЗИ и первого элемента 2И, третий вход разряда соединен с первым входом второго элемента 2И, второй вход которого соединен с первым выходом разряда и с выходом элемен та ЗИ, третий вход которого соединен с четвертым входом разряда, второй выход разряда соединен с выходом первого элемента 2И.

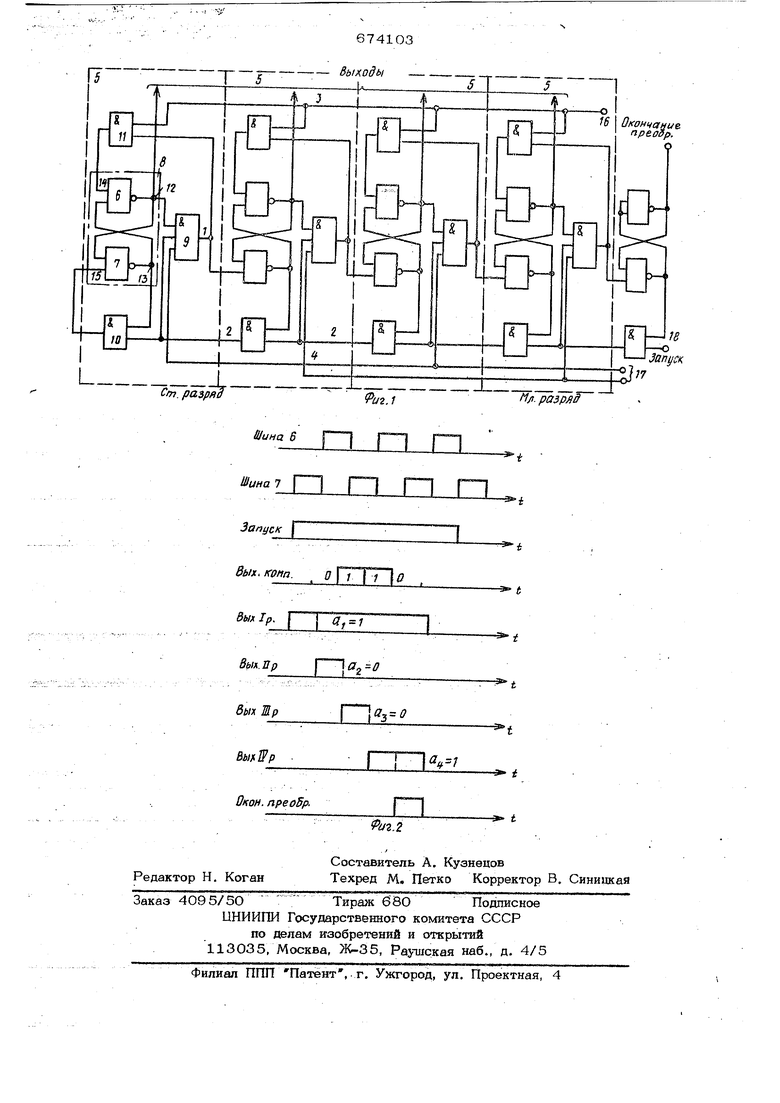

На фиг. 1 представлена схема .регистра; на фиг. 2 - временная диаграмма работы регист эа.

Регистр содержит разряды, каждый из которых имеет четыре входа 1, 2, 3 и 4.

Каждый разряд 5 регистра состоит из двух элементов 2ИЛИ-НЕ 6 и 7, образующих R-S триггер 8, элемента ЗИ 9 и двух элементов 2И 1О и 11. Прямой выход 12 триггера 8 соединен с первым йходом элемента ЗИ 9, а инверсный выход 13 - с первым входом первого элемента 2И 10. Выход второго элемента 2И 11 соединен со входом сброса 14, т. е. с поступлением логической на этот вход на прямом выходе триггера буает логический О. Первый вход 1 разряда соединен со входом установки 15, г. е. с поступлением логической 1 на ктот вход на прямом выходе будет логическая 1. Второй вход разряда 2 соединен со вторыми входами элемента 3 И 9 и первого элемента 2Й 10. Третий вход разряда 3 соединен с первой шиной 16 и первым -ВХОДОМ второго элемента 2И 11, второй вход которого соединен с первым выходом разряда и с выходом элемента ЗИ 9. Третий вход элемента , ЗИ 9 соединен с четвертым входом 4 разряда, соединенным с соответствующей тактовой шиной 17. Второй выход разряда соединен с выходом первого элемента 2И 10.

Устройство работает следующим образом.

В исходном положении триггеры всех разрядов установлены в состояние О, т. е. на прямых выходах логическое О, а на инверсных выходах - логические Независимо от сигнала компаратора (на чертеже не показан) вторые элементы 2И 11 закрыты, (т. е. на выходах логические О), так как один из входов соединен с выходом элементов ЗИ 9, которые закрыты иэ-за наличия сигнала О с прямых выходов 12 триггеров 8. Первые элементы 2И 10 закрыты, так как логическая 1 установлена на одном входе. Это устойчивое положение, в котором регистр может находиться длительное время. Процесс преобразования начинается с сигнала Запуск по второй шине 18 (логическая I, которая поступает нд вход первого элемента 2И 10 с приходом инверсного тактового импульса) В этом случае логическая 1 устанавливается на выходах всех первых элементов 2 И 1О. Логическая 1-е выхода первого элемента 2И 10 старшего разряда устанавливает триггер этого разряда в единичное состояние, остальные триггеры Находятся в О состоянии. Напряжение, соответствующее логической старшего разряда регистра 11щ , сравнивается с измеряемым напряжением l/x . Полагаем, что если U цап- напряжение, поступаемое на компаратор с цифроаналогового преобразователя, то на выходе компаратора логический если и - на выходе логическая Допустим, , я а, - код первого разряда регистра, тогда на выходе компаратора будет сигнал логического О, которьШ должен оставить триггер в состоянии, что соответствует коду а, 1. Поступивший прямой тактовый импульс открывает элемент ЗИ 9 старшего разряда и на его вь1ходе устанавливается логическая , так как на всех входах эле мента логическая , Элементы ЗИ 9 остальных разрядов регистра закрыты, та как триггеры этих разрядов регистра находятся в состоянии О, Логическая с элемента ЗИ 9 старшего, разряда регис ра подается на вход второго элемента 2И 11 этого разряда, тем самым разрешая сигналу с компаратора поступить на вход сброса старшего разряда и на вход установки триггера следующего разряда регистра. Так какITjf , то с компаратора поступает логический О и триггер сохраняет прежнее состояние что соответствует нужному коду а , 1. Логическая 1 с выхода элемента ЗИ 9 устанавливает триггер след ющего разряда регистра состояние, тем самым закрывая элемент ЗИ 9 старшего разряда регистра, так как инверсный выход триггера второго разряда регистра соединен со входом первого элемента 2И Ю, выход которого соединен со входом элемента ЗИ 9 старшего разряда регистра. Остальные разряды регистра остаются в прежнем состоянии, так как они управляются через элементы ЗИ 9, которые находятся в закрытом состоянии из-за наличия на входе логического О, либо с одной из 18 шин тактового импульса, ли бо с прямых выходов триггеров регистра Далее происходит.процесс установки кода во втором разряде и установка в состояние следуюшего разряда. Этот процесс П|годолжается до тех пор, пока не будут опрошены все разряды регистра и на выходах регистра установится код. Одновременно с установкой кода в послед нем младшем разряде регистра происхо дит установка логической на выходе оконечного триггера, который фиксирует окончание преобразования и блокирует по лачу сигнала запуск. Повышение быстродействия регистра осуществляется за счет уменьшения общего времени преобразования, так как в течение одного такта происходит опрос двух разрядов регистра. Общее время преобразования 10 - разрядного аналогоцифрового преобразователя может составлять 1 МКС. Упрощение схемы регистра достигается за счет использования на один разряд регистра R-S триггера, выполненного на элементах 2ИЛИ-НЕ, элемента ЗИ и двух элементов 2И. Формула и зоб ре тения 1.Регистр для аналого-цифрового преобразователя поразрядного уравновешивания, содержащий разряды, первый вход каждого из которых, кроме первого, соединен с первым Вь1хЬДОм предыдущего разряда. Второй вход - со вторым выхоflijM Последующего разряда, третий вход с первой шинсЛ, четвертый вход - с соответствующей тактовой шиной, отличающийся тем, что, с целью повышения быстродействия и упрощения регистра, он содержит Д-триггер и элемент 2И, первый вход которого соединен с инверсным выходом Д-т{жггера, второй вход - со бторой шиной, выход - со вторым входом последнего разряда регистра, первый выход которого соединен со входом Д-триггера, причем первый вход первого разряда соединен с его вторым выходом. 2.Регистр по п. 1, отличающийся тем, что каждый райряд регистра содержит R-S триггер на элементах 2ИЛИ-НЕ, прямой выход которого соединен с первым входом элемента ЗИ, ииверсный выход - с первым входом первого элемента 2И, вход сброса - с выходом второго элемента 2И, вход установки - с первым входом разряда, второй вход разряда соединен со вторыми входами элемента ЗИ и первого элемента 2И, третий вход разряда соединен с первым входом Второго элемента 2И, второй вход которого соединен с первым выходом разряда и с выходом элемента ЗИ, третий вход которого соединен с четвертым входом разряда, второй Ьыход разряда соединен с выходом первого элемента 2И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 444319, кл. Н 03 К, 13/258, 1972. 2.Авторское свидетельство СССР No 443483, кл. И 03к 13/258, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1988 |

|

SU1737731A1 |

| ДИСКРЕТНЫЙ СОГЛАСОВАННЫЙ ФИЛЬТР | 2014 |

|

RU2589404C2 |

| ЯЧЕЙКА ОДНОРОДНОЙ ПРОГРАММНО-УПРАВЛЯЕМОЙ СРЕДЫ | 1997 |

|

RU2132081C1 |

| Умножающий цифроаналоговый преобразователь | 1983 |

|

SU1181150A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Преобразователь напряжение-код сКОНТРОлЕМ | 1979 |

|

SU822342A1 |

| Регистр | 1979 |

|

SU860137A1 |

| Устройство для индицирования текущего времени | 1989 |

|

SU1661719A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

Авторы

Даты

1979-07-15—Публикация

1976-08-16—Подача