(54) РЕГИСТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр последовательного приближения | 1981 |

|

SU1149791A1 |

| Регистр для аналого-цифрового преобразователя поразрядного уравновешивания | 1976 |

|

SU674103A1 |

| Регистр | 1979 |

|

SU822367A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Регистр | 1981 |

|

SU1024989A1 |

| Универсальный сдвиговый регистр | 1985 |

|

SU1295449A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1987 |

|

SU1499496A1 |

| Универсальный сдвиговый регистр | 1986 |

|

SU1339657A1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

| Устройство управления преобразователем аналог-код последовательного приближения | 1979 |

|

SU858206A1 |

Изобретение относится к цифровой вычнспительной технике и предназначено для использования в аналого-цифровых преобразователях, в частности в ингегралыюм исполнении. Известен регистр для аналого-цифровы преобразователей содержащий троичный триггер, выполненный на элементах И ЛИНЕ, и другие логические элементы Ъ Однако этот регистр обладает малым быстродействием (тактовая частота 100 кГц), большей потребляемой мощностью (порядка 1ОО мВт на один разряд), недостаточно устойчив против помех трудно реализуемый в виде инге1Т)альнсяй схемы. Наиболее близким к предлагаемому по технической супвсосги является регистр, выполненный в интегральном исполнении и входящий в состав аналого-цифрового 1феобразователя АД 571. Регистр содержит в каждом разряде RS -триггер, образованный двумя элементами И-НЕ, в гри логических элемента и еще одкн ло- гичеокий элемет т служит для связи с со седним разрядом. Выход первого элемента И-НЕ соединен со входом установки триггера, выход второго элемента И-НЕ со входом сброса триггера. Вход первого элем«1та И-НЕ соединен с шиной тактовых импульсов и с вьсходом третьего блоцкирующего элемента И-НЕ, вход вт(фого элемента И-НЕ соединен с щиной комааратора р.. Недостатком этсА схемы является низкое быс1ройе&сгвие, так как для вьтолнения П -ра;фядаого преофазования неовходимо (п +1) Гбиктов. Б результате при работе регистра в составе 10-разряа ного аналого-цвфрового сфеобразователя время преофазоваявя 25 мкс. Другим к достатк(М4 явпяетса то, чтю один разряд регистра содержит 5 элементов И-НЕ, что увеличивает площадь врвсталаю внтегралы н(з& схемы )-аифровсго тфеобразователя. Цель ваобротевия - повьопенве быЕСТродействиа рехвстра в его утфогаенве.

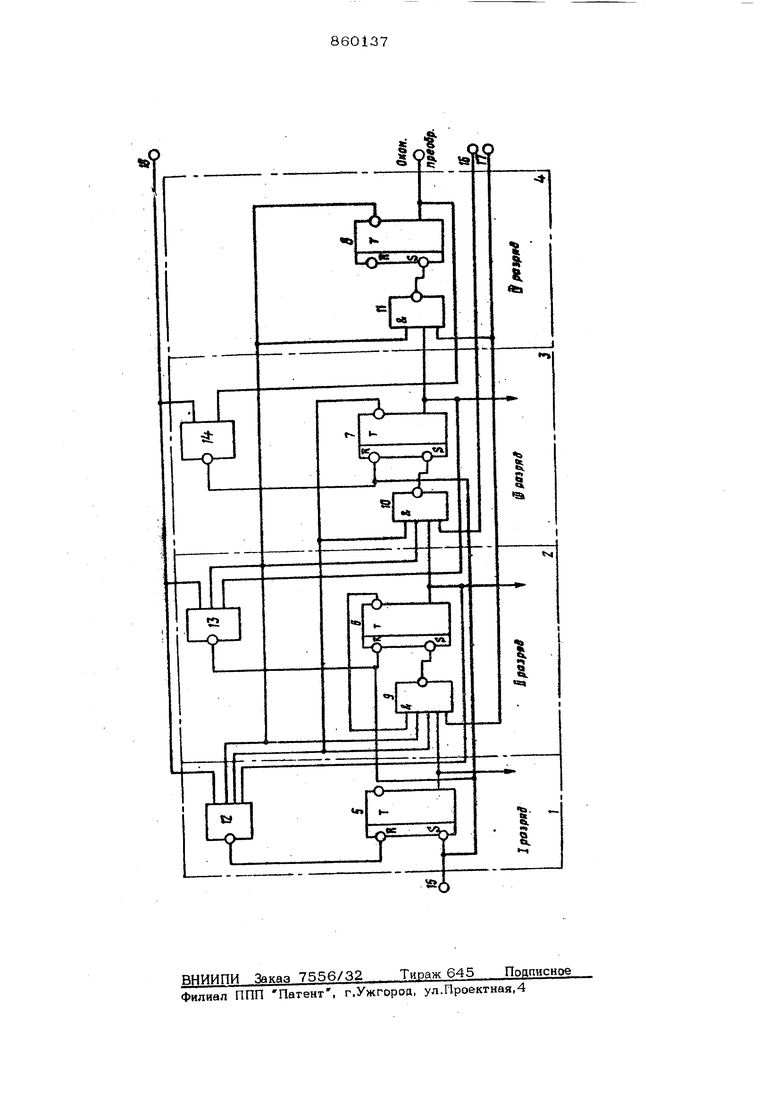

3860137

Поставленная цепь дсх:гигаегся гем, что в регистре, содержащем последователь-но соединенные ячейки памяти, каждая из которых, кроме первой и последней, выпопнена на RS -триггере и двух элементах И НЕ, вькод первого из которых соединен с S -входом R5-триггера, R-вход RS-трнггера каждой ячейки памяти подключен к выходу второго элемента И-НЕ данной ячейки памяти, первый вход элемента И-Н первой ячейки памяти и первые входы вто рых элементов И-НЕ остальных ячеек памяти, кроме последней, подсоединены к ин формацис«ному входу регистра, шину за пуска и тактовые шины, второй вход второго элемента И-НЕ каждой ячейки памяти соединен с прямым выходом Г З-триггера последующей ячейки памяти, (шверсный выход R5-тpиггepa которой подключен к первым входам первых элементов И-НЕ предыдущих нчеек памяти и второму входу элемента И-НЕ первой ячейки памяти, инверсный вьссод RS-триггера после щей ячейки памяти соединен с первым входом элемента И-НЕ данной ячейки памяти, со вторыми входами первых элементов; И-НЕ и с третьими входами вторых элементов И-НЕ остальных ячеек памяти, кроме предпоследней, и с треть входом элемента И-НЕ первой ячейки памяти, первая тактовая шина соединена с третьими входами первых элементов ИНЕ нечетных ячеек памяти, кроме первой, втекая трактовая шина соединена с третьими входами элементов И-НЕ четных ячеек Памяти, шина запуска соединена с -входом RS-тригг.ера первой ячейки памяти и R-входами RS-Tpm repoB остальных ячеек памяти, кроме последней. На чертеже представлена функциональная схема предлагаемого регистра. Регистр содержит ячейки 1-4 памяти (показаны только четыре ячейки памяти регистра), RS-триггеры 5-8, первые элементы И-НЕ 9-11, вторые элементы И-НЕ 12-14, шина 15 запуска, тактовые шины 16 и 17, информационный вход 18 регистра. Регистр функционирует следующим образом. В исходном состоянии триггеры 58 всех йчеек 1-4 памяти находятся в со стоянии О (т.е. на прямых выходах логические О на инверсных - логические I). Управление триггерами 5-8 инверсное, т.е. осуществляется логическим О), фоцесс преобразования начинается с сигнала Запуск ( логический О ), который с приходом прямого тактового импульса на шину 16 устанавливает триггер 5 старшего разряда в состояние 1 (т.е. на прямом выходе - логическая 1, на инверсном выходе - логический ) Остальные триггеры 6-8 - в со сто$гаии О, так как; на 5-ти входах триггеров 6-8 логическая 1. При работе схемы в качестве регист ра в аналого-цифровом ггреобразователе напряжение U - напряжение, поступающее на компаратор с цифро-аналогового преобразователя (не показан), соответствующее логической 1 ячейки 1 памяти (fv. сравнивается с измеряемым нагфя«ением, ЕслиОу о на выходе компаратс эа логическ{й1 О, если -х ицд„ - логическая . Доп устнм, что Ux U 1с-1 ицдп . где q код старшего первого разряда регистра, тогда на выходе компаратора будет сигНал логической 1, который должен сброснть триггер старшего разряда в состояние О, что соответствует коду ., Действительно, с приходом тактового импульса на шину 16 прои лодит установка iRS-триггера с 6 следующего раэряря в состояние 1 (так как на 5-ом этого триггера логический О с выхода элемента И-НЕ 9). На Е -вход тригрера 5 старшего разряда поступает логический О с выхода элемента И-НЕ 12. Он устанавливает триггер 5 в состояние О, что соответствует коду а,,Ог Допустим, Ч1О Ux о( -и |с оУкй -uan, я® Сг - коа второго разряда а . - напряжение ЦАП, соответствующее второму разряду. Тогда в пределах тактового импульса на шине 16 происходит установка ЦАП, а с приходом следующего тактовогч) ямпупьса происходит установка следуюшЕвго третьего разряда в состояние , а второй разряд остается в состоянии 1, что coorBeitn-вует коду Дд 1, Действительно, с «фиходом тактового импульса на шину 16 происходит установка триггера третьего разряда в состояние 1 (так как на«Г входе триггера 7 логический О), . временно с этим происходит блсж фовка элемента И-НВ 12 и элемента И-НЕ 9. На R-входе триггера 6 логическая I, так как с компаратсра на элемент И-НЕ 9 поступает логический О. Он ливает триггер 6 в состоянии I, что соответствует коду CJij 1, Далее с Приходом следующего тактового импульса на щйну 16 происходит установка кода в третьем разряде и установка в состояние 58 григгера 7, фиксирующего окончание преобразования. Таким образом, в течение однсяо такт происходит опрос двух ячеек памяти (разрядов) регистра, что увеличивает быстро- действие. Регистр благодаря предлагаема структуре уменьшает число кс 1понент в увеличивает быстродействие. Несмотря на то, что в предлагаемом регистре элемент И-ЛЕ имеют большее количество входов по сраш{еншо с известным, в интекцисяшо схемотехнике элемент И-НЕ реализуется одним транзистором, а т -входы обьедин ются в один узел. Каждая ячейка памяти регистра, за исключением старшего, содержит 4-е транзистора. Старший ра:фяд содержит 3-4 транзистсра. Повьвцение быстродействия в устройстве осуществляется за счет опроса двух ячеек памяти регистра в одном такте, а упрощение - за счет сокращения числа элементов. формула изобретения Регистр, содержащий последовательно соединенные ячейки памяти, каждая из ко торых, кроме первой и последней, выполнена на R,S-триггере и двух элементах ИНЕ, выход первого из которых соединен с S -входом RS-триггера,R-Bxoa F{S-триггера каждой ячейки памяти подключен к выходу вторсго элемента И-НЕ даннс ячейки памяти, первьЙ.вход элемента ННЕ первой ячейки памяти и первые входы вторых элементов И-НЕ остальных яче7ек памяти, кроме последней, подсоедине{1Ы к информаднежному входу регистра, швну запуска и гактс«ые шины, отличающийся тем, что, с целью повышения быстродействия устройства и его упрощения, в нем второй вход второго элемента И-НЕ каждой ячейки памяти соединен с прямым выходом RS-триггера последующей ячейки памяти, инверсный выход RSTptirrepa которой подключен к первым входам элементов И-НЕ этой ячейки памяти и тфедьшушвх ячеек памятк и второму входу элемента И-НЕ первой ячейки памяти, ннверсыьй выход RS-TpHr последней ячейке памяти соединены с первым входом элемента И-НЕ данной ячейки памяти, со входами первых элем@1тов И-НЕ и с третьими входами вторых элементов И-НЕ остальных .ячеек памяти, предпоследней, в с третьим входом элемента И-НЕ первой ячейки шмяти, первая тактовая шина соединена с третьими входами первых элементов И-41Е нечетных ячеек памяти, кроме первой, втекая тактовая шща соединена с третьими входами элементов И-НЕ четных ячеек памяти, шина запуска соединена с S -входом RS -триггера первой ячейки памяти и R-входами RS-TpHrrepOB осгальных ячеек памяти, кроме последней. Источники информации, принятые во Ш1имание при экспертизе 1. Авторское свидетельство СХЗСР № , кл. Н ОЗ К 13/258, 1974. 2. Tourme of Sot a-Sta-te С 1гсиН5.9с -/«u. 1978, №6. p.738-739 (прототип).

Авторы

Даты

1981-08-30—Публикация

1979-10-05—Подача