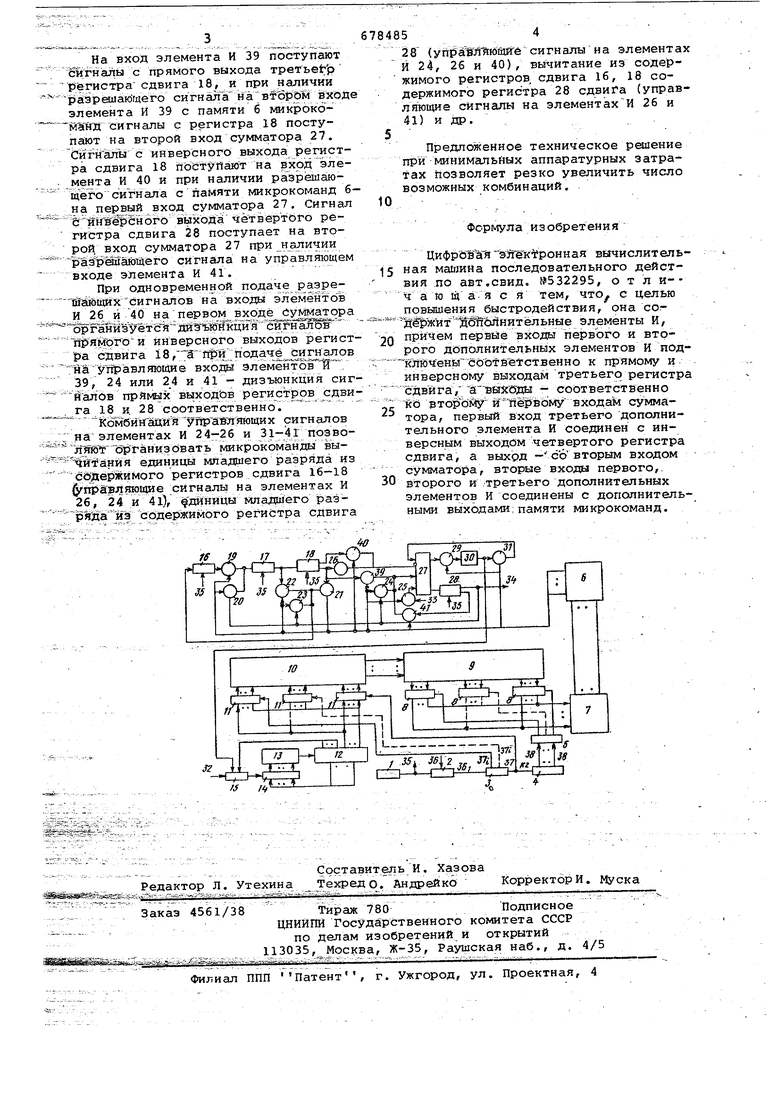

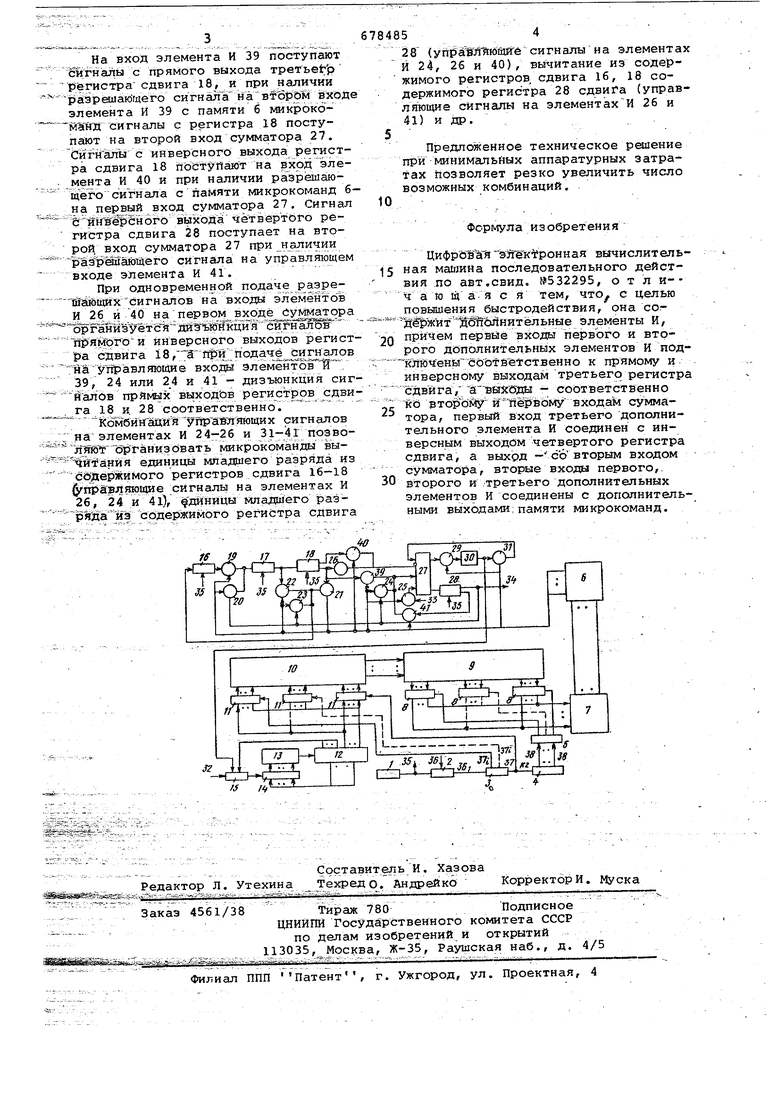

, 1 Изобретение относится к области вычислительной техники. По основному авт.св. № 532295 иэ .вестна цифровая электронная вычисли тельная мапшна последоватёльнбг6 действия, содержащая сумматор, четы ре регистра сдвига, элементы И, три гер, блок памяти команд, блок памяти адресов микрокоманд, память микрокоманд, две группы коммутаторов i гё нератор, три делителя частоты , блок формирования управляющих- сигналов, счётчик адреса команд, блок управле ния счетчиком адреса и дешифраторы кода адреса, адресов микрокоманд и адресов команд. Недостатком такой машины является низкое быстродействие. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что .предложенная машина содержит дополнительные элементы И, причем первые входы первого и второго дополнительных элементов И подключены соответственно к прямому и инверсному выходам третьего регистра сдвига, а выхода - соответственно ко второму и первому входш- сумматора. Первый вход третьего дополнительного элемента И соединен с инверсным выходом четвертого регистра сдвига, а выход - со вторым входом сумматора. Вторые входы первого, второго и третьего дополнительных элемёйтЬв И соединены с допопнительными выходами йамяти микрокоманд. Структурная схема вычислительной машины йр ёйс тавлёна на чертеже где обозначены генератор тактовых сигналов 1, делителя частоты 2-4, устройство управлений синхрбсигнапами 5, память микрокоманд 6, дешифратор адресов микрокоманд 7, коммутаторы 8,блок памяти адресов микрокоманд 9,дешифратор кода адреса синхропрограмли 10, комл1утаторы 11, блок памяти команд 12, дешифратор адресов команд 13, счетчик адреса команд 14, устройство управления счетчиком адреса команд 15, регистрь сдвига 16-18, элементы И 19-26, сумматор 27, регистр сдвига 28, элемент И 29, триггер 30, элемент И 31, входы 32, 33 машины, выход 34, выходы 35-38 делителей частоты, дополнительные :§1Лёмён тн И 39-41. Работает вычислительная машина .следующим образом.

На вход элемента И 39 поступают сй;гналы с прямого выхода третье р регистра сдвига 18, и при наличии раэреиаюгцего сиГнал а на вФорЬм бходе

элемента И 39 с памяти б микроко мггнж сигналы с регистра 18 поступают на второй вход сумматора 27. CnrH ajifci с инверсного выхода регистра сдвига 18 JBoCtSnaiOT на BjxpS элемента И 40 и при наличии paspiemaroщеГ-о сигнала с памяти микрокоманд б- на первый вход сумматора 27. Сигнал &11НЕГе|)ён огб выход а чёт вертого ре гистра сдвига 28 поступает на второй вход сумматора 27 при нзличии ра§рШакяцего сигнала на управляющем входе элемента И 41.

При одновременной подаче раэре Шайщйхсигналов на входы элементо в

И 26 и 40 на первом 9Д УМ зтора орРйй1уетс1 ДйЭ Ш1 № ТтЁ я1йгот ои инверсного выходов регистра сдвига 18,а йри подаче игналов ;н|1 Хправляю11ще входы элементовИ.

39, 24 или 24 и 41 - дизъюнкция сиг налбв прямых выходов регистров сдви. и. 28 соответственно. - - y f Q ffg fjfj fjp- ff У,щ сигналов

; на элементах И 24-26 и 31-4Г позво 1;№ro(5p fанкзовать микрокоманды вы CflriaHnH единицы младшего разряда из

свДёржимого регистров сдвига 16-18

| 1тр&вляющие сигналы на элементах И

26, 24 и 4l), динйцы младаего сс5держимогб регистра сдвига

«

J

784854

28 (упраШ йййШесигналына элементах И 24, 26 и 40), вычитание из содержимого регистров/сдвига 16, 18 содержимого регистра 28 сдвига (управляющие сигналы на элементах И 26 и 41) и др. 5 . .

Предложенное техническое радение при минимальных аппаратурных затратах позволяет резко увеличить число возможных комбинаций.

10

Формула изобретени я

ЦифрбВсГя э лёк ронная вычислительная маишйа последовательного действия по авт.свид. №532295, о т л и- чаю 1ц а-я с я тем, что с целью повышения быстродействия, она со.Й1| жит б 6йнитёльные элементы И, причем входы первого и второго дополнительных элементов И подкЛЙЧеНы соответственно к прямому и инверсному выходам третьего регистра сдвига,; а. - соответственно кО рторЪйуй Тпёрвому входам сумматора, первый Вход третьего дополнительного элемента И соединен с инверсным выходом четвертого регистра сдвига, а вых(рд -совторым входом сумматора, вторые входы первого,, второго и третьего дополнительных элементов И соединены с дополнительными выходами;памяти микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU654948A2 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU658564A2 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU678486A2 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU591076A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Микропроцессор | 1984 |

|

SU1257657A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Микропроцессор | 1982 |

|

SU1045231A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

Авторы

Даты

1979-08-05—Публикация

1976-03-15—Подача