Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств (АУ) вычислительных машин.

Целью изобретения является сокращение оборудования с .одновременным повышением быстродействия путем сокращения времени такта.

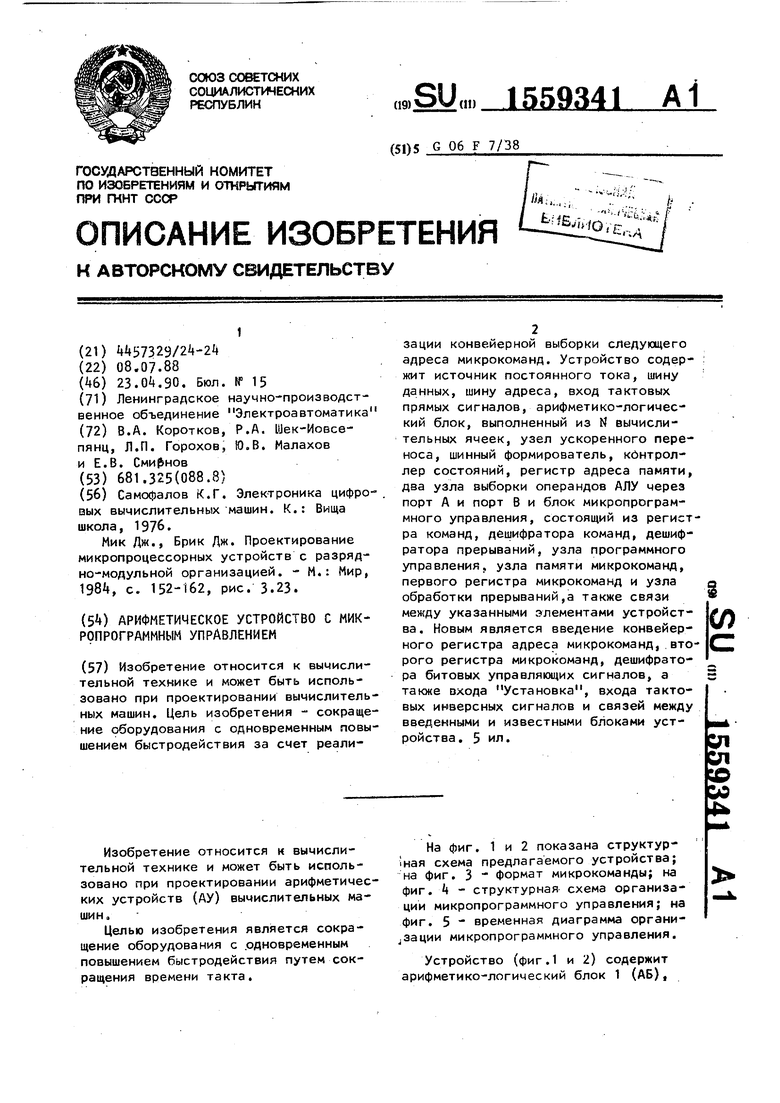

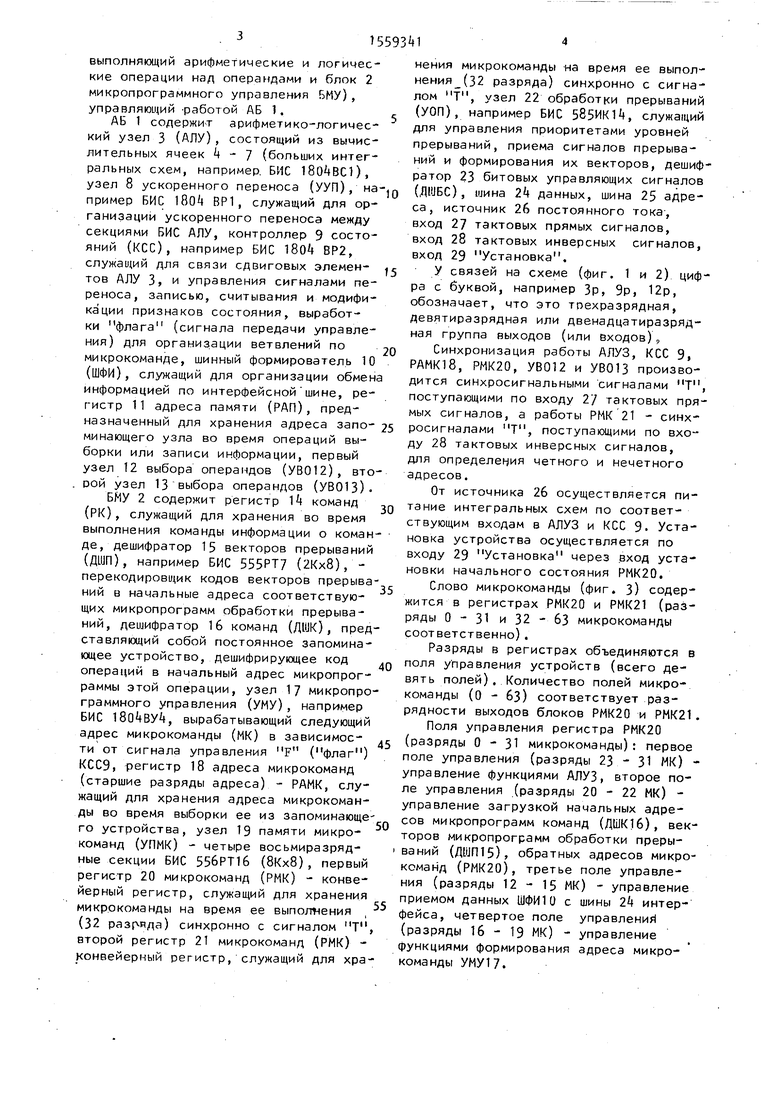

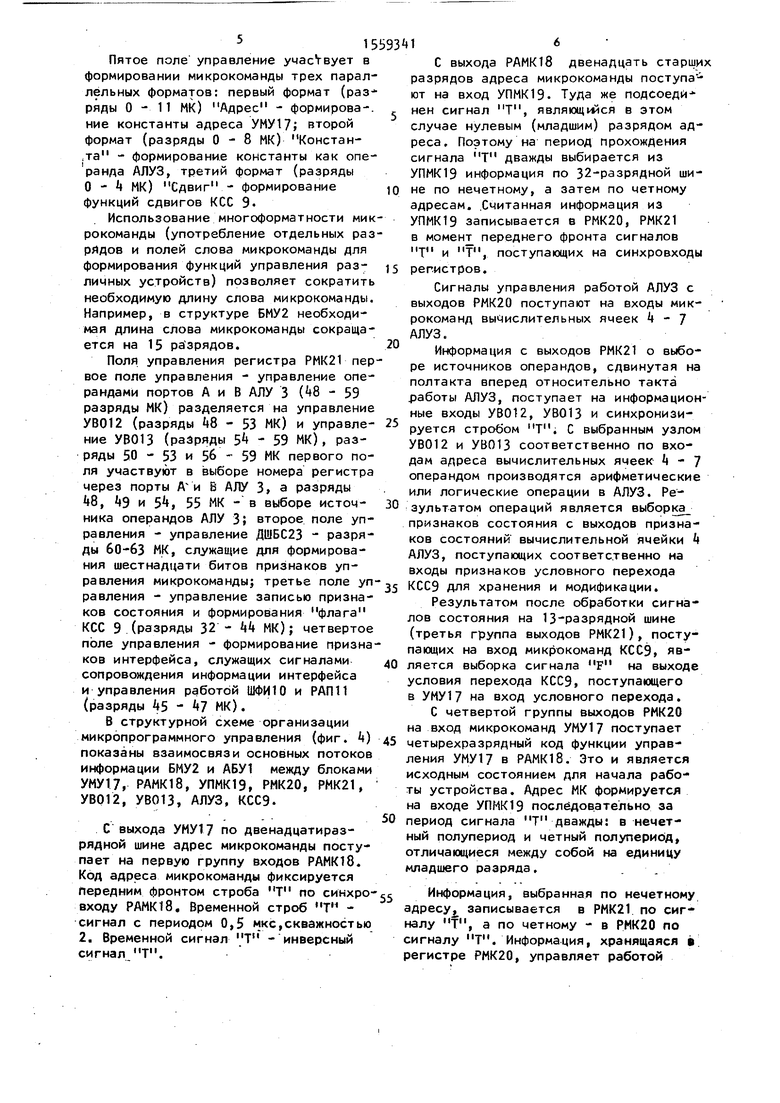

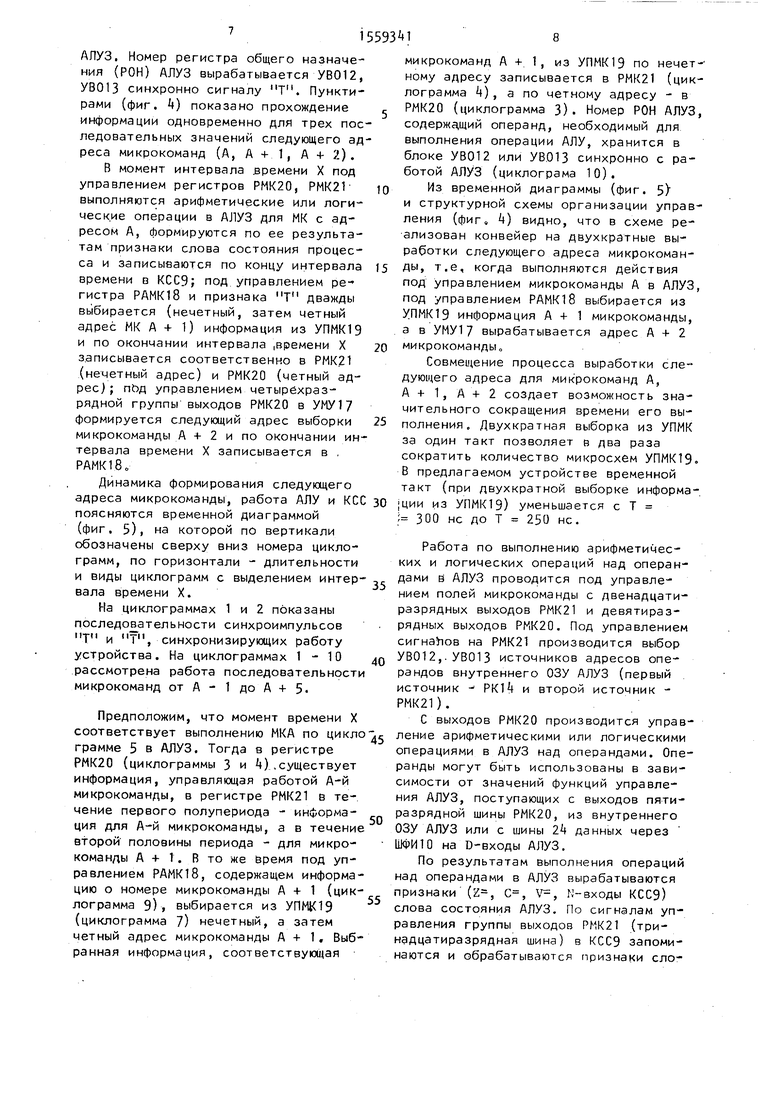

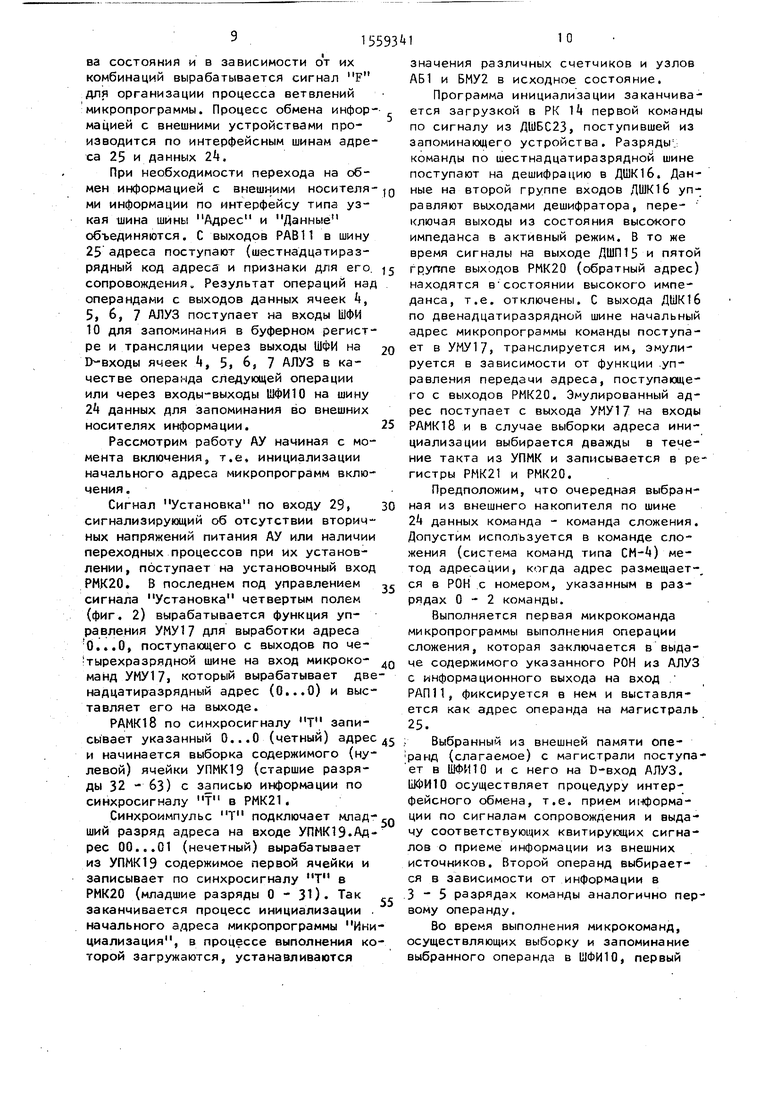

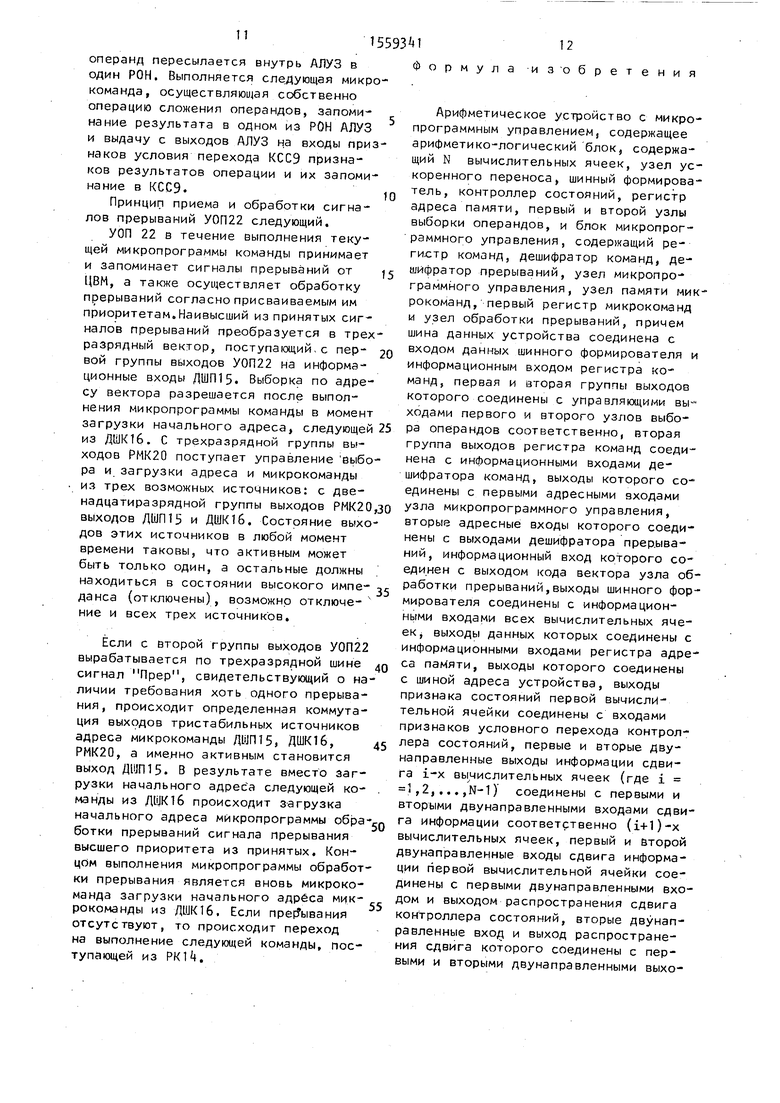

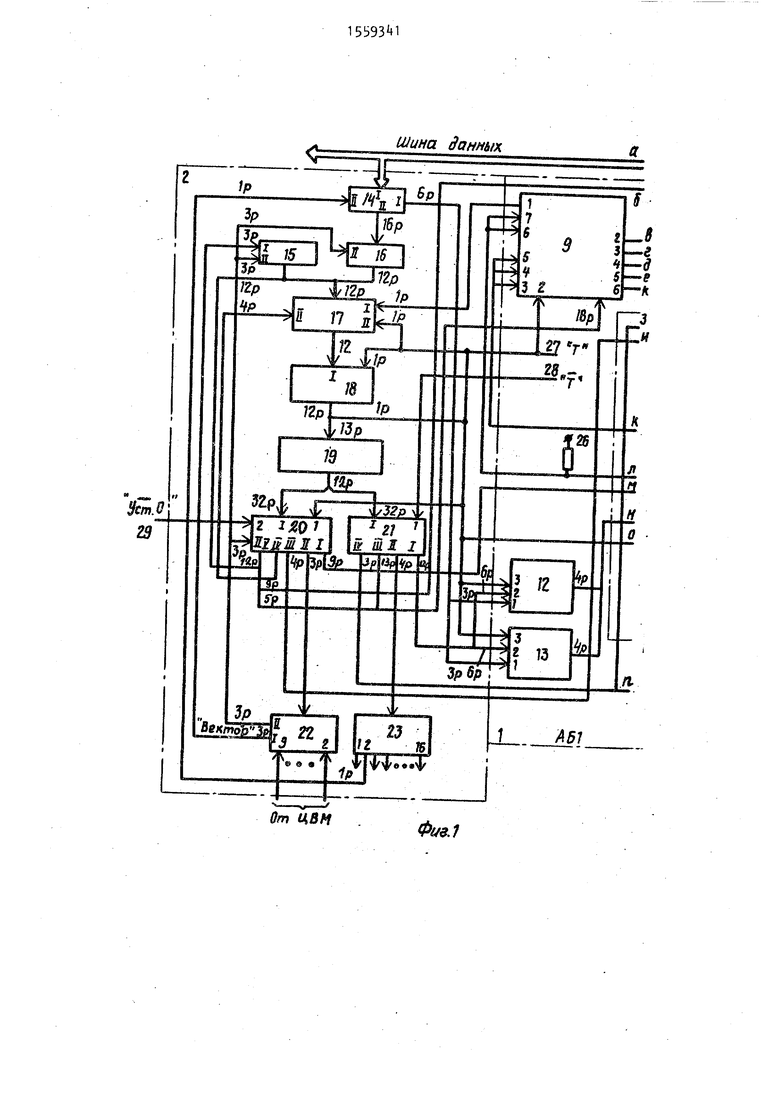

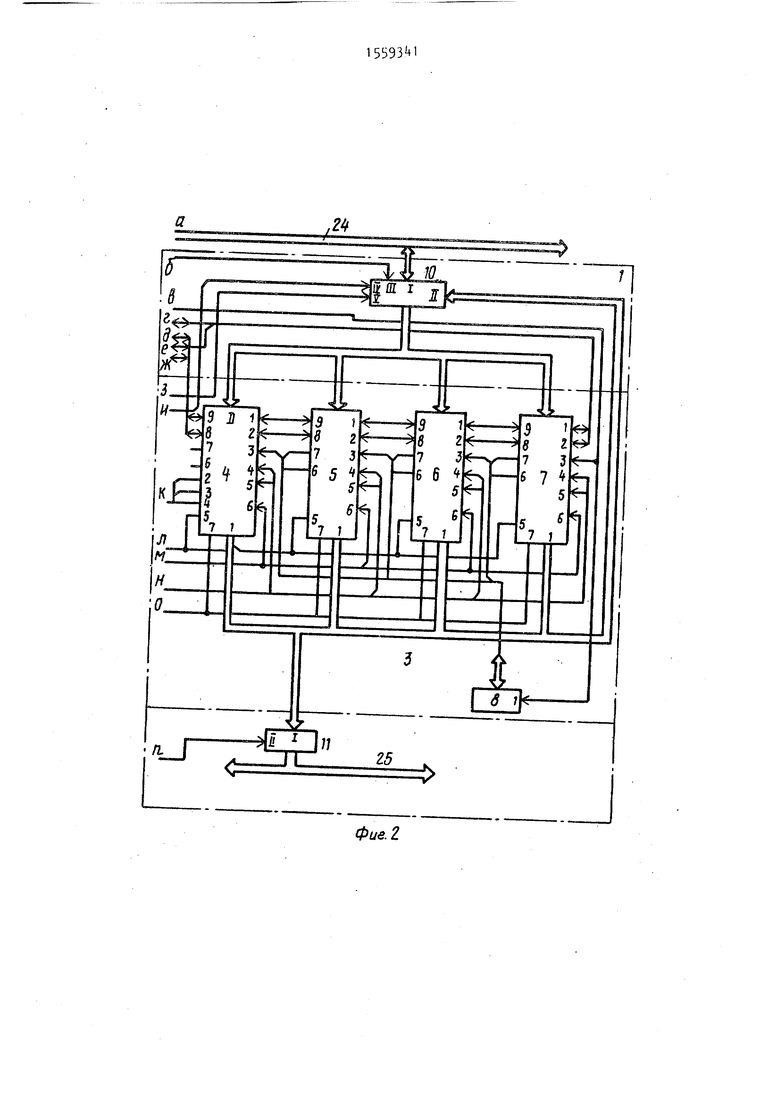

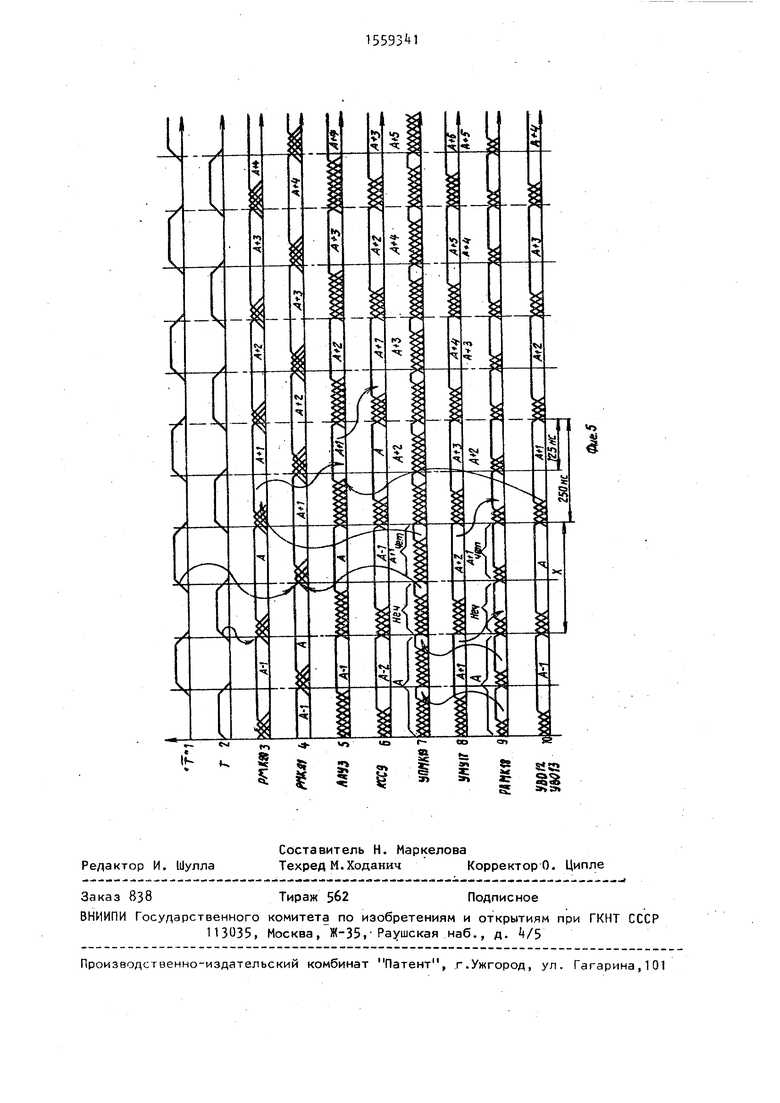

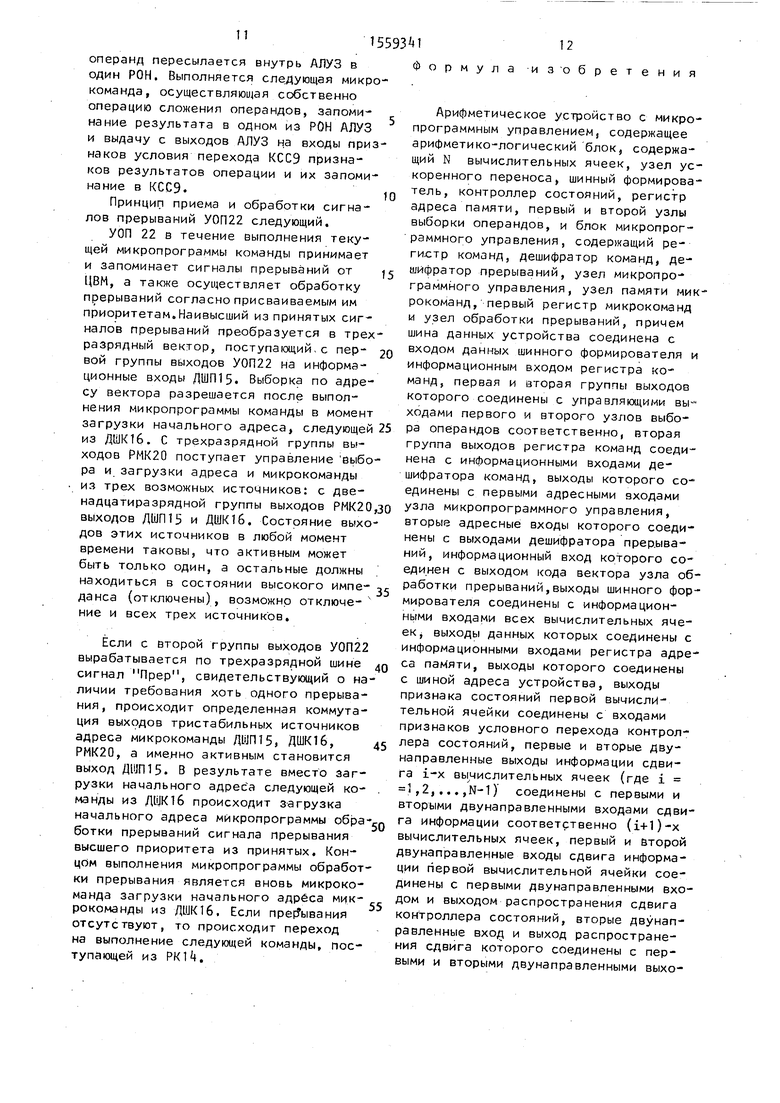

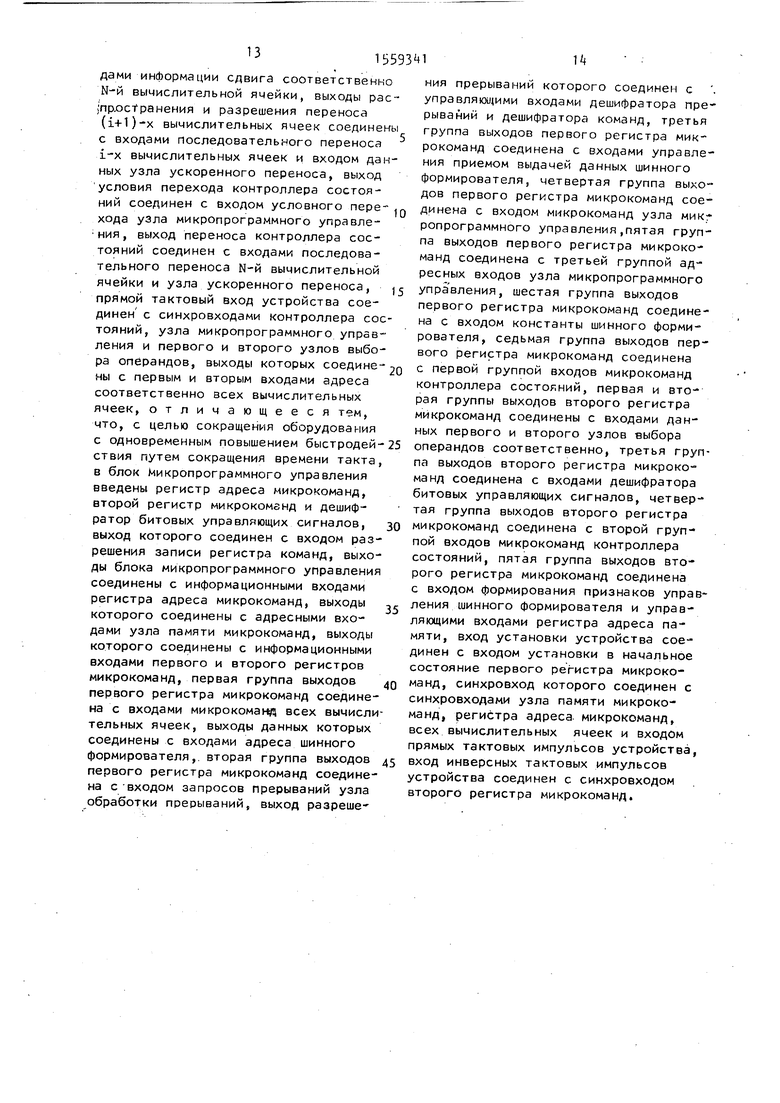

На фиг. 1 и 2 показана структур- ная схема предлагаемого устройства; на фиг. 3 - формат микрокоманды; на фиг. 4 - структурная схема организации микропрограммного управления; на фиг. 5 временная диаграмма органи- лзации микропрограммного управления.

Устройство (фиг.1 и 2) содержит арифметико-логический блок 1 (АБ),

выполняющий арифметические и логические операции над операндами и блок 2 микропрограммного управления БМУ), управляющий работой АБ 1.

АБ 1 содержит арифметико-логичес- кий узел 3 (АЛУ), состоящий из вычислительных ячеек 4-7 (больших ральных схем, например БИС 1804ВС1), узел 8 ускоренного переноса (УУП), на пример БИС 180А ВР1, служащий для организации ускоренного переноса между секциями БИС АЛУ, контроллер 9 состояний (КСС), например ЬИС 180 ВР2, служащий для связи сдвиговых элемен- тов АЛУ 3, и управления сигналами переноса, записью, считывания и модификации признаков состояния, выработки флага (сигнала передачи управления) для организации ветвлений по микрокоманде, шинный формирователь 10 (ШФИ), служащий для организации обмен информацией по интерфейсной шине, регистр 11 адреса памяти (РАП), предназначенный для хранения адреса запо- минающего узла во время операций выборки или записи информации, первый узел 12 выбора операндов (УВ012), второй узел 13 выбора операндов (УВ013).

БМУ 2 содержит регистр 1 команд (РК), служащий для хранения во время выполнения команды информации о команде, дешифратор 15 векторов прерываний (ДШП), например БИС 555РТ7 (2Кх8), - перекодировщик кодов векторов прерываний в начальные адреса соответствующих микропрограмм обработки прерываний, дешифратор 16 команд (ДШК), представляющий собой постоянное запоминающее устройство, дешифрирующее код операции в начальный адрес микропро - раммы этой операции, узел 17 микропрограммного управления (УМУ), например БИС , вырабатывающий следующий адрес микрокоманды (МК) в зависимое- ти от сигнала управления F (флаг) КСС9, регистр 18 адреса микрокоманд (старшие разряды адреса) - РАМК, служащий для хранения адреса микрокоманды во время выборки ее из запоминающе го устройства, узел 19 памяти микрокоманд (УПМК) - четыре восьмиразрядные секции БИС 556РТ16 (8Кх8), первый регистр 20 микрокоманд (РМК) - конвейерный регистр, служащий для хранения микрокоманды на время ее выполнения (32 разр-нда) синхронно с сигналом Т второй регистр 21 микрокоманд (РМК) - конвейерный регистр, служащий для хра

g 0 5

Q 5

0

5

0

5

нения микрокоманды «а время ее выпол- нения(32 разряда) синхронно с сигналом Т, узел 22 обработки прерываний (УОП), например БИС 585ИК1, служащий для управления приоритетами уровней прерываний, приема сигналов прерываний и формирования их векторов, дешифратор 23 битовых управляющих сигналов (Д1УБС), шина 2k данных, шина 25 адреса, источник 26 постоянного тока, вход 27 тактовых прямых сигналов, вход 28 тактовых инверсных сигналов, вход 29 Установка.

У связей на схеме (фиг. 1 и 2) цифра с буквой, например Зр, 9р 12р, обозначает, что это трехразрядная, девятиразрядная или двенадцатиразрядная группа выходов (или входов),

Синхронизация работы АЛУЗ, КСС 9, РАМК18, РМК20, УВ012 и УВ013 производится сиНхросигнальными сигналами Т, поступающими по входу 2/ тактовых прямых сигналов, а работы РМК 21 - синхросигналами Т, поступающими по входу 28 тактовых инверсных сигналов, для определения четного и нечетного адресов.

От источника 26 осуществляется питание интегральных схем по соответствующим входам в АЛУЗ и КСС 9 Установка устройства осуществляется по входу 29 Установка через вход установки начального состояния РМК20.

Слово микрокоманды (фиг. 3) содержится в регистрах РМК20 и РМК21 (разряды 0-3 и 32 - 63 микрокоманды соответственно).

Разряды в регистрах объединяются в поля управления устройств (всего девять полей). Количество полей микрокоманды (0 - 63) соответствует разрядности выходов блоков РМК20 и РМК21.

Поля управления регистра РМК20 (разряды 0-31 микрокоманды): первое поле управления (разряды 23-31 МК) - управление функциями АЛУЗ, второе поле управления (разряды 20 - 22 МК) - управление загрузкой начальных адресов микропрограмм команд (ДЫК16), векторов микропрограмм обработки прерываний (ДШП15), обратных адресов микрокоманд (РМК20), третье поле управления (разряды 12-15 МК) - управление приемом данных ШФИ10 с шины 2k интерфейса, четвертое поле управлений (разряды 16-19 МК) - управление функциями формирования адреса микрокоманды УМУ17.

51559341

Пятое поле управление участвует в формировании микрокоманды трех параллельных форматов: первый формат (раз- ряды 0-11 МК) Адрес - формирова-. ние константы адреса УМУ17; второй формат (разряды 0-8 МК) КонстанII .

формирование константы как опета

ранда АЛУЗ, третий формат (разряды 0-4 МК) Сдвиг - формированиеJQ

функций сдвигов КСС 9.

Использование многоформатности микрокоманды (употребление отдельных разрядов и полей слова микрокоманды для формирования функций управления раз- 15 личных устройств) позволяет сократить необходимую длину слова микрокоманды. Например, в структуре БМУ2 необходимая длина слова микрокоманды сокращается на 15 ра зрядов.20

Поля управления регистра РМК21 первое поле управления - управление операндами портов А и В АЛУ 3 (48-59 разряды МК) разделяется на управление УВ012 (разряды 48 - 53 МК) и управле- 25 ние УВ013 (разряды 54 - 59 МК) , разряды 50 - 53 и 56 - 59 МК первого поля участвуют в выборе номера регистра через порты Av и В АЛУ 3, а разряды 48, 49 и 54, 55 МК - в выборе источ- зо ника операндов АЛУ 3 второе поле управления - управление ДШБС23 - разряды 60-63 МК, служащие для формирования шестнадцати битов признаков упИнформация с выходов РМК21 о ре источников операндов, сдвинута полтакта вперед относительно такт работы АЛУЗ, поступает на информа ные входы УВ012, УВО13 и синхрони руется стробом Т. С выбранным у УВ012 и УВ013 соответственно по в дам адреса вычислительных ячеек 4 операндом производятся арифметиче или логические операции в АЛУЗ. Р зультатом операций является выбо признаков состояния с выходов при ков состояний вычислительной ячей АЛУЗ, поступающих соответственно входы признаков условного переход

равления микрокоманды; третье поле уп-35 КСС9 хранения и модификации.

равления - управление записью признаков состояния и формирования флага КСС 9 (разряды 32 - 44 МК); четвертое поле управления - формирование признаков интерфейса, служащих сигналами сопровождения информации интерфейса и управления работой ШФИ10 и РАП11 (разряды 45 - 47 МК).

В структурной схеме организации микропрограммного управления (фиг. 4) показаны взаимосвязи основных потоков информации БМУ2 и АБУ1 между блоками УМУ17, РАМК18, УПМК19, РМК20, РМК21, УВ012, УВ013, АЛУЗ, КСС9.

С выхода УМУ17 по двенадцатиразрядной шине адрес микрокоманды поступает на первую группу входов РАМК18. Код адреса микрокоманды фиксируется Передним Лронтом строба Т по синхро- входу РАМК18. Временной строб Ти - сигнал с периодом 0,5 икс,скважностью 2. Временной сигнал Т - инверсный сигнал Т.

Результатом после обработки си лов состояния на 13-разрядной шин (третья группа выходов РМК21), по пающих на вход микрокоманд КСС9,

40 ляется выборка сигнала F на вы условия перехода КСС9, поступающе в УМУ17 на вход условного переход С четвертой группы выходов РМК на вход микрокоманд УМУ17 поступа

45 четырехразрядный код функции упра ления УМУ17 в РАМК18. Это и являе исходным состоянием для начала ра ты устройства. Адрес МК формирует на входе УПМК19 последовательно з

50 период сигнала Т дважды: в нече ный полупериод и четный полуперио отличающиеся между собой на едини младшего разряда.

55

Информация, выбранная по нечет адресуА записывается в РМК21 по налу Т, а по четному - в РМК20 сигналу Т. Информация, хранящая регистре РМК20, управляет работой

С выхода РАМК18 двенадцать старши разрядов адреса микрокоманды поступа - ют на вход УПМК19. Туда же подсоеди-- нен сигнал Т, являющийся в этом случае нулевым (младшим) разрядом адреса. Поэтому на период прохождения сигнала Т дважды выбирается из УПМК19 информация по 32-разрядной шине по нечетному, а затем по четному адресам. Считанная информация из УПМК19 записывается в РМК20, РМК21 в момент переднего фронта сигналов Т и Т, поступающих на синхровходы регистров.

Сигналы управления работой АЛУЗ с выходов РМК20 поступают на входы микрокоманд вычислительных ячеек 4-7 АЛУЗ.

Информация с выходов РМК21 о выборе источников операндов, сдвинутая на полтакта вперед относительно такта работы АЛУЗ, поступает на информационные входы УВ012, УВО13 и синхронизируется стробом Т. С выбранным узлом УВ012 и УВ013 соответственно по входам адреса вычислительных ячеек 4-7 операндом производятся арифметические или логические операции в АЛУЗ. Результатом операций является выборка признаков состояния с выходов признаков состояний вычислительной ячейки 4 АЛУЗ, поступающих соответственно на входы признаков условного перехода

КСС9 хранения и модификации.

Результатом после обработки сигналов состояния на 13-разрядной шине (третья группа выходов РМК21), поступающих на вход микрокоманд КСС9, является выборка сигнала F на выходе условия перехода КСС9, поступающего в УМУ17 на вход условного перехода. С четвертой группы выходов РМК20 на вход микрокоманд УМУ17 поступает

четырехразрядный код функции управления УМУ17 в РАМК18. Это и является исходным состоянием для начала работы устройства. Адрес МК формируется на входе УПМК19 последовательно за

период сигнала Т дважды: в нечетный полупериод и четный полупериод, отличающиеся между собой на единицу младшего разряда.

Информация, выбранная по нечетному адресуА записывается в РМК21 по сигналу Т, а по четному - в РМК20 по сигналу Т. Информация, хранящаяся в регистре РМК20, управляет работой

71

АЛУЗ. Номер регистра общего назначения (РОН) АЛУЗ вырабатывается УВ012, УВ013 синхронно сигналу Т. Пунктирами (фиг. 4) показано прохождение информации одновременно для трех последовательных значений следующего адреса микрокоманд (А, А + 1, А + 2).

В момент интервала времени X под управлением регистров РМК20, РМК21 выполняются арифметические или логические операции в АЛУЗ для МК с адресом А, формируются по ее результатам признаки слова состояния процесса и записываются по концу интервала времени в КСС9; под управлением регистра РАМК18 и признака Т дважды выбирается (нечетный, затем четный адрес МК А + 1) информация из УПМК19 и по окончании интервала ,времени X записывается соответственно в РМК21 (нечетный адрес) и РМК20 (четный адрес) ; под управлением четырёхразрядной группы выходов РМК20 в УМУ 17 формируется следующий адрес выборки микрокоманды А + 2 и по окончании интервала времени X записывается в , РАМК18,

Динамика формирования следующего адреса микрокоманды, работа АЛУ и КС поясняются временной диаграммой (фиг. 5), на которой по вертикали обозначены сверху вниз номера циклограмм, по горизонтали - длительности и виды циклограмм с выделением интервала времени X.

На циклограммах 1 и 2 показаны последовательности синхроимпульсов Т и Т, синхронизирующих работу устройства. На циклограммах 1-10 рассмотрена работа последовательност микрокоманд от А - 1 до А + 5.

Предположим, что момент времени X

0

5

0

0

5

8

микрокоманд А + 1, из УПМК19 по нечет- ному адресу записывается в РМК21 (циклограмма k), а по четному адресу - в РМК20 (циклограмма 3). Номер РОН АЛУЗ, содержаний операнд, необходимый для выполнения операции АЛУ, хранится в блоке УВ012 или УВ013 синхронно с работой АЛУЗ (циклограма 10).

Из временной диаграммы (фиг. 5У и структурной схемы организации управления (фиг, А) видно, что в схеме реализован конвейер на двухкратные выработки следующего адреса микрокоманды, т.е, когда выполняются действия под управлением микрокоманды А в АЛУЗ, под управлением РАМК18 выбирается из УПМК19 информация А + 1 микрокоманды, а в УМУ17 вырабатывается адрес А + 2 микрокоманды

Совмещение процесса выработки следующего адреса для микрокоманд А, А + 1, А + 2 создает возможность значительного сокращения времени его выполнения. Двухкратная выборка из УПМК за один такт позволяет в два раза сократить количество микросхем УПМК19. В предлагаемом устройстве временной такт (при двухкратной выборке информации из УПМК19) уменьшается с Т ; 300 не до Т 250 не.

Работа по выполнению арифметических и логических операций над операндами и АЛУЗ проводится под управлением полей микрокоманды с двенадцатиразрядных выходов РМК21 и девятиразрядных выходов РМК20. Под управлением сигналов на РМК21 производится выбор УВ012,.УВ013 источников адресов операндов внутреннего ОЗУ АЛУЗ (первый источник - PKI t и второй источник - РМК21).

С выходов РМК20 производится управ

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании вычислительных машин. Цель изобретения - сокращение оборудования с одновременным повышением быстродействия за счет реализации конвейерной выборки следующего адреса микрокоманд. Устройство содержит источник постоянного тока, шину данных, шину адреса, вход тактовых прямых сигналов, арифметико-логический блок, выполненный из N вычислительных ячеек, узел ускоренного переноса, шинный формирователь, контроллер состояний, регистр адреса памяти, два узла выборки операндов АЛУ через порт А и порт В и блок микропрограммного управления, состоящий из регистра команд, дешифратора команд, дешифратора прерываний, узла программного управления, узла памяти микрокоманд, первого регистра микрокоманд и узла обработки прерываний, а также связи между указанными элементами устройства. Новым является введение конвейерного регистра адреса микрокоманд, второго регистра микрокоманд, дешифратора битовых управляющих сигналов, а также входа "Установка", входа тактовых инверсных сигналов и связей между введенными и известными блоками устройства. 4 ил.

соответствует выполнению МКА по циклоне ление арифметическими или логическими

грамме 5 в АЛУЗ. Тогда в регистре РМК20 (циклограммы 3 и Ц).существует информация, управляющая работой А-й микрокоманды, в регистре РМК21 в течение первого полупериода - информация для А-й микрокоманды, а в течение второй половины периода - для микрокоманды А + 1. В то же время под управлением РАМК18, содержащем информацию о номере микрокоманды А + 1 (циклограмма 9), выбирается из УПМК19 (циклограмма 7) нечетный, а затем четный адрес микрокоманды А + 1. Выбранная информация, соответствующая

50

55

операциями в АЛУЗ над операндами. Операнды могут быть использованы в зависимости от значений функций управления АЛУЗ, поступающих с выходов пятиразрядной шины РМК20, из внутреннего ОЗУ АЛУЗ или с шины 2 данных через ШФИ10 на D-входы АЛУЗ.

По результатам выполнения операций над операндами в АЛУЗ вырабатываются признаки (Z-, С, V, К-входы КСС9) слова состояния АЛУЗ. По сигналам управления группы выходов РМК21 (тринадцатиразрядная шина) в КСС9 запоминаются и обрабатываются признаки ело0

5

операциями в АЛУЗ над операндами. Операнды могут быть использованы в зависимости от значений функций управления АЛУЗ, поступающих с выходов пятиразрядной шины РМК20, из внутреннего ОЗУ АЛУЗ или с шины 2 данных через ШФИ10 на D-входы АЛУЗ.

По результатам выполнения операций над операндами в АЛУЗ вырабатываются признаки (Z-, С, V, К-входы КСС9) слова состояния АЛУЗ. По сигналам управления группы выходов РМК21 (тринадцатиразрядная шина) в КСС9 запоминаются и обрабатываются признаки елова состояния и в зависимости от их комбинаций вырабатывается сигнал F для организации процесса ветвлений микропрограммы. Процесс обмена информацией с внешними устройствами производится по интерфейсным шинам адреса 25 и данных 2k,

При необходимости перехода на обмен информацией с внешними носителя-j ми информации по интерфейсу типа узкая шина шины Адрес и Данные объединяются. С выходов РАВ11 в шину 25 адреса поступают (шестнадцатиразрядный код адреса и признаки для его. 1 сопровождения. Результат операций над операндами с выходов данных ячеек k, 5, 6, 7 АЛУЗ поступает на входы ШФИ 10 для запоминания в буферном регистре и трансляции через выходы ШФИ на 2 D-входы ячеек , 5, 6, 7 АЛУЗ в качестве операнда следующей операции или через входы-выходы ШФИ10 на шину 2k данных для запоминания во внешних носителях информации.2

Рассмотрим работу АУ начиная с момента включения, т.е. инициализации начального адреса микропрограмм включения .

Сигнал Установка по входу 29, 3 сигнализирующий об отсутствии вторичных напряжений питания АУ или наличии переходных процессов при их установлении, поступает на установочный вход РМК20. В последнем под управлением 3 сигнала Установка четвертым полем (фиг. 2) вырабатывается функция управления УМУ1 для выработки адреса 0...0, поступающего с выходов по четырехразрядной шине на вход микроко- 4 манд УМУ17| который вырабатывает двенадцатиразрядный адрес (0...0) и выставляет его на выходе.

РАМК18 по синхросигналу Т записывает указанный 0...0 (четный) адрес 4 и начинается выборка содержимого (нулевой) ячейки УПМК19 (старшие разряды 32 - 63) с записью информации по синхросигналу Т в РМК21.

Синхроимпульс Т подключает ший разряд адреса на входе УПМК19.Адрес 00...01 (нечетный) вырабатывает из УПМК19 содержимое первой ячейки и записывает по синхросигналу Т в РМК20 (младшие разряды 0 - 31). Так заканчивается процесс инициализации начального адреса микропрограммы Инициализация, в процессе выполнения которой загружаются, устанавливаются

5

jg 15 20 25

30 35 4Q 4$ ,,

0 5

значения различных счетчиков и узлов АБ1 и БМУ2 в исходное состояние.

Программа инициализации заканчивается загрузкой в РК первой команды по сигналу из ДШБС23, поступившей из запоминающего устройства. Разряды1, команды по шестнадцатиразрядной шине поступают на дешифрацию в ДШК16. Данные на второй группе входов ДШК16 управляют выходами дешифратора, пере- ключая выходы из состояния высокого импеданса в активный режим. В то же время сигналы на выходе ДШП15 и пятой группе выходов РМК20 (обратный адрес) находятся в состоянии высокого импеданса, т.е. отключены. С выхода ДЫК16 по двенадцатиразрядной шине начальный адрес микропрограммы команды поступает в УМУ17, транслируется им, эмулируется в зависимости от функции .управления передачи адреса, поступающего с выходов РМК20. Эмулированный адрес поступает с выхода УМУ17 на входы РАМК18 и в случае выборки адреса инициализации выбирается дважды в течение такта из УПМК и записывается в регистры РМК21 и РМК20.

Предположим, что очередная выбранная из внешнего накопителя по шине 2k данных команда - команда сложения. Допустим используется в команде сложения (система команд типа СМ- ) метод адресации, когда адрес размещает-, ся в РОН с номером, указанным в разрядах 0-2 команды.

Выполняется первая микрокоманда микропрограммы выполнения операции сложения, которая заключается в выдаче содержимого указанного РОН из АЛУЗ с информационного выхода на вход РАП11, фиксируется в нем и выставляется как адрес операнда на магистраль 25.

Выбранный из внешней памяти операнд (слагаемое) с магистрали поступает в ШФИ10 и с него на D-вход АЛУЗ. ШФИ10 осуществляет процедуру интерфейсного обмена, т.е. прием информации по сигналам сопровождения и выдачу соответствующих квитирующих сигналов о приеме информации из внешних источников. Второй операнд выбирается в зависимости от информации в 3-5 разрядах команды аналогично первому операнду.

Во время выполнения микрокоманд, осуществляющих выборку и запоминание выбранного операнда в ШФИ10, первый

11

операнд пересылается внутрь АЛУЗ в один РОН. Выполняется следующая микрокоманда, осуществляющая собственно операцию сложения операндов, запоминание результата в одном из РОН АЛУЗ и выдачу с выходов АЛУЗ на входы признаков условия перехода КСС9 признаков результатов операции и их запоминание в КСС9«ю

Принцип приема и обработки сигналов прерываний УОП22 следующий.

УОП 22 в течение выполнения текущей микропрограммы команды принимает и запоминает сигналы прерываний от J ЦВМ, а также осуществляет обработку прерываний согласно присваиваемым им приоритетам.Наивысший из принятых сигналов прерываний преобразуется в трехразрядный вектор, поступающий с пер- 2 вой группы выходов УОП22 на информационные входы ДШП15. Выборка по адресу вектора разрешается после выполнения микропрограммы команды в момент загрузки начального адреса, следующей 2 из ДШК16. С трехразрядной группы выходов РМК20 поступает управление выбора и загрузки адреса и микрокоманды из трех возможных источников: с двенадцатиразрядной группы выходов РМК20,зо Узла микропрограммного управления, выходов ДШП15 и ДШК16. Состояние выходов этих источников в любой момент времени таковы, что активным может быть только один, а остальные должны находиться в состоянии высокого импе- or данса (отключены), возможно отключение и всех трех источников.

Если с второй группы выходов УОП22 вырабатывается по трехразрядной шине 0 сигнал Прер, свидетельствующий о наличии требования хоть одного прерывания, происходит определенная коммутация выходов тристабильных источников адреса микрокоманды ДЫП15, ДШК16, 45 РМК20, а именно активным становится выход ДШП15. В результате вместо за(- рузки начального адреса следующей команды из ДШК16 происходит загрузка

вторые адресные входы которого соединены с выходами дешифратора прерываний, информационный вход которого соединен с выходом кода вектора узла обработки прерываний,выходы шинного формирователя соединены с информационными входами всех вычислительных ячеек, выходы данных которых соединены с информационными входами регистра адреса памяти, выходы которого соединены с шиной адреса устройства, выходы признака состояний первой вычислительной ячейки соединены с входами признаков условного перехода контроллера состояний, первые и вторые двунаправленные выходы информации сдвига i-x вычислительных ячеек (где i ,2,...,N-1) соединены с первыми и вторыми двунаправленными входами сдвиначального адреса микропрограммы обра-5д га информации соответственно (i+1)-x

вычислительных ячеек, первый и второй двунаправленные входы сдвига информации первой вычислительной ячейки соединены с первыми двунаправленными вхоботки прерываний сигнала прерывания высшего приоритета из принятых. Концом выполнения микропрограммы обработки прерывания является вновь микрокоманда загрузки начального адреса мик- дом и выходом распространения сдвига рокоманды из ДШК16, Если прерыванияконтроллера состояний, вторые двунапотсутствуют, то происходит переходравленные вход и выход распространена выполнение следующей команды, пос- ния сдвига которого соединены с пер- тупающей из РКТ.выми и вторыми двунаправленными выхо

ормула

12 з о б р е т

е н и я

Арифметическое устройство с микропрограммным управлением, содержащее арифметико-логический блок( содержащий N вычислительных ячеек, узел ускоренного переноса, шинный формирователь, контроллер состояний, регистр адреса памяти, первый и второй узлы выборки операндов, и блок микропрограммного управления, содержащий регистр команд, дешифратор команд, дешифратор прерываний, узел микропрограммного управления, узел памяти микрокоманд, первый регистр микрокоманд и узел обработки прерываний, причем шина данных устройства соединена с входом данных шинного формирователя и информационным входом регистра команд, первая и аторая группы выходов которого соединены с управляющими выходами первого и второго узлов выбора операндов соответственно, вторая группа выходов регистра команд соединена с информационными входами дешифратора команд, выходы которого соединены с первыми адресными входами

Узла микропрограммного управления,

вторые адресные входы которого соединены с выходами дешифратора прерываний, информационный вход которого соединен с выходом кода вектора узла обработки прерываний,выходы шинного формирователя соединены с информационными входами всех вычислительных ячеек, выходы данных которых соединены с информационными входами регистра адреса памяти, выходы которого соединены с шиной адреса устройства, выходы признака состояний первой вычислительной ячейки соединены с входами признаков условного перехода контроллера состояний, первые и вторые двунаправленные выходы информации сдвига i-x вычислительных ячеек (где i ,2,...,N-1) соединены с первыми и вторыми двунаправленными входами сдвивычислительных ячеек, первый и второй двунаправленные входы сдвига информации первой вычислительной ячейки соединены с первыми двунаправленными входом и выходом распространения сдвига контроллера состояний, вторые двунап1

1

дами информации сдвига соответственно N-й вычислительной ячейки, выходы рас™ ;пр.остранения и разрешения переноса (i+1)-x вычислительных ячеек соединены с входами последовательного переноса 1-х вычислительных ячеек и входом данных узла ускоренного переноса, выход условия перехода контроллера состояний соединен с входом условного перехода узла микропрограммного управле- ния, выход переноса контроллера состояний соединен с входами последовательного переноса N-й вычислительной ячейки и узла ускоренного переноса, прямой тактовый вход устройства соединен с синхровходами контроллера состояний, узла микропрограммного управления и первого и второго узлов выбора операндов, выходы которых соединен ны с первым и вторым входами адреса соответственно всех вычислительных ячеек, отличающееся тем, что, с целью сокращения оборудования с одновременным повышением быстродей-2 ствия путем сокращения времени такта, в блок Микропрограммного управления введены регистр адреса микрокоманд, второй регистр микрокоманд и дешифратор битовых управляющих сигналов, 3 выход которого соединен с входом разрешения записи регистра команд, выходы блока микропрограммного управления соединены с информационными входами регистра адреса микрокоманд, выходы которого соединены с адресными входами узла памяти микрокоманд, выходы которого соединены с информационными входами первого и второго регистров микрокоманд, первая группа выходов первого регистра микрокоманд соединена с входами микрокоманд всех вычислительных ячеек, выходы данных которых соединены с входами адреса шинного формирователя,, вторая группа выходов д первого регистра микрокоманд соединена с-входом запросов прерываний узла обработки прерываний, выход разреше3

4

0

5

о5 0 5

5

0

ния прерываний которого соединен с управляющими входами дешифратора прерываний и дешифратора команд, третья группа выходов первого регистра микрокоманд соединена с входами управления приемом выдачей данных шинного формирователя, четвертая группа выходов первого регистра микрокоманд соединена с входом микрокоманд узла микг ропрограммного управления,пятая группа выходов первого регистра микрокоманд соединена с третьей группой адресных входов узла микропрограммного управления, шестая группа выходов первого регистра микрокоманд соединена с входом константы шинного формирователя, седьмая группа выходов первого регистра микрокоманд соединена с первой группой входов микрокоманд контроллера состояний, первая и вторая группы выходов второго регистра микрокоманд соединены с входами данных первого и второго узлов выбора операндов соответственно, третья группа выходов второго регистра микрокоманд соединена с входами дешифратора битовых управляющих сигналов, четвертая группа выходов второго регистра микрокоманд соединена с второй группой входов микрокоманд контроллера состояний, пятая группа выходов второго регистра микрокоманд соединена с входом формирования признаков управления шинного формирователя и управляющими входами регистра адреса памяти, вход установки устройства соединен с входом установки в начальное состояние первого регистра микрокоманд, синхровход которого соединен с синхровходами узла памяти микрокоманд, регистра адреса микрокоманд, всех вычислительных ячеек и входом прямых тактовых импульсов устройства, вход инверсных тактовых импульсов устройства соединен с синхровходом второго регистра микрокоманд.

ltjЈ6f$l

-Т оо

СП LA LA

Формат I Адрес

Формат 2 Константа

Формат 3 Сдвиг

Формирование адреса УМУ

МФИ|6|6|7|В|9Ц(Ц

Формирование константы

0|1|2}3|4|5|б|7|8|Х1Х1Х

Управление функциями сдвига КСС9

О

I

ХХХХХХХ

Разряды

О

поле управления

Управление

БМУ

Загрузканачальногоадреса ЕМУ

Управление АЛУ

ХХХХХХХ

8

10

II

I2|I3|I4|I5

I6|I7| 8|I9

го 21}22

23|24|25|26|27 {28129 30131

л л U) UJ

J

Фиг. 3

| Самофалов К.Г | |||

| Электроника цифровых вычислительных машин | |||

| К.: Вища школа, 1976 | |||

| Мик Дж., Брик Дж | |||

| Проектирование микропроцессорных устройств с разряд- но-модульной организацией | |||

| - М.: Мир, 1984, с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-04-23—Публикация

1988-07-08—Подача