2. Микропроцессор по п.1, о тличаюцийся тем, что блок микропрограммного управления содержит регистр адреса, дешифратор функций, две группы элементовИ, группу триггеров, элемент ИЛИ, дешифратор переходов и группу селекiTOpOB, первые и в.торые информационные входы, управляющие входы и выходы которых соединены соответствен JHO с входом управления переходами блока,выходами регистра адреса,выходами дешифратора переходов и информационными входами регистра адреса, синхровход, установочный вход и выходы регистра адреса подключены соответственно к синхровходу, входу начальной установки и адресному выходу блока, вход и один из выходов дешифратора переходов соединены соответственно с входом управления переходами и управляющим выходом блока информационные входы, синхровходы i и выходы триггеров группы подключены соответственно квходу признаков блока, выходам соответствующих элементов И первой группы и первым входам соответствующих элементов И второй группы, первые входы элементов И первой группы соединены с синхровходом блока, вход и выход дешифратора функций подключены соответственно квходу дешифрации флагов , и вторытл входам соответствующих, элементов И первой и второй группы, входы элемента ИЛИ соединены с одним из| выходов дешифратора функций,и выходами элементов И второй группы, а выход элемента ИЛИ подключен к выходу признаков блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропроцессор | 1982 |

|

SU1035610A1 |

| Микропроцессор | 1985 |

|

SU1290340A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1667068A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1277107A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Микропроцессор для управления памятью микрокоманд | 1979 |

|

SU803700A1 |

| Процессор | 1984 |

|

SU1200294A1 |

1.МИКРОПРОЦЕССОР, содержащий блок обработки данных, блок микропрограммного управления, блок памяти и конвейерный регистр, инфоргаационныД вход, синхровход, первый , второй и третий выходы которого соединены с первым выходом блока памяти, синхровходом микропроцессора, управляющим выходом микропроцессора входом кода микрокоманды блока обработки данных и входом дешифрации флагов блока микропрограммного управ ления, вход начальной установки, адресный выход,вход управления переходами, вход признаков и выходпризнаков блока микропрограммного управления подключены соответственно к входу начальной установки микропроцесс ра, адресному входу и второму выход блока памяти, выходу переноса и вхо переноса блока обработки данных, информационный вход, информационный выход и адресный выход которого соединены соответственно с информационным входом, информационным выходом и адресным выходом микропроцессора, отличающийся тем, что, с целью сокращения оборудования, он содержит два триггера, дваэлемента И и элемент И-НЕ, первый и второй входы и выход которого подключены соответственно к управляющему выходу блока микропрограммного управления, выходу первого триггера и информационному входу первого триггера, первый и второй входы и выход первого элемента И соединены соответственно с синхровходом микропроцессора, выходом элемента И-НЕ и синхровходом блока микропрограммного управления, первый и второй входы и выход второго элемента И подключены соответственно к синхровходу микропроцессора, выходу второго триггера и синхровходу блока обработки данных, сихровходы и установоч-Г ные входы обоих триггеров соединены с синхровходом и входом начальной , f установки микропроцессора, а информационный вход второго триггера подключен к выходу первого триггера.

Изобретение относится к вычислительной технике и может быть использовано для обработки данных в системах управления. Известен микропроцессор, содержа щий центральный блок обработки данных, блок микропрограммного управления, блок микропрограммной памяти, конвейерный регистр, два регист ра и элемент , Недостатком данного устройства является избыточность микропрограммной памяти вследствие того, что при выполнении каждого условного перехода в микропрограмме предусматривается холостая микрокоманда Наиболее близок к предлагаемому по технической сущности микропроцес сор,, который содержит, центральный блок обработки данных, блок микропрограммного упра вления, конвейерный регистр и блок микропрограммной памяти. В микропроцессоре используется конвейерный принцип выполнения микрокоманд, который заключает ся в том, что -в одном микрокомандно цикле одновременно с выполнением те кущей микрокоманда, находящейся на конвейерном регистре. Производится выборка следующей микрокоманды. При этом выборка микрокоманды оперетает на цикл ее выполнение 2. Однако при выполнении условных переходов следующая после условного перехода микрокоманды выбирается раньше, чем формируется логическое условие, определяющее направление перехода. Поэтому при каждом условном переходе в микропрохрамме предусматривается холостая микрокоман-; да, выполняющая функцию задержки на один цикл. Если учесть, что в реаль них микропрограммах один условный переход приходится в среднем на 57 выполняе№лх микрокоманд, то 15-20% дорогостоящей микропрограммной памяти оказывается избыточным. Цель изобретения - сокращениеоборудования в. части микропрограм.лной. памяти микропроцессора. Поставленная це.пь достигается тем, что в микропроцессор, содержащий блок обра.ботки данных, блок микропрограммного управления., блок памяти и конвейерный регистр, информационный вход, синхровход, первый, второй и третий выходы которого со,единены соответственно с первым выхо;дом блока памяти,, синхровходом микропроцессора, управляющим выходом микропроцессора, входом кода микрокоманды блока обработки данных и входом дешифрации флагов блока микропрограммного управления, вход начальной установки, адресный выход вход управления переходами, вход I признаков и выход признаков блока микропрограммного управления подключены соответственно к входу начальной установки микрб процессора, адресному входу и второму выходу блока памяти, выходу переноса и входу переноса блока об гработки данных, информационный вход, информационный выход и адресный выход которого соединены соответствен но с информационным входом, информационным выходом и адресным выходом микропроцессора, введены два триггера, два элемента И и элемент. И-НЕ, первый и второй входы и выход которого подключены соответственно к управляющему выходу блока микропрограммного управления, выходу первого триггера и информационному входу первого триггера, первый и второй входы и выход первого элемента И соединены соответственно с синхровходом микропроцессора, выходом элемента И-НЕ и синхровходом блока микропрограммного управления, первый и второй входы и выход второго элементаИ подключены соответственно к синхровходу микропроцессора,выходу второго триггера и синхровходу блока обработки данных, синхровходы и установочные входы обоих триггеров соединены с синхровходом и входом начальной установки микропроцессора, а информационный вход второго триггера подключен к выходу первого триггера,

Кроме того, блок микропрограммного управления содержит регистр адреса, дешифратор функций, две группы элементов И, группу триггеров, элемент ИЛИ, дешифратор переходов и группу селекторов, первые и вторые информационные входы, управляющие входы и выходы которых соединены соответственно с входом управления переходами блока, выходами регистра адреса, выходами дешифратора переходов и информационными входами регистра адреса , синхровход,установочны вход и выходы регистра адреса подключены соответственно к синхровходу, входу Начальной установки и адресному выходублока, вход и один из выходов дешифратора переходов соединены соответственно с входом управления переходами и управляющим выходом блока, информационные входы, синхровходы и выходы триггеров группы подключены соответственно к входу признаков бло ка, выходам соответствующих элементов И первой группы и первым входам соответствующих элементов И второй группы, первые входы элементов И пер вой группы соединены с синхровходами блока, вход и выходы дешифратора функций подключены соответственно к входу дешифрации флагов и вторым входам соответствующих.элементов И первой и второй группы, элемента ИЛИ соединены с одним 1из выходов д шифратора функций и. выходами элементов И второй группы, а выход элемента ИЛИ подключен к выходу признаков блока.За счет исключения холостых микрокоманд из микропрограммы сокращается микропрограммная память.

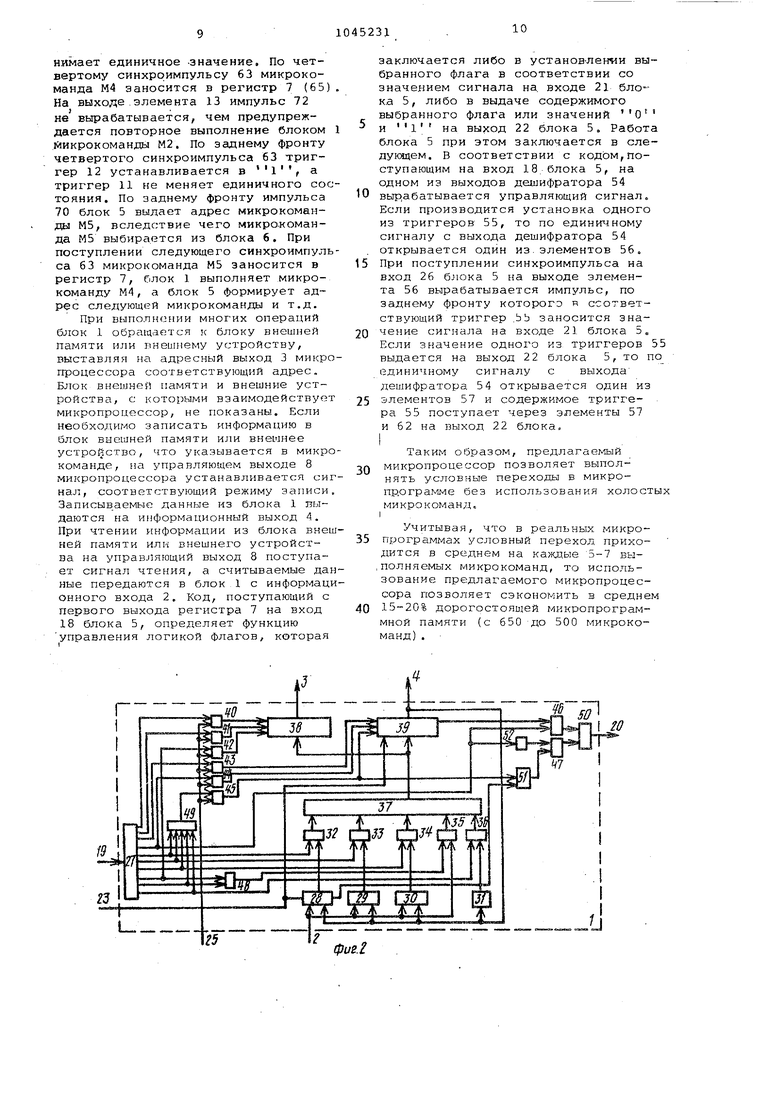

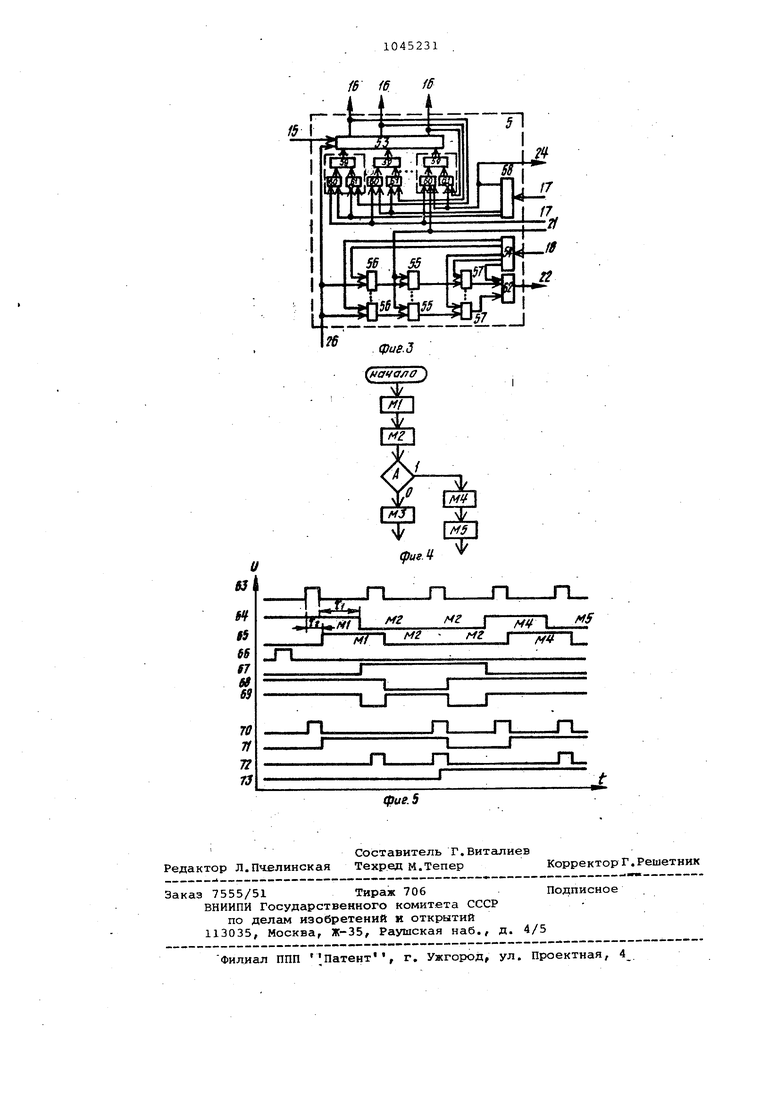

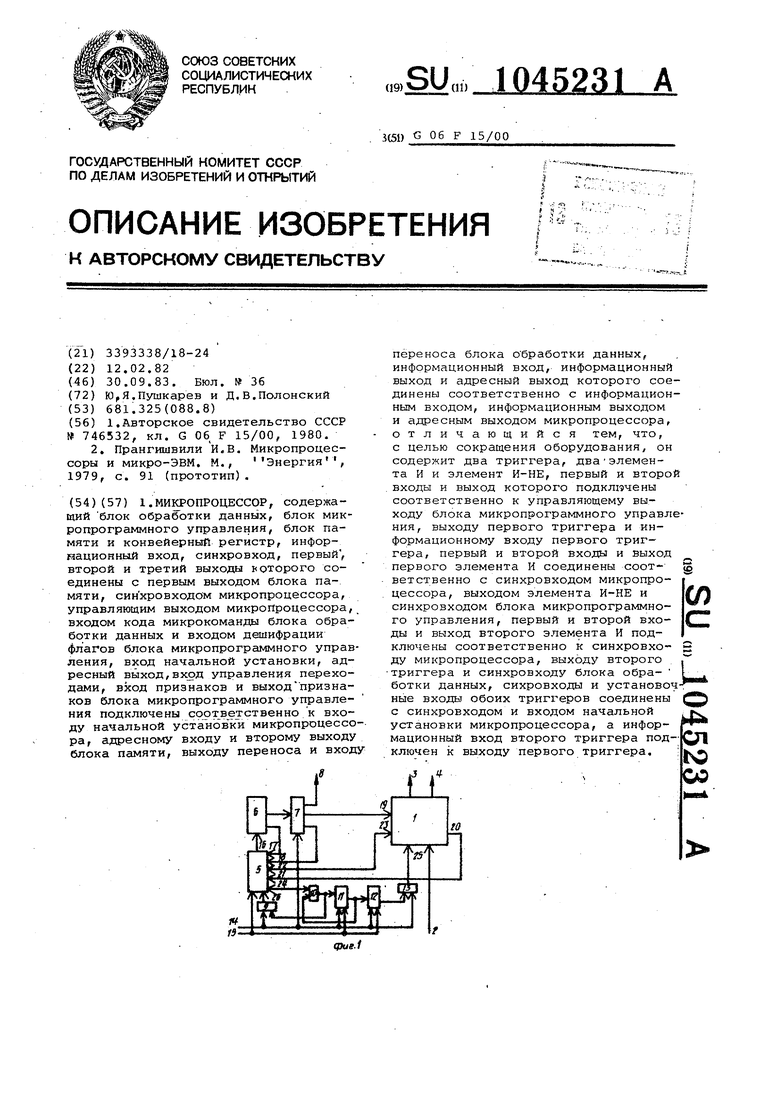

На фиг. 1 представлена структурная схема микропроцессора; на фиг.2- функциональная схема блока, обработки .данных,-на фиг.З - функциональная схема блока микропрограммного управления; на фиг. 4-алгоритм микропрограммы; на фиг. 5 - временная диаграмма выполнения микропрогрс1ммы.

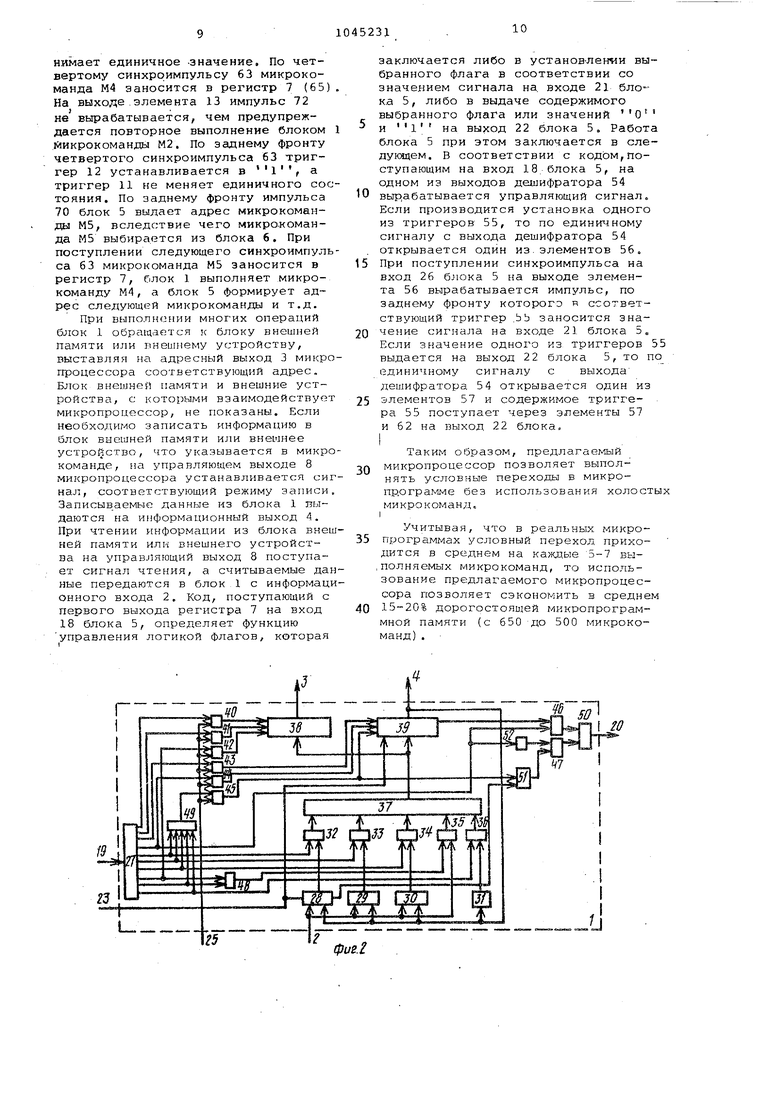

Микропроцессор содержит (фиг. 1) блок 1 обработки данных, информационный вход 2 которого является информационным входом микропроцессора, а выходы 3 и 4 являются соответствен10но адресным и информационным выходами микропроцессора,блок 5 микропрограммного управления, блок 6 памяти, конвейерный регистр 7, выход 8 которого является управляющим выходом микропроцессора, элемент И 9, эле5мент И-НЕ 10, триггеры Ни 12, элемент и 13, синхровход 14 и вход 15 начальной установки.

Адресный выход 16 блока 5 соединен с адресным входом блока 6,пер0вый выход которого соединен с входом 17 управления переходами блока 5. Второй выход блока 6 соединён с информационным входом регистра 7 первый выход которого соединен вхо5дом 18 управления дешифрацией флагов блока 5. Второй выход регистра 7 соединен с входом 19 кода микрокоманды блока 1, выход 20 переноса которого соединен с входом 21 приз0наков блока 5. Выход 22 признаков блока 5 соединен с входом 23 переноса блока 1. Управляющий выход 24 блока 5 соединен С входом элемента 10, выход которого соединен с ин5формационным входом триггера 11 и входом элемента 9. Выход триггера 11 соединен с информационным входом триггера 12 и входом элемента 10. Выход триггера 12 соединен с входом элемента 13, выход которого

0 соединен с синхоовходом 25 блока 1. Выход элемента 9 соединен с синхровходом 26 блока 5. Вход 15 начальной установки соединен с входами начальной установки блока 5 и триг5гера 11 и 12. -Входы элементов 9 и 10 и синхровходы регистра 7 и триггера 11 и 12 соединены с синхровходом 14 микропроцессора.

Блок 1 обработки данных {фиг.2)

0 содержит дешифратор 27 микроприказов, сумматор 28, элементы И 29, ИЛИ 30 и НЕ 31, группы элементов И 32-36, группу элементов ИЛИ 37,счетчик 38 адреса, сдвиговый регистр 39,

5 элементы И 40-47;элементы ИЛИ 48-50, триггер 51 и элемент НЕ 52, Вход дешифратора 27 является входом 18 .блока 1. Выходы дешифратора 27 соединены с входами элементов 40-44,. вхо0дами групп элементов 32-34-и 36,входами элементов 48 и- 49, входом, i мента 46 и входом элемента 52. Выход элемента 49 соединен с входом элемента 45. Выход элемента 40 соединен 5 f входом установки в О счетчика 38, к -счетному входу которого подклю чен выход элемента 41, а к выходу занесения - выход элемента 42. Выход элемента 43 соединен с входом установки в О регистра 39, тактирую щий вход которого подключен к выход элемента 44, Выход элемента 45 соед иен с входами занесения регистра. 39 и триггера 51,Выход элемента 48,сое динен с входами группьа элементов 35 К информационному входу 2 блока 1 подключены входы сумматора 28, входы элементов 29,30 и входа элементо 35, Выход сумматора 28 соединен с входами группы элементов 32, Выходы групп элементов 29,30 и 31 соединен® соответственно с входами групп элементов 33,34 и 36,Выходы групп элем тов 32-36 соединены с входами групп ..элементов 37,выхотрз1 которых подключе - Ы к информацйонн);лм входам счетчика 38 регистра 39, Выходы счетчика 38 и регистра 39 являются соответственно адресным выходом 3 и информационным выходом 4 блока 1, Выход регистра 39 соединен с входами сумматора 28, и входами групп элементов 29-31, К входу 25 блока 1 полключены вх , да элементов 40-45 „ Вход переноса су№-1атора 28 и вход первого сдвига регистра 39 соединены с входом 23 переноса блока 1. Выход переноса сумматора 28 соединен с информацион ным пхолом триггера 51, выход которого соединен с входом элемента 47. Выход правого сдвига регистра 39 по ключен к входу элемента 46,Выход эл мента 52 соединен с входом элемента 47, Выходы элементов 46 и 47 соединены с входами элемента 50, выхо которого является выходом 20 перено са блока 1с Блок 5 (фиг, 3) содержит регистр 53 адреса, дешифратор 54 функ.ций, группу триггеров 55 флагов, группу элементов И 56 и 57, деыифрат.ор 58 переходов, элементы ИЛИ 59и И 60 и элемент ИЛИ -62. Элементы 59-61 . образуют группу селекторов К входам 17 управления переходами блока .подключены входы дешифратора 58 и Входы элементов 60. Выходы дешифра торп 58 соединены с входами группы элементов 60 и инверсными входами ;группы элементов 61. Первый выход дешифратора 58 является выходом 24 блока 5, Выходы групп элементов 60 и 61 соединены с входами групп элементов 59, выходы которых подклю чены к информационным входам регист ра 53, Вход 21 б71ока 5 соединен с входом первого элемента И rpynotii элементов 60 и информационными входами группы триггеров 55,, Вход дешифратора 54 является входом 18 бло ка 5. Выходы данифратора 54 соединены с входами группы элементов 56 и 57 о Первый выход дешифратора 54 соединен с входом элемента 62, выход которого является выходом 22 блока 5, К синхровходу 26 бло-ка 5 подключены входы группы элементов 56 и вход занесения регистра 53, вход установки в О ,которого является входом 15 начальной установки блока 5,, йзахода группы элементов 56 соединены с входами занесения группы триггеров 55, выходы которых соединены с входами групп 3JjeMeHTOB 57. Выходы группы элементов 57 соединены с входами элемента 62 „ Выходы регистра 53 являются адресными выходами 16 блока 5 и соединенЕл с входами элементов 61 „ На фиг. 4 показан алгоритм микро™ программы, на примере выполнения которой поясняется принцип работы микропроцессора. Символами Mi обоэначены отд(2льные микрокоманды, а символом А -- проверяемое логическое ус ловив. На временных диаграммах выполнения алгоритма микропрограмг/м приняты следуюш.ие обозначения: 63 - синхроимпульсы на входе 14 микропроцессора; 64 - коды микрокоманд на выходе блока 6; 65 - коды микрокоманд на выходе регистра 7; 66 - сигнал начальной установки на входе 15 микропроцессора; 67 - сигнал на выходе 24 блока 5; 68 - сигнал на выходе триггера 11; 69 - сигнал на выходе элемента 10; 70 импульсы на выходе элемента Э; 71 - сигнал на выходе триггера 12; 72 - импульсы наг выходе элемента 13; 73 - сигнал условия на. входе 21 блока 5 Для приведения микропроцессора в исходное состояние на вход 15 подается сигнал 66 начггльной установки. По этому сигналу регистр 53 ка 5 и триггер 12 устана.вливаются в О, а триггер 11 устанавливается в По нулевому адресу,- у станов ленному на выходе 16 блока 5, из блока 6 выбирается микрокоманда М (64), Операционная часть микрокоманды М поступает на информационный вход регистра7, а адресная часть на вход 17 блока 5, Адресная часть микрокоманды состоит из двух полей- адресного поля и поля управления переходами Сигналы, соответствующие а.дресному полю,, поступают на входы групп.элементов 60, Сигналы, соответствующие полю управлении пёрЪходами, поступают на вход дешифратора 58, В поле управления переходами адресной части микрокоманда Ml задается эезусловный переход к микро команде М2„ Поэтому единичный сигнал вырабатывается на одном из выходов, кроме первого дешифратора 58. Этим сигналом разре;яается прохождение а.цресного поля через одну из групп элементов 60 и 59 на информационные входы регистра 53, Так как на остальных выходах дешифратора 58 присутствуют нулевые сигналы, то элементы 60 остальных групп оказываются закрытыми. На информационные входы регистра 53 через группы элементов 61 и 59 передается код с выхода регистра 53. Таким образом, на информационных входах регистра 53 формируется адрес микрокоманды Так как на упра;вляющем выходе 25 присутствует нулевой сигнал 67,то единичный сигнал 69 поступает на входы триггера 11 и элемента 9, Пр поступлении синхроимпульса 6t3 на вход 14 на выходе элемента 9 вырабтывается импульс 70, Одновременно микрокоманда Ml заносится в конвейерный регистр 7, Однако код микрокоманды Ml (65) появляется на выхо регистра 7 через время t. t определемое временем задержки занесения в регистр 7, На вход 25 блока 1 импульс 72 не поступает, так как элемент 13 закрыт нулевым сигналом 71 с выхода триггера 12, По заднему /фронту синхроимпульса 63 в триггер 11 в соответствии с сигналом .69 заносится , а в триггер 12 в соответствии с сигналом 68 также заносится . В результате этого сигнал 68 не меняет единичного значения, а сигнал 71 принимает единичное значение и открывает элемент 13. По заднему фронту импульса 70 адрес микрокоманды М2 заносится в регистр 53, Однако микрокоманда М2 появляется на выходе блока 6 (64) через время 1, , определяемое временем занесения в регистр 53 и временем выборки из блока 6. В адресной части микрокоманды М 2 задается- условный переход к следующей микрокоманде (по значению условия А). Поэтому единичный сигнал вырабатывается на первом выходе дешифратора 58. Сигнал 67 принимает единичное значение, а адрес следующей микрокоманды формируется в блоке 5 с учетом значения сигнала 73 логического условия, поступающего на вход 21 блока 5, Сигнал 69 на выходе элемента 10 принимает нул вое значение и закрывает элемент 9, При поступлении второго синхроимпульса 63 одновременно с занесением микрокоманды М2 в регистр 7 на выходе элемента 13 вырабатывается импульс 72, По переднему фронту импульса 72 блок 1 начинает выполнение микрокоманды Ml (6.5) , хранимой на регистре .7 р В зависимости от кода микрокоманды блок 1 выполняет арифметико-логические и сдвговые операции. Дешифратор 27 декодирует код микрокоманды и вырабатывает на одном из своих выходов сигнал соответствующего микроприказа.

Арифметико-логические операции выполняются в блоке 1 над двумя операндами, один из которых находится в регистре 39, а другой поступает на информационный вход 2, Причем на -выходе сумматора 28 формируется значение арифметической суммы слагаемых с учетом значения входного переноса, сигнал которого поступает на вход 23 блока 1. Если при этом

0 происходит переполнение разрядной . сетки сумматора 2.8, то на выходе пе реноса сумматора 28 вырабатывается единичный сигнал и поступает на информационный вход триггера 51, На выходах элементов 29 формируется

5 конъюкция, а на выходах элементов 30 - дизъюнкция операндов. Кроме того, на выходах элементов 31 формируется инверсное значение кода, содержащегося в регистре 39,По

0 единичному сигналу с одного из йыходов дешифратора 27 значение результата операции поступает через одну из групп элементов 32-36 и группу элементов 37 на информацион5ные входы счетчика 38 и регистра 39, По переднему фронту импульса с выхода одного из элементов 40-45 производятся различные действия со счетчиком 38 и регистром 39 (установка

0

О

занесение, сдвиг, прибавв

ление к содержимому). На выходе элемента 9 импульс 70 не вырабатывается, вследствие чего на выходе 16 блока 5 сохраняется адрес

5 микрокоманды М2. По заднему фронту второго синхроимпульса 63 триггер 11 устанавливается в О , в результате чего сигнал 69 принимает единичное значение и открывает элемент 9, Триггер 12 не изменяет единичного состояния. При поступлении третьего синхроимпульса 63 микрокоманда М2 опять заносится в регистр 7 (65), Одновременно по переднему фронту импульса 72 блок 1 выполняет микро5команду М2, в результате чего формируется значения сигнала 73 логического условия. По адресной части микрокоманды М2 и значению логического условия в блоке 5 формируется

0 адрес микрокоманды МЗ или М4. Например, по единичному значению сигнала 73 условия в блоке формируется адрес микрокоманды М4, По заднему фронту третьего синхроимпульса 63

5 триггер 11 устанавливается в , а триггер 12 в О, Сигнал 71 с его выхода закрывает элемент 13, .По заднему фронту импульса 70 блок 5 выдает на выход 16 адрес микрокоман0ды М4, Микрокоманда М4 выбирается из блока 6 (64), Так как в адресной части микрокоманды М4 задается безусловный переход к микрокоманде М5, сигнал 67 принимает нулевое значе5 нив, вследствие чего сигнал 69 принимает единичное .значение. По четвертому синхроимпульсу 63 микрокоманда М4 заносится в регистр 7 (65), На выходе.элемента 13 импульс 72 не вырабатывается, чем предупреждается повторное выполнение блоком 1 йикрокоманды М2. По заднему фронту четвертого синхроимпульса 63 триггер 12 устанавливается в , а триггер 11 не меняет единичного состояния. По заднему фронту импульса 70 блок 5 выдает адрес микрокоманды МБ, вследствие чего микрокоманда М5 выбирается из блока 6. При поступлении следующего синхроимпульса 63 микрокоманда М5 заносится в регистр 7, блок 1 выполняет микрокоманду М4, а блок 5 формирует адрес следующей микрокоманды и т.д. При вЕлполненин многих операций блок 1 обращается к блоку внешней памяти или внешнему устройству, выставляя на адресный выход 3 микрогфоцессора соответствующий адрес. Блок внешней памяти и внешние устройства, с которыми взаимодействует микропроцессор, не показаны. Если необходимо записать информацию в блок внешней памяти или внешнее устройство, что указывается в микрокоманде, на управляющем выходе 8 микропроцессора устанавливается сигнал, соответствующий режиму записи. Записываемые данные из блока 1 выдаются на информационный выход 4. При чтении информации из блока внешней памяти или внешнего устройства на yпpaвJlяющий выход 8 поступает сигнал чтения, а считываемые данные передаются в блок 1 с информационного входа 2, Код, поступающий с первого выхода регистра 7 на вход 18 блока 5, определяет функцию управления логикой флагов, которая 4 - I ™-..rTi..JL. ™-t

заключается либо в установ-лении выбранного флага в соответствии со значением сигнала на. входе 21 блок.а 5, либо в выдаче содержимого выбранного флага или значений О и на выход 22 блока 5. Работа блока 5 при этом заключается в следутацем. В соответствии с кодом,поступающим на вход 18. блока 5, на одном из выходов дешифратора 54 вырабатывается управляющий сигнал. Если производится установка одного из триггеров 55, то по единичному сигналу с выхода дешифратора 54 . открывается один из.элементов 56.

5 При поступлении синхроимпульса на вход 26 блока 5 на выходе элемента 56 вырабатывается импульс, по заднему фронту которого п соответствующий триггер .ЬЬ заносится значение сигнала на входе 21. блока 5. Если значение одного из триггеров 55 выдается на выход 22 блока 5, то по единичному сигналу с выхода дешифратора. 54 открывается один из

5 элементов 57 и содержимое триггера 55 поступает через элементы 57 и 62 на выход 22 блока,

Таким образом, предлагаемый n микропроцессор позволяет выполнять условные переходы в микропрограмме без использования холостых

микрокоманд,

Учитывая, что в реальных микропрограммах условный переход приходится в среднем на каждые 5-7 вы.полняемых микрокоманд, то использование предлагаемого микропроцессора позволяет сэкономить в среднем 0 15-20% дорогостоящей микропрограммной памяти (с 650 до 500 микрокоманд) . ,,,

и

IB i6. f6

n

д)иеЛ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Прангишвили и.В | |||

| Микропроцессоры и микро-ЭВМ | |||

| М., Энергия, 1979, с | |||

| Огнетушитель | 0 |

|

SU91A1 |

Авторы

Даты

1983-09-30—Публикация

1982-02-12—Подача