входом регистра адреса, первый, и третий входы .и выход элементов ИЛИ группы подключены соответственно к аыходам элементов И первой, вто рой VI третьей групп и информационному входу регистра адреса, выход котс ого соединен с адресным выходом блока, вход, первый, второй и третий выходы дешифратора переходов подклю чаны соответственно к входу управления переходами блока, первому входу второго элемента ИЛИ и первым входам элементов И второй и третьей групп, вторые входы которых соединены с входом управления переходам11 блока, третиФ1 вход элементов И третьей группы подключен к входу признаков блока, а третий выход дешифратора переходов соединен с управляющим выходом блока, второй вход второго элемента ИЛИ и инверсные входы элементов И второй и третьей групп

подключены к входу начальной установ ки блока, а первый и второй входы элементов И первой группы соединены соответственно с информационным входом блока и выходом второго элемента ИЛИ, информационные входы, синхроеходы и выходы триггеров группы подключены соответственно к входу признаков блока, выходам соответствующих элементов И четвертой группы соединены с синхровходом блока, вход и выходы дешифратора функций подключены соответственно к входу дешифрации флагов блока и вторым входам соответствующих элементов И четвертой и пятой групп, входы третьего элемента ИЛИ соединены с одним из выходов дешифратора функций и выходами элементов И пятой группы, а выход третьего элемента ИЛИ подключен к выходу признаков бло- . ка.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1982 |

|

SU1035610A1 |

| Микропроцессор | 1982 |

|

SU1045231A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Микропроцессор | 1985 |

|

SU1290340A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

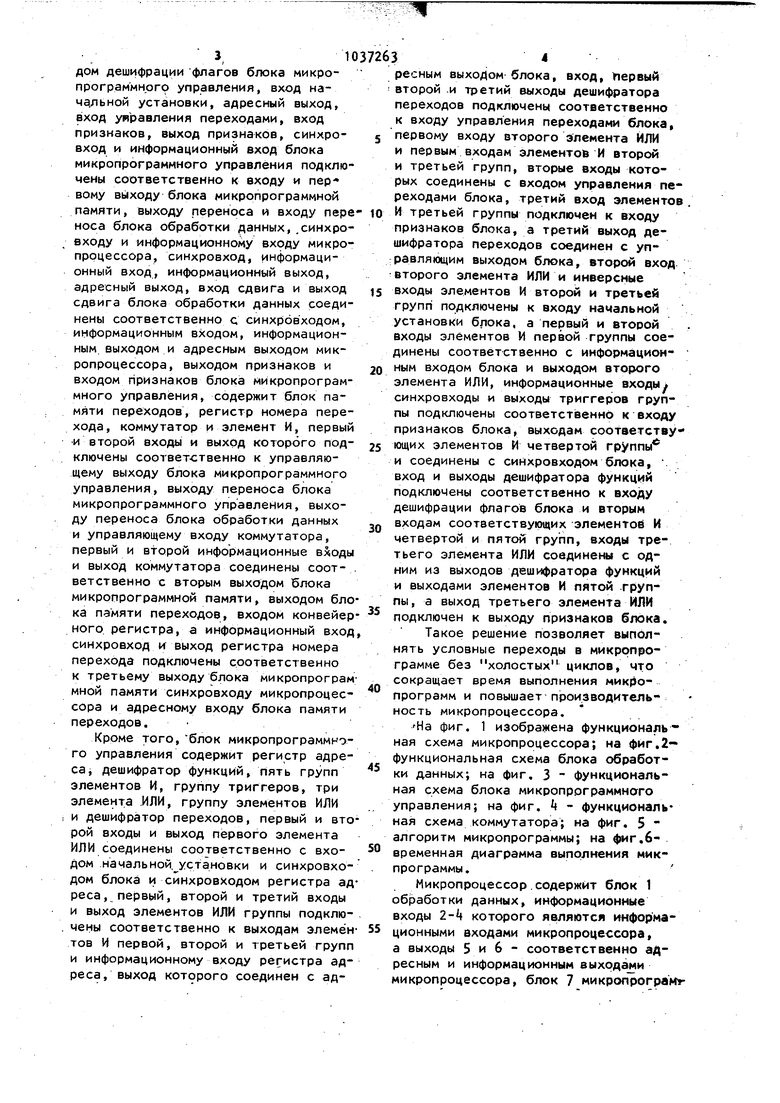

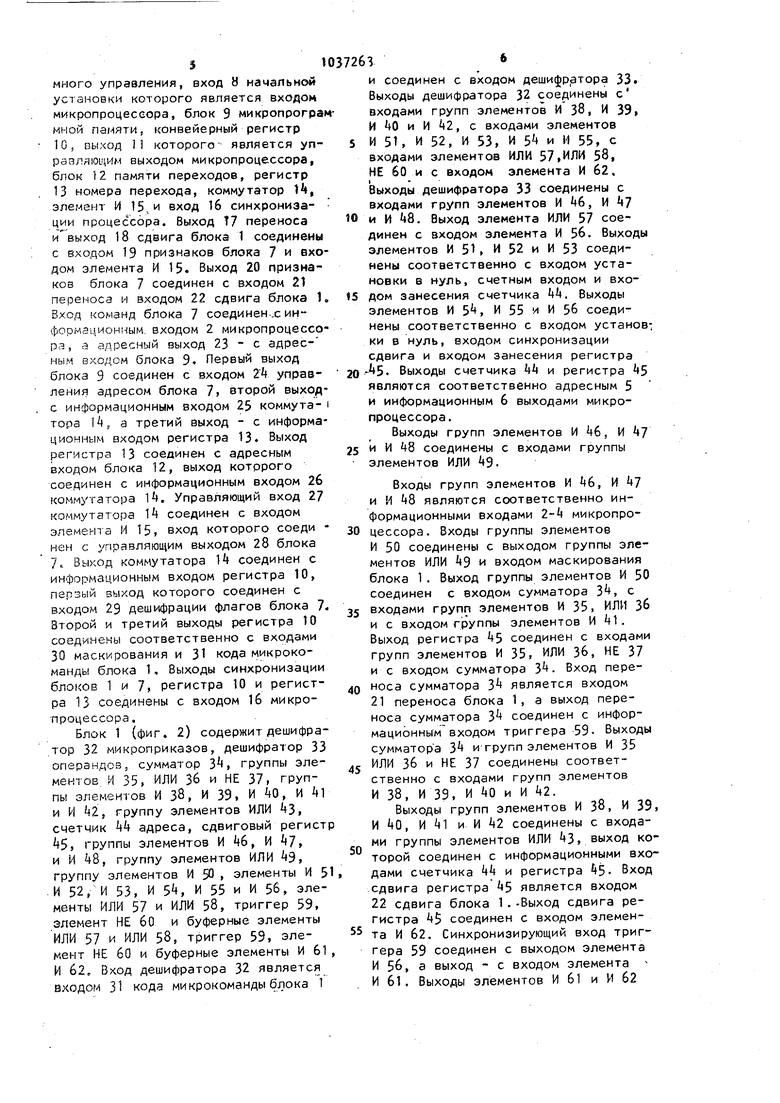

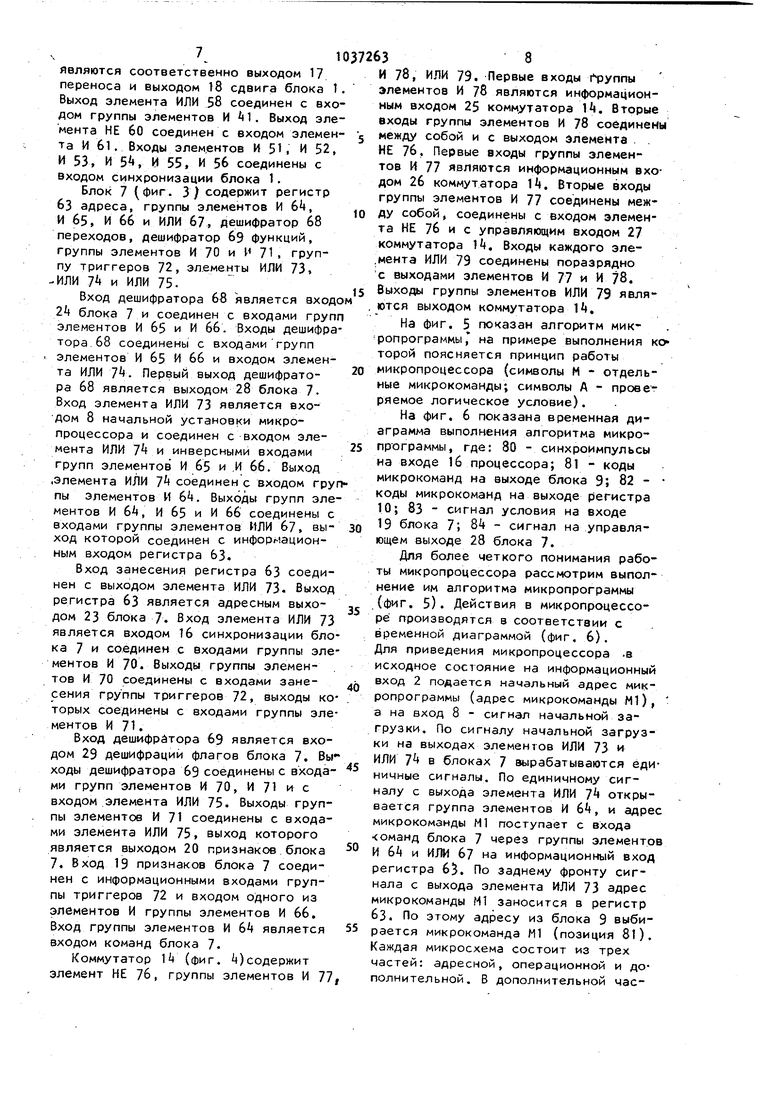

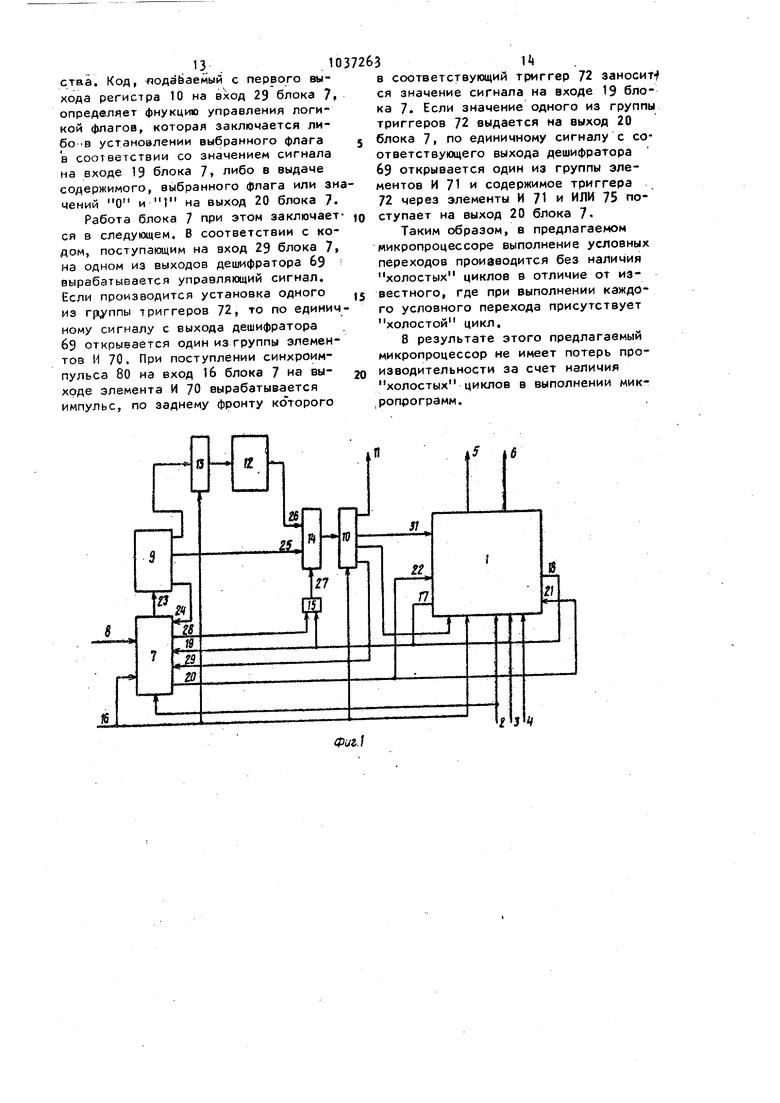

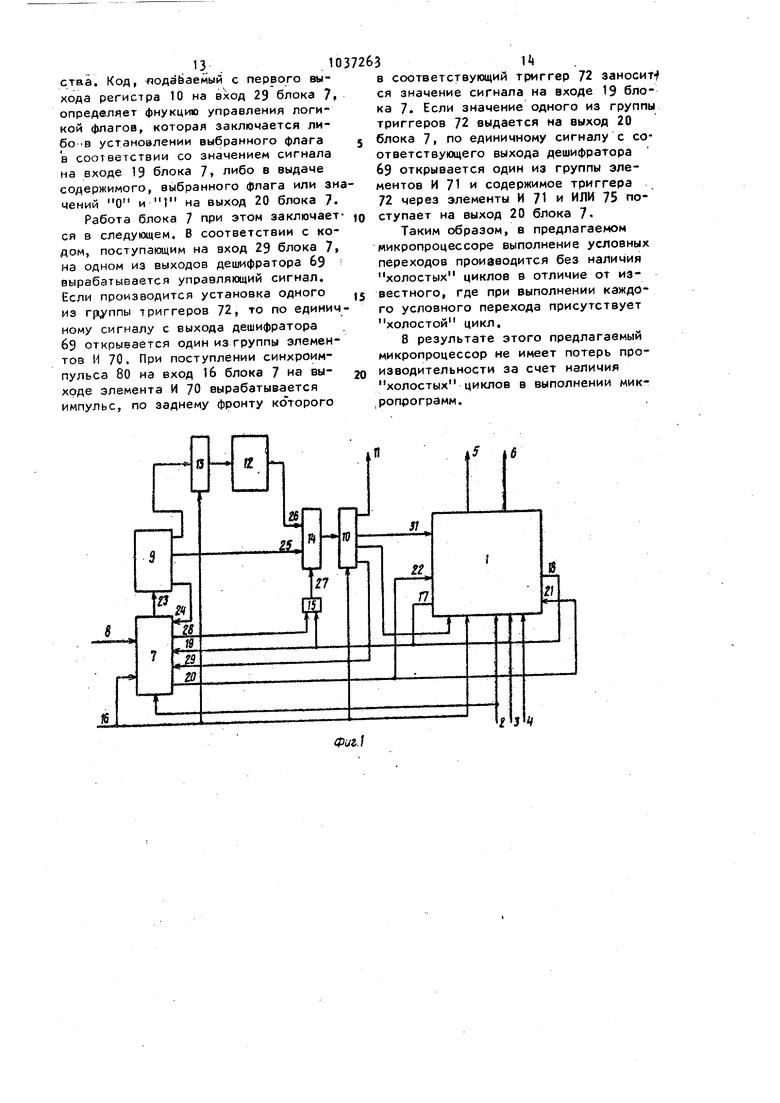

1. МИКРОПРОЦЕССОР, содержащий блок обработки данных, блок микропрограммного управления, блок микропрограммной памяти и конвейерный регистр, синхровход, первый, второй, третий и четвертый выходы которого соединены соответственно с синхровходом и управляющим выходом микропроцессора, входом кода микрокоманды и входом маскирования блока обработки данных и входом дешифрации флагов блока микропрограммного управления, вход начальной установки, адресный выход, .вход управления переходами, вход признаков, выход признаков, синхровход и информационный вход блока микропрограммного управ- . ления подключены соответственно к входу и первому выходу блока микропрограммной памяти, выходу переноса и входу переноса блока обработки данных, синхровходу и информационному входу микропроцессора, синхровход, информационный вход, информационный выход, адресный выход, вход, сдвига и выход сдвига блока обработки данных соединены соответственно с сиихровходом, информационным входом, информационным выходом и адресным выходом микропроцессора, выходом признаков и входом признаков блока микропрограммного управления, отличающийся тем, что, с целью повышения производительности,. он содержит блок памяти переходов, регистр номера перехода, коммутатор и элемент И, первый и второй входы и выход которого подключены соответственно к управляющему выходу блока микропрограммного управления, выходу переноса блока микропрограммного упi (О равления, выходу переноса блока обработки данных и управляющему входу коммутатора, первый и второй инфорс мационные входы и выход коимутвтора соединены соответственно с вторым вы§ .ходом блока микропрограммной памяти, выходом блока памяти переходов, входом конвейерного регистра, а информационный вход, синхровход и выход ре00 гистра номера перехода подключены м соответственно к третьему выходу N9 блока микропрограммной памяти, синхО ровходу микропроцессора и адресному СО входу блока памяти переходов. 2, Микропроцессор по п. 1, отличающийся тем, что, блок микропрограммного управления содержит регистр адреса, дешифратор функций, пять групп элементов И, группу триггеров, три элемента ИЛИ группу элементов ИЛИ и дешифратор переходов, первый и вторЬй входы и выход первого элемента ИЛИ соединены соответственно с входом начальной установки и си нхровходом блока и синхро

Изобретение относится к вычислительной технике и может быть исполь зовано для обработки данных в системах управления.

Известен микропроцессор, содержащий центральный блок обработки данных, блок микропрограммного управления, блок микропрограммной памяти, конвейерный регистр, два регистра и элемент НЕ l .

Недостатком данного микропроцессора является низкая производительность вследствие того, что при выполнении каждого условного перехода непроизводительно тратится один микрокомаидный цикл.

Наиболее близким к изобретению по технической сущности является микропроцессор, содержащий центральный блок обработки данных, блок микропрограммного управления, конвейерный регистр и блок микропрограммной памяти ,

В известном микропроцессоре используется конвейерный принцип выполнения микрокоманд, который заключается в том, что в одном микрокомандном цикле одновременно с выполнением текущей микрокоманды, находящей-.

ся на конвейерном регистре, производится выборка следующей микрокоманды. При этом выборка микрокоманды опережает на цикл ее выполнение. Однако при выполнении условных переходов следующая после условного перехода микрокоманда выбирается раньше, чем формируется логическое условие, определяющее направление перехода. Поэтому при каждом условном переходе в микропрограмме предусматривается холостая микрокоманда выполняющая функцию задержки на один цикл. Наличие холостых циклов при выполнении микропрограмм снижает производительность микропроцессора.

Цель изобретения - повышение производительности.

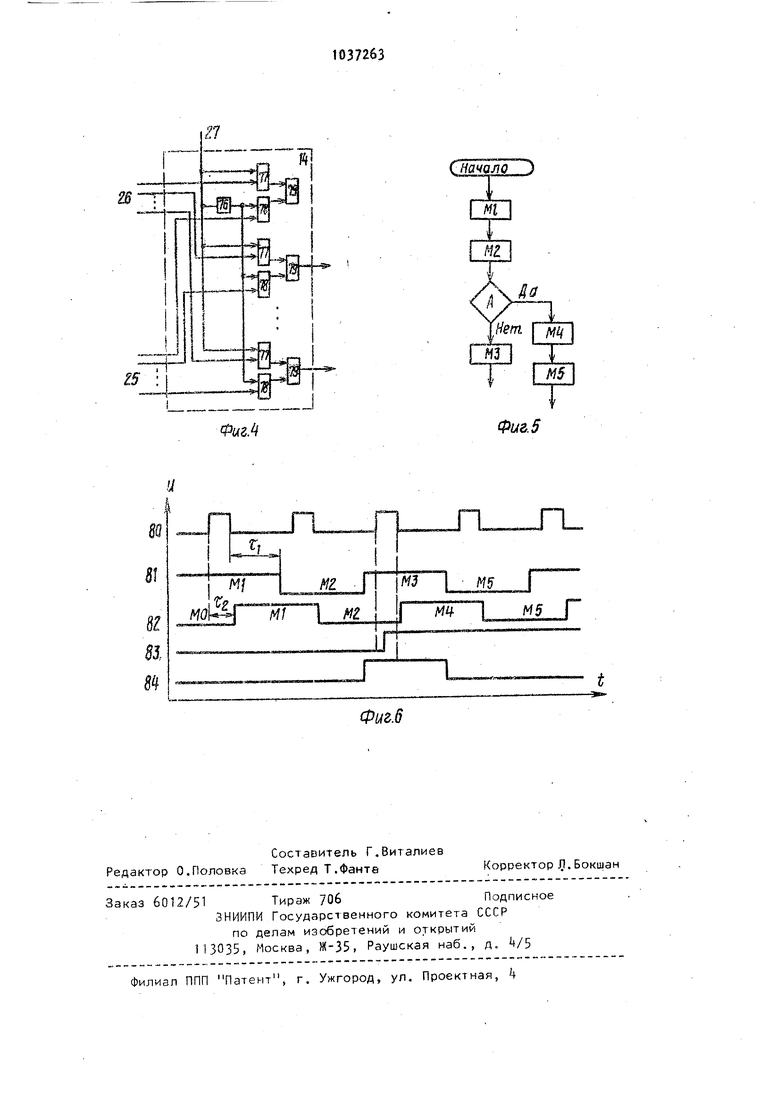

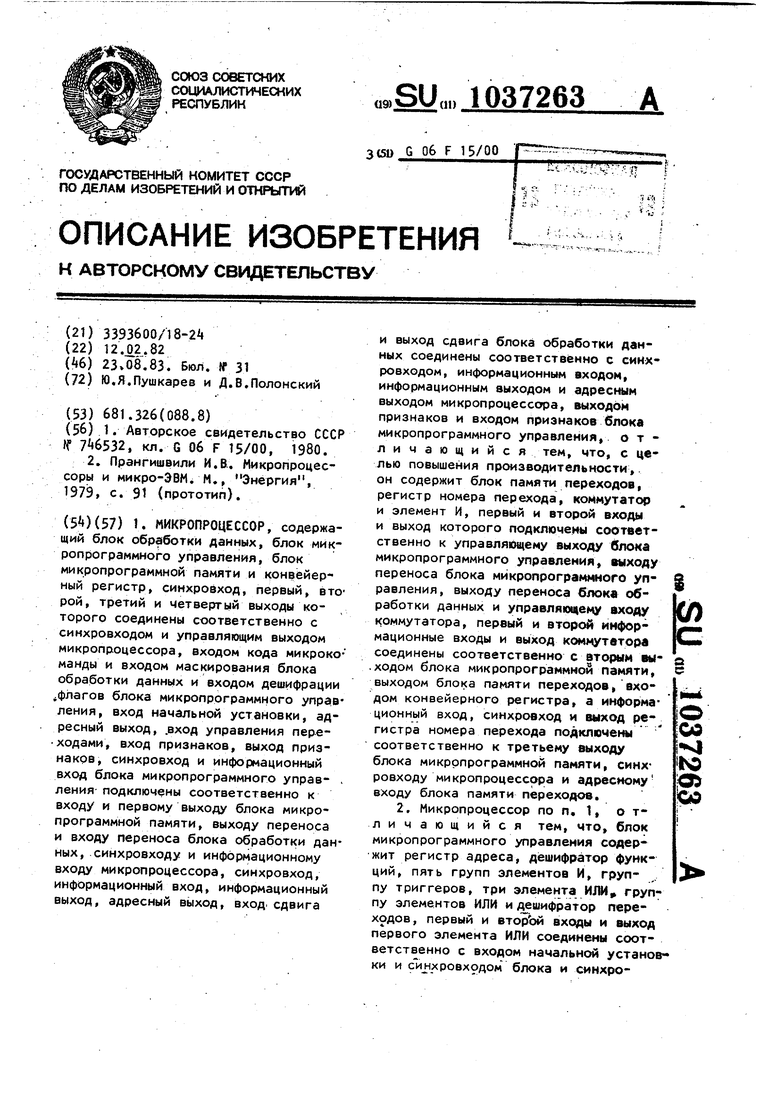

Цель достигается тем, что микропроцессор, содержащий блок обработки данных, блок микропрограммного управления, блок микропрограммной памяти и конвейерный регистр, синхровход, первый, второй, третий и четвертый выходы которого соединены соответственно с синхровходом и управляющим выходом микропроцессора, входом кода микрокоманды и входом маскирования блока обработки данных и входом дешифрации флагов блока микропрограммного управления, вход нач льной установки, адресный выход, вход управления переходами, вход признаков, выход признаков, синхровход и информационный вход блока микропрограммного управления подключены соответственно к входу и первому выходу блока микропрограммной памяти, выходу переноса и входу пере носа блока обработки данных,,синхровходу и информационному входу микропроцессора, синхровход, информационный вход, информационный выход, адресный выход, вход сдвига и выход сдвига блока обработки данных соединены соответственно с синхровходом, информационным входом, информационным, выходом и адресным выходом микропроцессора, выходом признаков и входом признаков блока микропрограммного управления, содержит блок памяти переходов, регистр номера перехода, коммутатор и элемент И, первый и второй входы и выход которого подключены соответственно к управляющему выходу блока микропрограммного управления, выходу переноса блока микропрограммного управления, выходу переноса блока обработки данных и управляющему входу коммутатора, первый и второй информационные входы и выход коммутатора соединены соответственно с вторым выходом блока микропрограммной памяти, выходом бло ка памяти переходов, входом конвейер ного, регистра, а информационный вход синхровход и выход регистра номера перехода подключены соответственно к третьему выходу блока микропрограм мной памяти синхровходу микропроцес сора и адресному входу блока памяти переходов. Кроме того, блок микропрограммного управления содержит регистр адреса дешифратор функций, пять групп элементов И, группу триггеров, три элемента .ИЛИ, группу элементов ИЛИ и дешифратор переходов, первый и вто рой входы и выход первого элемента ИЛИ соединены соо7ветственно с входом .начальной, установки и синхровходом блока и синхровходом регистра ад реса, первый, второй и третий входы и выход элементов ИЛИ группы подключены соответственно к выходам элемён тов И первой, второй и третьей групп и информационному входу регистра адреса, выход которого соединен с адресным выходом блока, вход, 1ервыЙ второй .и третий выходы дешифратора переходов подключены соответственно к входу управления переходами блока, первому входу второго элемента ИЛИ и первым входам элементов И второй и третьей групп, вторые входы которых соединены с входом управления переходами блока, третий вход элементов. И третьей группы подключен к входу признаков блока, а третий выход дешифратора переходов соединен с управляющим выходом блока, второй вход. второго элемента ИЛИ и инверсные входы элементов И второй и третьей групН подключены к входу начальной установки блока, а первый и второй входы элементов И первой группы соединены соответственно с информационным входом блока и выходом второго элемента ИЛИ, информационные входы синхровходы и выходы триггеров группы подключены соответственно к входу признаков блока, выходам cooteeTCTsyющих элементов И четвертой группы и соединены с сийхровходом блока, вход и выходы дешифратора функций подключены соответственно к входу дешифрации флагов блока и вторым входам соответствующих элементов И четвертой и пятой групп, входы третьего элемента ИЛИ соединены с одним из выходов дешифратора функций и выходами элементов И пятой группы , а выход третьего элемента ИЛИ подключен к выходу признаков блока. Такое решение позволяет выполнять условные переходы в микропрограмме без холостых циклов, что сокращает время выполнения микропрограмм и повышает производительность микропроцессора. На фиг. 1 изображена функциональ ная схема микропроцессора; на фйг,2- функциональная схема блока обработки данных; на фиг. 3 - функциональная схема блока микропрограммного управления; на фиг. k - функциональная схема коммутатора; на фиг. 5 алгоритм микропрограммы; на фиг.6временная диаграмма выполнения микпрограммы. Микропроцессор .содержит блок 1 обработки данных, информационные входы 2-k которого являются информационными входами микропроцессора, а выходы 5 и 6 - соответственно адресным и информационным выходами микропроцессора, блок 7 микропрограмтг 5 много управления, вход 9 начальной установки которого является входом микропроцессора, блок 9 микропрогра мной памяти, конвейерный регистр 10, выход 11 которого- является управляющим выходом микропроцессора, блок 12 памяти переходов, регистр 13 номера перехода, коммутатор Н, элемент И 15,и вход 16 синхронизации процессора. Выход Т7 переноса и выход 18 сдвига блока 1 соединены с входом 19 признаков блока 7 и вхо дом элемента И 15. Выход 20 признаков блока 7 соединен с входом 21 переноса и входом 22 сдвига блока 1 Вход команд блока 7 соединен-.с информационным, входом 2 микропроцессо ра, а адресный выход 23 - с адресHbiM входом блока 9. Первый выход блока 9 соединен с входом 2Ц управлеНия адресом блока 7 второй выход с информационным входом 25 коммутатора И,, а третий выход - с информа ционным входом регистра 13. Выход регистра 13 соединен с адресным входом блока 12, выход которого соединен с информационным входом 26 коммутатора l4. Управляющий вход 27 коммутатора 1 соединен с входом элемента И 15, вход которого соеди иен с угфавляющим выходом 28 блока 7. Выход коммутатора Н соединен с информационным входом регистра 10, перзый выход которого соединен с входом 29 дешифрации флагов блока 7 Второй и третий выходы регистра 10 соединены соответственно с входами 30 маскирования и 31 кода микрокоманды блока 1, Выходы синхронизации блоков 1 и 7, регистра 10 и регистра 13 соединены с входом 16 микропроцессора. Блок 1 {фиг. 2) содержит дешифратор 32 микроприказов, дешифратор 33 операндов, сумматор 3 группы элементов И 35, ИЛИ 36 и НЕ 37, группы элементов И 38, И 39, И tO, И 41 и И 42, группу элементов ИЛИ 3, счетчик kk адреса, сдвиговый регист 5( группы элементов И 46, И 7, и И 48, группу элементов ИЛИ 49, группу элементов И 50 , элементы И 5 И 52, И 53, И 54, И 55 и И 56, элементы ИЛИ 57 и ИЛИ 58, триггер 59, элемент НЕ 60 и буферные элементы ИЛИ 57 и ИЛИ 58, триггер 59, элемент НЕ 60 и буферные элементы И 61 И 62. Вход дешифратора 32 является входом 31 кода микрокоманды блока 1 3 и соединен с входом дешифратора 33. Выходы дешифратора 32 соединены с входами групп элементов И 38, И 39, И 40 и И 42, с входами элементов И 51, И 52, И 53, И 54 и И 55, с входами элементов ИЛИ 57,ИЛИ 58, НЕ 60 и с входом элемента И 62. Выходы дешифратора 33 соединены с входами групп элементов И 46, И 47 и И 48. Выход элемента ИЛИ 57 соединен с входом элемента И 56. Выходы элементов И 51, И 52 и И 53 соединены соответственно с входом установки в нуль, счетным входом и входом занесения счетчика 44. Выходы элементов И 54, И 55 и И 5б соединены соответственно с входом установки в нуль, входом синхронизации сдвига и входом занесения регистра -45. Выходы счетчика 44 и регистра 45 являются соответственно адресным 5 и информационным 6 выходами микропроцессора. Выходы групп элементов И 46, И 47 и И 48 соединены с входами группы элементов ИЛИ 49. Входы групп элементов И 46, И 47 и И 48 являются соответственно информационными входами 2-4 микропроцессора. Входы группы элементов И 50 соединены с выходом группы элементов ИЛИ 49 и входом маскирования блока 1. Выход группы элементов И 50 соединен с входом сумматора 34, с входами групп элементов И 35, ИЛИ Зб и с входом г эуппы элементов И 41. Выход регистра 45 соединен с входами групп элементов И 35, ИЛИ Зб, НЕ 37 и с входом сумматора 34. Вход переноса сумматора 34 является входом 21переноса блока 1, а выход переноса сумматора 34 соединен с информационным входом триггера 59. Выходы сумматора 34 и групп элементов И 35 ИЛИ Зб и НЕ 37 соединены соответственно с входами групп элементов И 38, И 39, И 40 и И 42. Выходы групп элементов И 38, И 39, И 40, И 41 и И 42 соединены с входами группы элементов ИЛИ 43, выход которой соединен с информационными входами счетчика 44 и регистра 45- Вход сдвига регистра 45 является входом 22сдвига блока 1. -Выход сдвига регистра 45 соединен с входом элемента И 62. Синхронизирующий вход триггера 59 соединен с выходом элемента И 5б, а выход - с входом элемента И б1. Выходы элементов И 61 и И 62 1 являются соответственно выходом 1 переноса и выходом 18 сдвига блока t Выход элемента ИЛИ 58 соединен с входом группы элементов И 1, Выход элемента НЕ 60 соединен с входом элемента И 61, Входы элементов И 51i И 52, И 53, И 5, И 55, И 56 соединены с Входом синхронизации блока 1. Блок 7 (фиг. 3J содержит регистр 63 адреса, группы элементов И , И 65, И 66 и ИЛИ 67, дешифратор 68 переходов, дешифратор 69 функций, группы элементов И 70 и И 71, группу триггеров 72, элементы ИЛИ 73, -ИЛИ 7 и ИЛИ 75. Вход дешифратора 68 является входо 2 блока 7 и соединен с входами групп элементов И 65 и И 66. Входы дешифра тора. 68 соединены с входамигрупп элементов И б5 И 66 и входом элемента ИЛИ J. Первый выход дешифратора 68 является выходом 28 блока 7. Вход элемента ИЛИ 73 является вхоДом 8 начальной установки микропроцессора и соединен с входом элемента ИЛИ 7 и инверсными входами групп элементов И б5 и ,И 66. Выход .Элемента ИЛИ 7 соединен с входом гру пы элементов И 64. Выходы групп эле ментов И 64, И б5 и И 66 соединены с входами группы элементов ИЛИ 67, выход которой соединен с инфорг- ационным входом регистра 63. Вход занесения регистра 63 соединен с выходом элемента ИЛИ 73. Выход регистра 63 является адресным выходом 23 блока 7. Вход элемента ИЛИ 73 является входом 16 синхронизации бло ка 7 и соединен с входами группы эле ментов И 70. Выходы группы элементов И 70 соединены с входами занесения группы триггеров 72, выходы ко торых соединены с входами группы эле ментов И 71. Вход дешифратора 69 является входом 29 дешифраций флагов блока 7. Вы ходы дешифратора 63 соединены с входами групп элементов И 70, И 71 и с входом .элемента ИЛИ 75. Выходы группы элементов И 71 соединены с входами элемента ИЛИ 75, выход которого является выходом 20 признаков.блока 7, Вход 19 признаков блока 7 соединен с информационными входами группы триггеров 72 и входом одного из элементов И группы элементов И 66. Вход группы элементов И 64 является входом команд блока 7. Коммутатор 14 (фиг. 4)содержит элемент НЕ 76, группы элементов И 77 38 И 73, ИЛИ 79. Первые входы Группы элементов И 78 являются информационным входом 25 коммутатора 14. Вторые входы группы элементов И 78 соединены между собой и с выходом элемента . . НЕ 76, Первые входы группы элементов И 77 являются информационным входом 26 коммутатора 14. Вторые входы группы элементов И 77 соединены между собой, соединены с входом элемента НЕ 7б и с управляющим входом 27 коммутатора 14. Входы каждого элемента ИЛИ 79 соединены поразрядно с выходами элементов И 77 и И 78. Выходы группы элементов ИЛИ 79 являются выходом коммутатора 14. На фиг. 5 показан алгоритм микропрограммы, на примере выполнения ко торой поясняется принцип работы микропроцессора (символы М - отдельные микрокоманды; символы А - проверяемое логическое условие). На фиг. 6 показана временная диаграмма выполнения алгоритма микропрограммы, где: 80 - синхроимпульсы на входе 16 процессора; 81 - коды микрокоманд на выходе блока 9; 82 - коды микрокоманд на выходе регистра 10; 83 - сигнал условия на входе 19 блока 7; 84 - сигнал на управляющем выходе 28 блока 7. Для более четкого понимания работы микропроцессора рассмотрим выполнение им алгоритма микропрограммы .(фиг. 5). Действия в микропроцессоре производятся в соответствии с временной диаграммой (фиг. 6). Для приведения микропроцессора .в исходное состояние на информационный вход 2 подается начальный адрес микропрограммы (адрес микрокоманды Ml), а на вход 8 - сигнал начальной загрузки. По сигналу начальной загрузки на выходах элементов ИЛИ 73 и ИЛИ 74 в блоках 7 вырабатываются единичные сигналы. По единичному сигналу с выхода элемента ИЛИ 74 открывается группа элементов И 64, и адрес микрокоманды Ml поступает с входа команд блока 7 через группы элементов И 64 и И1Ы б7 на информационный вход регистра 65. По заднему фронту сигнала с выхода элемента ИЛИ 73 адрес микрокоманды Ml заносится в регистр 63. По этому адресу из блока 9 выбирается микрокоманда Ml (позиция 81), Каждая микросхема состоит из трех частей: адресной, операционной и дополнительной. В дополнительной части микрокоманды указывается номер условногоперехода в микропрограмме. Разрядность (Р) этой части микро команды определяется выражением . где N - общее число условных перехо дов в микропрограмме. Дополнительная часть микрокоманды поступает на информационный вход регисгра Операционная часть микрокоманды поступает на вход 25 комму таторз Н, а адресная часть микрокоманды - на вход 2 управления адресом блока 9. Адресная часть микрокоманды состоит из двух полей-- адреснего пбяя и поля переходов. Сигналы соответствующие адресному полю, по ступают на входы групп элементов И 65 и И 66. Сигналы, соответствующие полю переходов, поступают на вход дешифратора 68. В поле переходов адресной части микрокоманды Ml задается безусловный переход к микрокоманде М2. Поэтому единичным сигналом с выхода дешифратора 68 открывается группа элементов М 65 и И 66 Сигналы, соответствующие полю перехо дов, поступают на вход дешифратора 68. В поле переходов адресной части микрокоманды М1 задается безу словный переход к микрокоманде М2. Поэтому единичным сигналом с выхода дешифратора 68 открывается группа элементов И 65 и адресное поле микрокоманды поступает через группы элементов И 65 и ИЛИ 67 на информаци онный вход регистра 63. Так как элемент И 15 закрыт нулевым сигналом 84, го на входе 27 коммутатора 1 присутствует нулевой сигнал. При этом группа элементов И 77 оказывается закрытой, а группа элементов И 78 открыта единичным сигналом с выхода элемента НЕ 76- В результате на информационный вход регистра 10 передается операционная часть микрокоманды Ml. При поступлении первого синхроимпульса 80 rta вход 16 производятся следующие действия. При возникнозении переднего фронта синхроимпульса 80 блок 1 начинает выполнение микрокоманды МО (позиция 82), хранимой на конвейерном регистре 10. Одновременно микрокоманда Ml начинает заноситься в конвейерный регистр 10, однако код этой микрокоманды появля63 . ется на выходе регистра 10 через время Со . определяемое задержкой, занесения информации в регистр 10. В начальный момент времени в регистре 10 хранится микрокоманда МО, код которой сформировался несмпределеиным образом после включения устройства. Поэтому выполнение этой микрокоманды не производит никаких полезных действий. Это связано сконвейерным принципом выполнения микропрограммы. Так как выборка микрокоманды опережает на цикл ее выполнение, первая микрокоманда микропрограммы может быть выполнена только во втором микрокомандном цикле. Поэтому первый микрокомандный цикл всегда является холостым .в зависимости от управляющего слова, поступающего на вход 31, блок 1 выполняет арифметико-логические и сдвиговые операции. Управляющее слово.состоит из двух полей - поля операций и поля операндов. Сигналы, соответствующие полю операции, поступают на вход дешифратора 32. Сигналы, соответствующие полю операндов, поступают на ., вход дешифратора 33. Дешифратор 32 вырабатывает на одном из своих выходов сигналомикроприказа, соответствующий определенной операции. Арифметико-логические операции в блоке 1 выполняются над двумя операндами. Один из них находится в регистре 5, а второй поступает на один из информационных входов 2- микропроцессора. Дешифратор З вырабатывает на одном из своих выходов единичный сигнал, по которому открывается одна из групп элементов И i+6, И 7 и И i«8. В результате этого операнд с соответствующего информационного входа поступает для дальнейшей обработки через группу элементов ИЛИ 49 и группу элементов И 50. На выходе сумматора 34 формируется значение арифметической суммы слагаемых с учетом значения сигнале входного пере- , носа. Если при этом происходит переполнение сетки сумматора 34, ( то на выходе переноса вырабатывается единичный сигнал. На выходе группы операционных элементов И 35 формируется конъюнкция, а на выходе группа операционных элементов ИЛИ 36изъюнкция операндов. На выходе группы операционных элементов НЕ 37 фopмиf руется инверсное значение кода, содержащегося s регистре 5. По едини ному сигналу с одного из выходов дешифратора 32 значение результата операции поступает через одну из. групп элементов И 38, И 39, И tO, И 1, : И k2 и группу элементов ИЛИ 3 на информационные входы счетчика и регистра 45. По переднему фронту импульса с выхода одного из управляющих элементов И 51, И 52 И 53, И 54, И 55 И 56 производятся различные действия со счетчиком 44 и регистром 45 (установка в нуль, занесение, сдвиг, прибавление единицы, к содержимому). По заднему фронту синхроимпульса 80 адрес микрокоманды М2 заносится в регистр 63, а дополнительная.часть микрокоманды - в регистр 13. Микрокоманда М2 появляется на выходе блока 9 (позиция 81) через время t определяемое временем занесения в регистр 63 и временем выборки из блока 9. В дополнительной части мик рокоманды М2 указывается номер усло ного перехода А в микропрограмме. В адресной части микрокоманды М2 зада ется безусловный переход в .микрокоманду МЗ. При поступлении второго синхроимпульса 80 блок 1 выполняет микрокоманду Ml (позиция 82), а мик рокоманда М2 заносится в регистр10 По адресной части микрокоманды М2 блок 7 формирует адрес микрокоманды МЗ, номер перехода по условию А заносится в регистр 13. Из блока 9 вы бирается микрокоманда МЗ ( позиция 8 а из блока 12 выбирается операционная часть микрокоманды М4. В адресной части микрокоманды МЗ задается выполнение условного перехода.Поэтому единичным сигналом с выхода дешифратора 68 открывается группа элементов И 66, в результате чего адрес следующей микрокоманды формируется с учетом значения сигнала ус ловия на входе 19 блока 7. Сигнал 84 принимает единичное значение, вследствие чего открывается элемент И. 5. При поступлении третьего синх роимпульса 80 блок 1 выполняет микрокоманду М2 (позиция 82), в резуль тате чего формируется значение си1- нала 83 условия. Так как сигнал 83 принимает единичное значение ( условие выполняется ), на управляющем входе 27 комму.татора 14 устанавливается единичный сигнал. По этому сигналу комму-|атор 14 подключает на ин рмационный вход регистра 10 операционную часть микрокоманды М4 с выхода блока 12. Микрокоманда М4 заносится в регистр 10. По адресной части микрокоманды МЗ и единичному значению сигнала 83 условия блок 7 формирует адрес микрокоманды М5, которая затем выбирается из блока 9 ( позиция 81). В адресной части микрокоманды М5 задается безусловный переход к следующей микрокоманде. Поэтому сигнал 84 принимает нулевое значение, вследствие чего закрывается элемент И 15. Коммутатор 14 подключает на информационный вход регистра 10 операционную часть микрокоманды М5 с выхода блока 9. При поступлении четвертого синхроимпульса 80 блок 1 выполняет микрокоманду М4 (позиция 82),микрокоманда М5 заносится в регистр 10, а по ее адресной части блок 7 формирует адрес следующей микрокоманды и т.д. Если сигнал 83 условия в результате выполнения микрокоманды М2 по третьему синхроимпульсу ВО принимает нулевое значение (условие не выполняется),то коммутатор 14 подключает на вход регистра 10 операционную часть микрокоманды МЗ с выхода блока 9. Блок 7 по адресной части микрокоманды МЗ и нулевому значению условия формирует адрес следующей микрокоманды этой ветви и работа микропроцессора продолжается аналогично. При выполнении многих операций блок 1 обращается к блоку внешней памяти или внешнему устройству, выставляя на выход 5 микропроцессора соответствующий адрес. Блок внешней памяти и внешние устройства, с которыми взаимодействуют микропроцессор, на фиг. 1 не показаны.. Если необ ходимо записать информацию а.блок . внешней памяти или внешнее устройство, что указывается в текущей микрокоманде, на управляющем выходе 11 устанавливается сигнал, соответствующий режиму записи. Записываемые данные выставляются блоком 1 на информационный выход. При чтении информации из блока внешней памяти или внешнего устройства на управляющий выход 11 поступает сигнал чтения, а считываемые данные снимаются блоком 1 с информационных 1зходов устройстаа. Код, яодаЬаемый с первого выхода регистра 10 на вход 29 блока 7, определяет фнукцию управления логикой флагов, которая заключается либо .в установлении выбранного флага в соответствии со значением сигнала на входе 19 блока 7 либо в выдаче содержимого, выбранного флага или зн чений О и 1 на выход 20 блока 7. Работа блока 7 при этом заключает ся в следующем. В соответствии с кодом, поступающим на вход 29 блока 7, на одном из выходов дешифратора б9 вырабатывается управляющий сигнал. Если производится установка одного из группы триггеров 72, то по единич ному сигналу с выхода дешифратора 69 открывается один из группы элементов И 70. При поступлении синхроимпульса 80 на вход 16 блока 7 на выходе элемента И 70 вырабатывается импульс, по заднему фронту которого 10 3 В соответствующий триггер 72 заносит- ся значение сигнала на входе 19 блока 7. Если значение одного из группы триггеров 72 выдается на выход 20 блока 7, по единичному сигналу с соответствующего выхода дешифратора б9 открывается один из группы элементов И 71 и содержимое триггера 72 через элементы И 71 и ИЛИ 75 поступает на выход 20 блока 7. Таким образом, в предлагаемом микропроцессоре выполнение условных переходов производится без наличия холостых циклов в отличие от известного, где при выполнении каждого условного перехода присутствует холостой цикл, В результате этого предлагаемый микропроцессор не имеет потерь производительности за счет наличия холостых циклов в выполнении микропрограмм.

Фиг.1

I 3 Ц

QicMajTO

Фиг.6

Авторы

Даты

1983-08-23—Публикация

1982-02-12—Подача