Изобретение относится к вычисли;- тельной технике и может быть испель- зованр для обработки данных в сясте- мах управления.

Целью изобретения является повьппе- няе производительности микропроцессора .

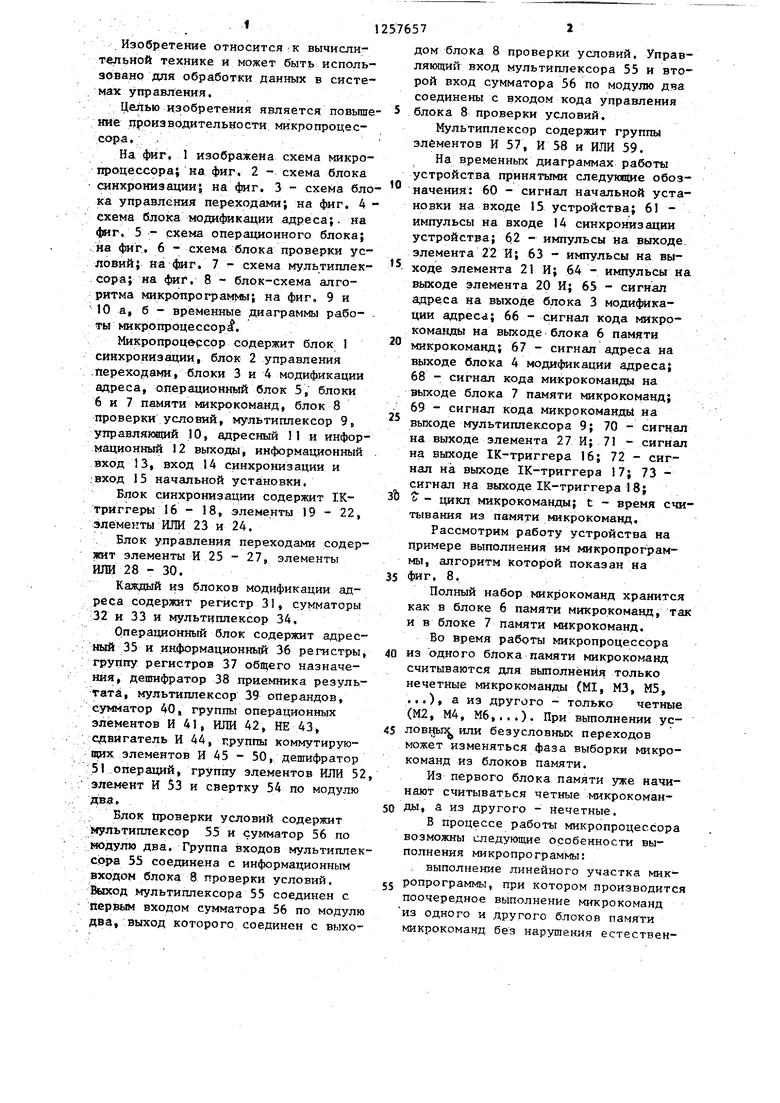

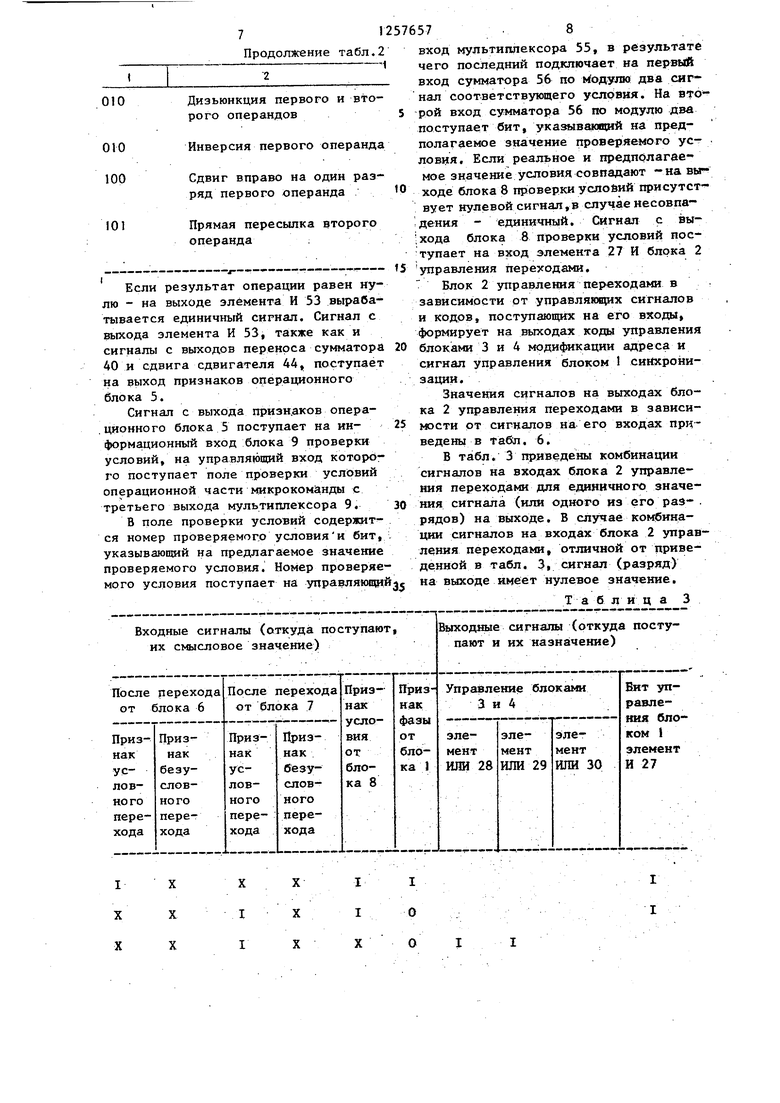

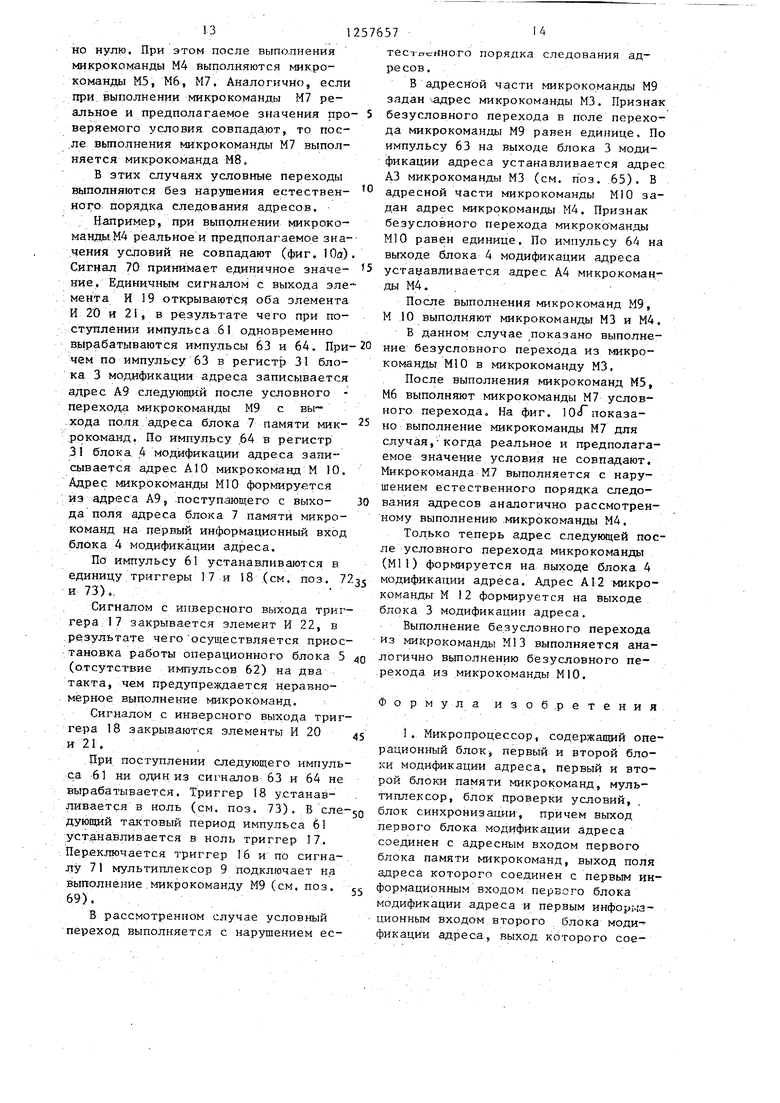

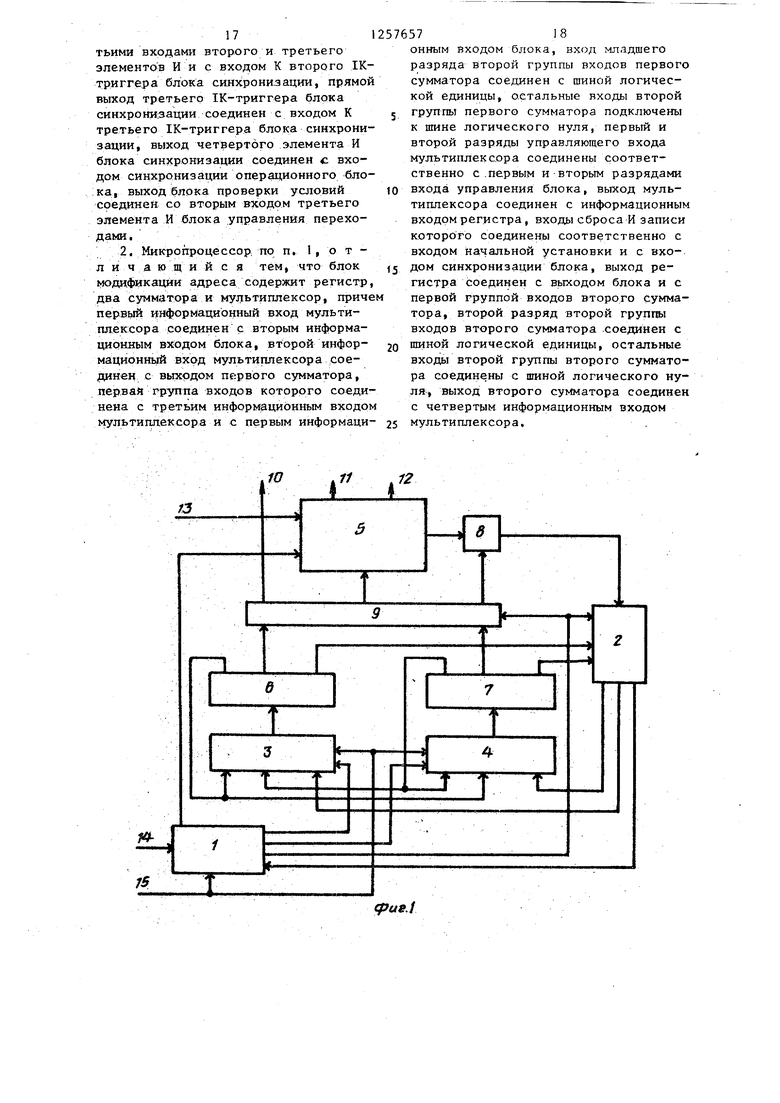

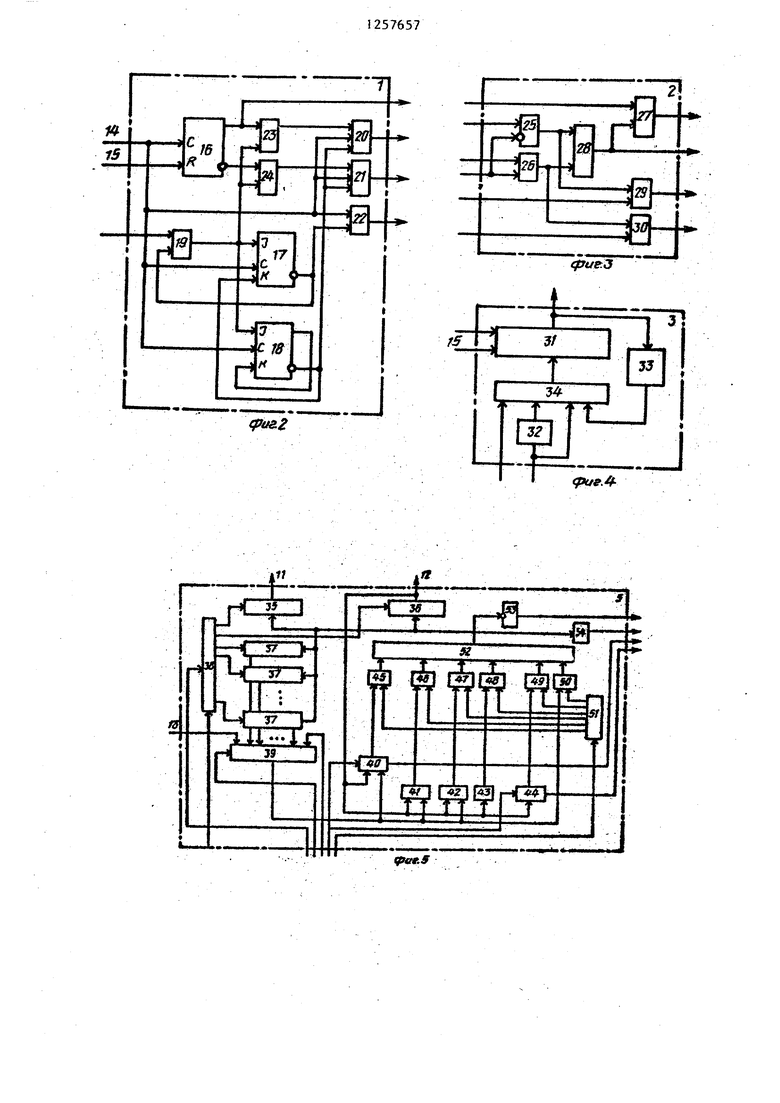

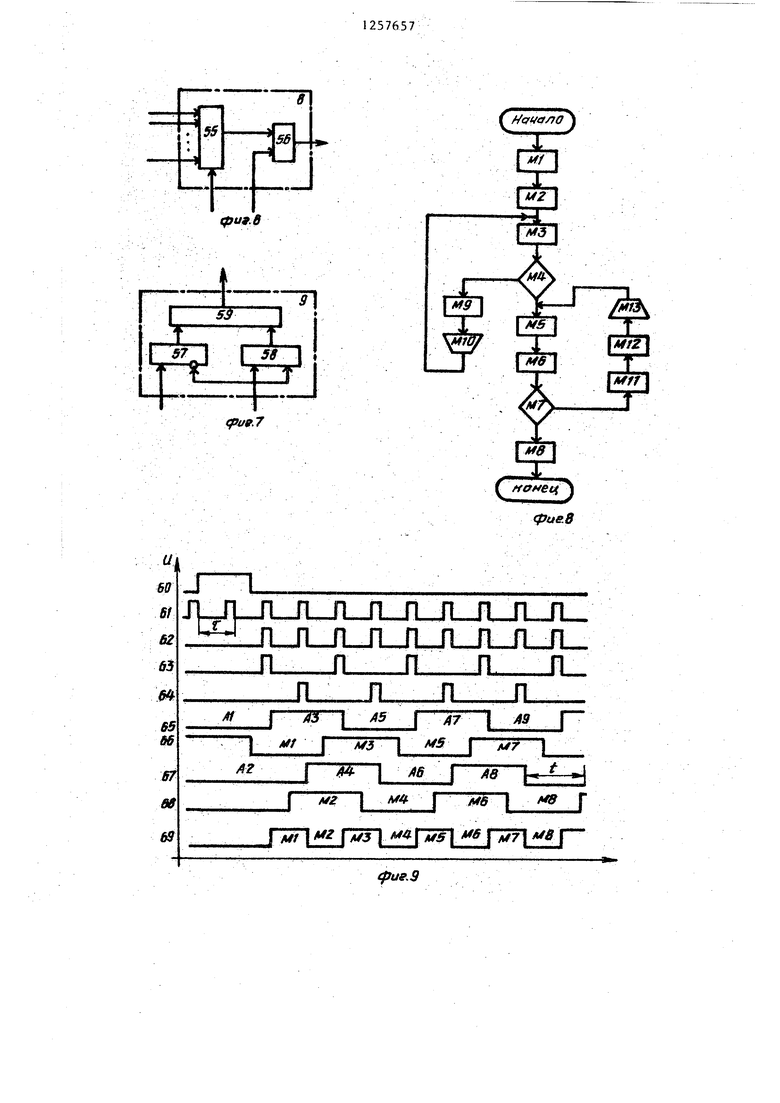

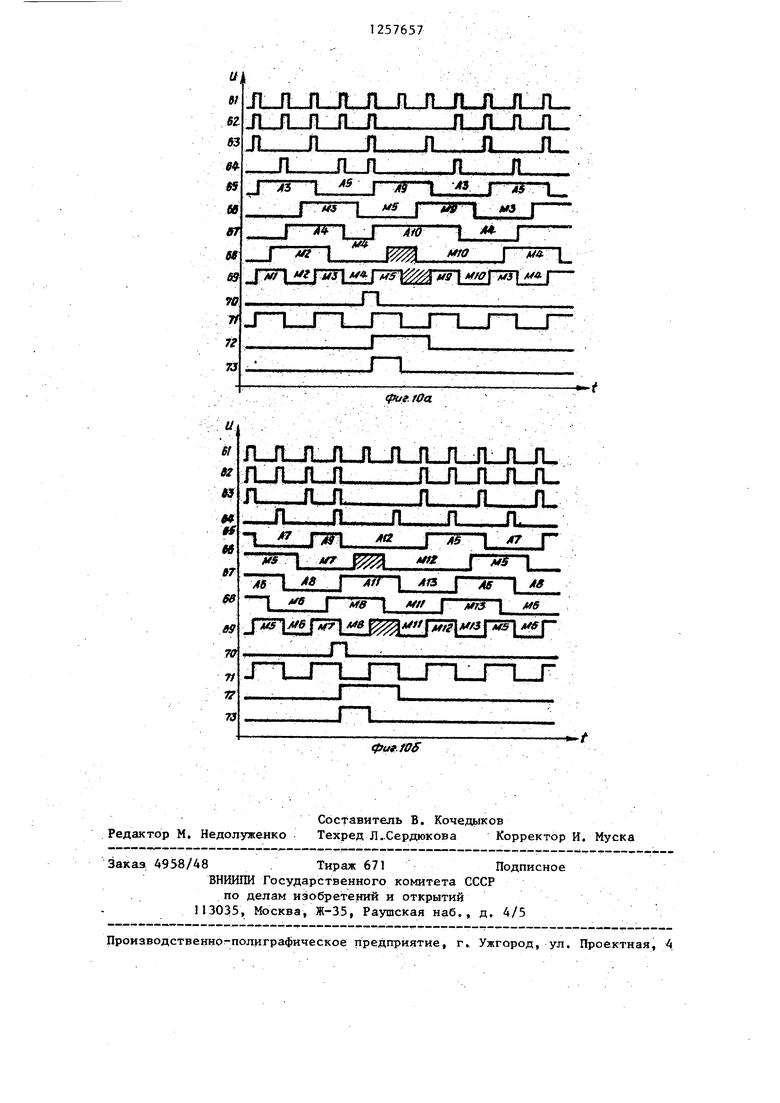

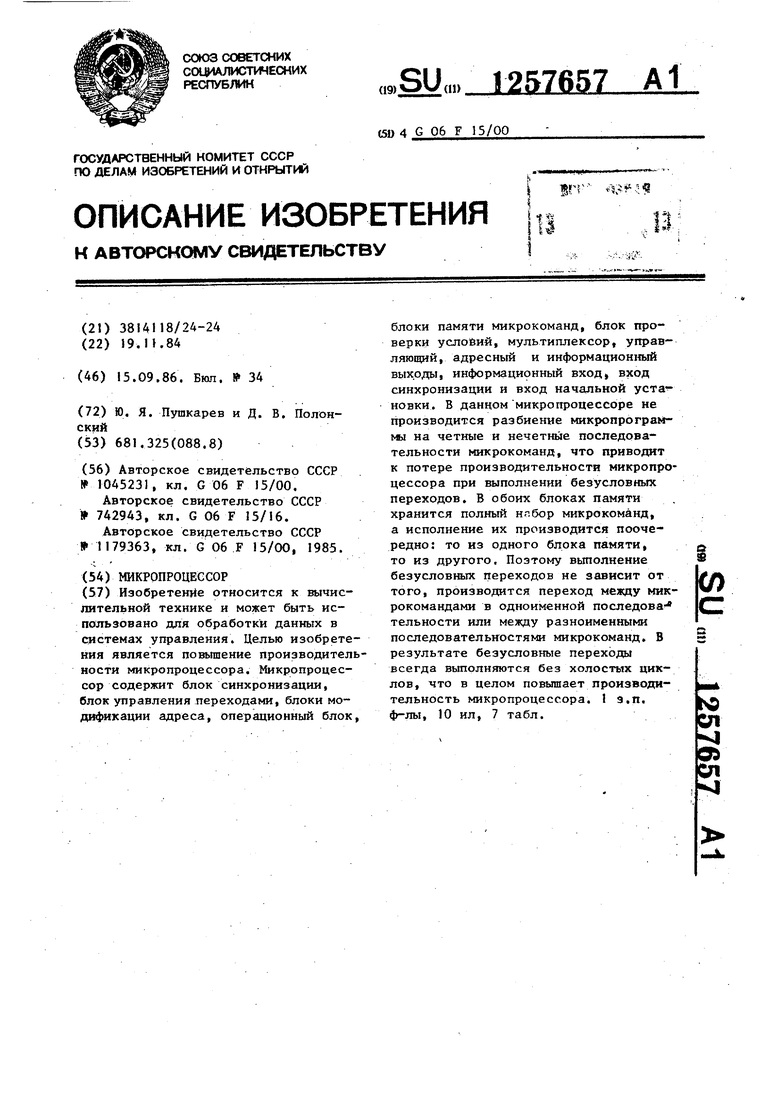

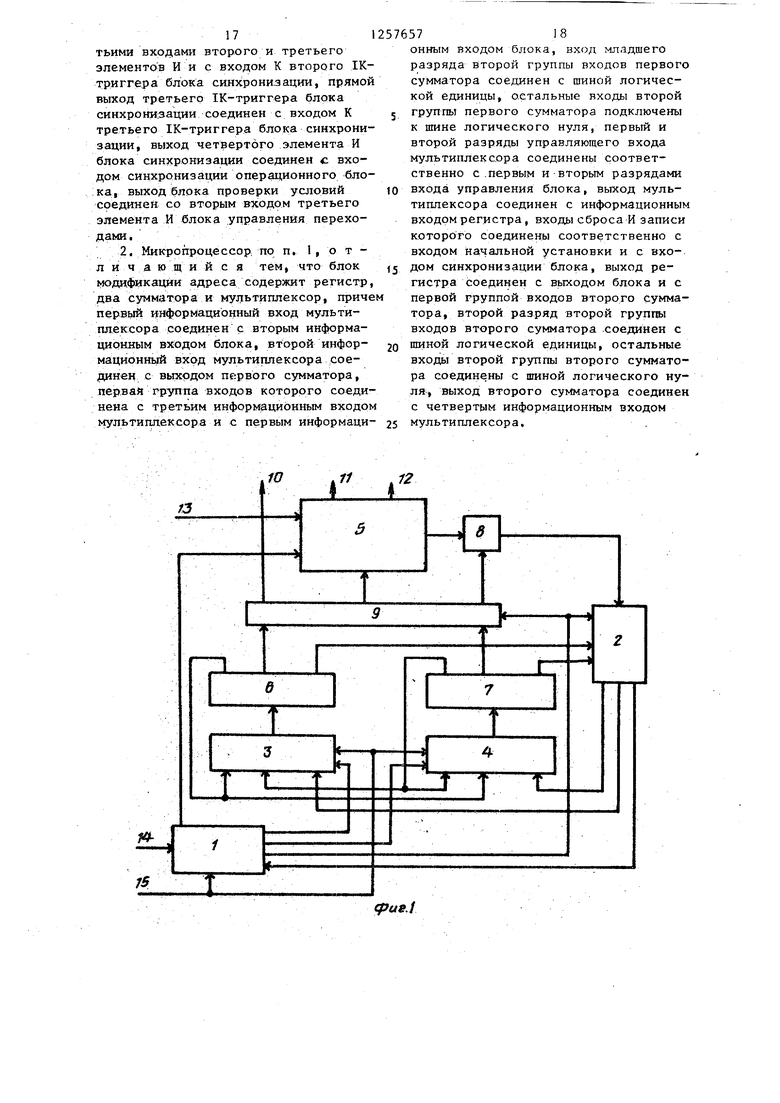

На фиг, 1 изображена схема микропроцессора; на фиг. 2 - схема блока синхронизации; на фиг. 3 - схема блока управления переходами; на фиг. 4 - схема блока модификации адреса;, на фиг. 5 - схема операционного блока; .на фиг, 6 - схема блока проверки условий; на 4ИГ, 1 схема мультиплексора; на фиг. 8 - блок-схема алгоритма микропрограммы; на фиг, 9 и 10 а, б - временные диаграммы работы микропроцессор.

Микропроцерсор содержит блок 1 синхронизации, блок 2 управления :переходами, блоки 3 и 4 модификации адреса, операционный блок 5, блоки 6 и 7 памяти микрокоманд, блок 8 проверки условий, мультиплексор 9, утфавлякя ий 10, адресный 11 и информационный 12 вьгходы, информационный вход 13, вход 54 синхронизации и .вход 15 начальной установки.

Блок синхронизации содержит IK- триггеры 16 - 18, элементы 19 - 22, элементы ИЛИ 23 и 24.

Блок управления переходами содер- ямт элементы И 25 - 27, элементы ИЛИ 28 - 30.

Каждый из блоков модификации адреса содержит регистр 31, сумматоры 32 и 33 и мультиплексор 34,

Операционный блок содержит адрес- : ный 35 и информационнь|й 36 регистры, ; группу регистров 37 общего назначения, депгафратор 38 приемника результата, мультиплексор 39 операндов, сумматор 40, группы операционных элементов И 41, ИЛИ 42, НЕ 43

сдвнгатель И 44, группы коммутирую- 1ЦИХ элементов И 45 - 50, дешифратор 51 операций, группу элементов ИЛИ 52, элемент И 53 и свертку 54 по модулю два., . , , .

Блок хфоверки условий содержит мультиплексор 55 и сумматор 56 по 1 юдулю два. Группа входов мультиплексора 55 соединена с информационным входом блока В проверки условий. Выход мультиплексора 55 соединен с первым входом сумматора 56 по модулю два, выход которого соединен с выхо

0

5

дом блока В проверки условий. Управляющий вход мультиплексора 55 и второй вход сумматора 56 по модулю два соединены с входом кода управления блока 8 проверки условий.

Мультиплексор содержит группы элементов И 57, И 58 и ИЛИ 39.

На временных диагра1 ах работы устройства принятыми следуня е обозначения: 60 - сигнал начальной установки на входе 15 устройства; 61 - импульсы на входе 14 синхронизации устройства; 62 - импульсы на выходе элемента 22 И; 63 - импульсы на вы- ходе элемента 21 И; в4 - импульсы на выходе элемента 20 И; 65 - сигнал адреса на выходе блока 3 модификации адреса; 66 - сигнал кода микрокоманды на выходе блока 6 памяти микрокоманд; 67 - сигнал адреса на выходе блока 4 модификации адреса;

68- сигнал кода микрокоманде на выходе блока 7 памяти микрокоманд;

69- сигнал кода микрокоманды на выходе мультиплексора 9; 70 - сигнал на выходе элемента 27 И; 71 - сигнал на выходе 1К-триггера 16; 72 - сигнал на выходе 1К-триггера 17; 73 - сигнал на выходе 1К-триггера 18;

- цикл микрокоманды; t - время считывания из памяти микрокоманд.

Рассмотрим работу устройства на примере выполнения им микропрограммы, алгоритм Которой показан на фиг, 8.

Полный набор микрокоманд хранится как в блоке 6 памяти микрокоманд, так и в блоке 7 памяти микрокоманд.

Во работы микропроцессора из одного блока памяти микрокоманд считываются для выполнения только нечетные микрокоманды (MI, МЗ, М5, ...), а из другого - только четньге (М2, М4, Мб,...). При выполнении ус- 5 ловцы или безусловных переходов может изменяться фаза выборки микрокоманд из блоков памяти.

Из первого блока памяти уже начинают считываться четные микрокоманды, а из другого - нечетные.

В процессе работы микропроцессора возможны следующие особенности выполнения микропрограммы:

выполнение линейного участка микропрограммы, при котором производится поочередное выполнение мтсрокоманд из одного и другого блоков памяти микрокоманд без нарутения естественЬ

5

0

0

5

ного порядка следования адресов (адрес каждой следующей микрокоманды 1на единицу больйе предыдущей);

выполнение условного перехода без нарушения естественного порядка следования адресов;

выполнение условного перехода с нарушением естественного порядка следования адресов;

выполнение безусловного перехода.

Алгоритм микросхемы, лредставлен- ный на фиг. 8, предполагает выполнение микропрограммы с учетом перечисленных особенностей.

Рассмотрим работу устройства в соответствии с временной дааграммой, показанной на фиг. 9.

В соответствии с а.бл. I триггер 16 постоянно находится в счетном режиме, распределяя входную серию импульсов 61 на две выходные 63

.и-64. ;. -: .. : , ,

Все действия в микропроцессоре осуществляются по задним фронтам импульсов 61-64.

По адресам А1 (0...00) и А2 (0.. ,0i,j) (см. поз. 65 и 67), соответственно из блоков 6 в 7 памяти микрокоманд через время t считываютс микрокоманды Щ и М2 (см. поз. 66 и 68).

Формат каждой микрокоманды приведен ниже,

Микрокоманда

Операционная часть

После перехода

Для приведения 1икропроцессора в исходное состояние подается сигнал 60, в результате чего регистр 31 в блоке 3 ьк дификации адреса и IK- триггер 16 устанавливаются в ноль, а регистр 31 в блоке 4 модификации адреса устан;авливается в состояние

or

16

После снятия сигнала 60 блок 1 синхрош1защ1И начинает вырабатывать две серии импульсов 63 и 64, сдви-г нутых отиос1В тельно друг друга на полупериод. Блок I синхронизации построен на базе 1К-триг.геров.

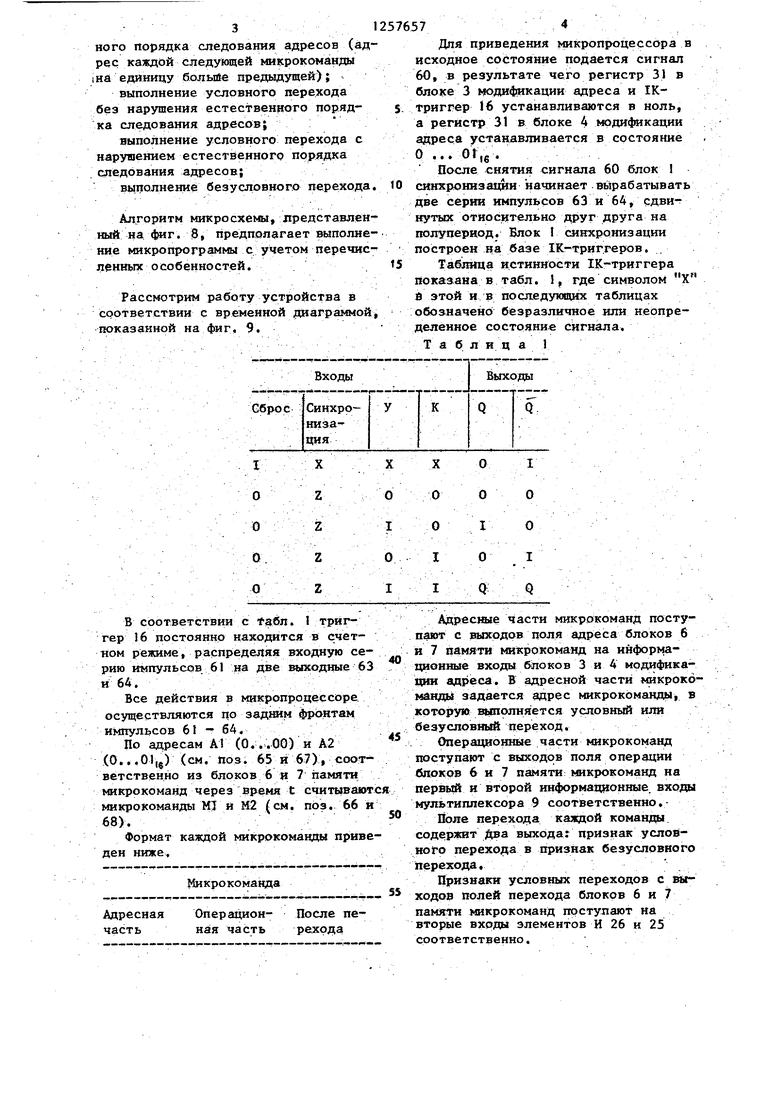

Таблица истинности 1К-триггера покааана в табл. , где символом Х б зтой ив последующих таблицах ;обоэначенЬ безразличное или неопре- делеиное состояние сигнала. Т а б л и ц а 1

Адресные части микрокоманд поступают с выходов поля адреса блоков 6 и 7 микрокоманд на информационные входы блоков 3 и 4 модификации адреса. В адресной части шкрок6- манды задается адрес микрокоманда, в которую в(шолняется условный или безусловный переход. . Операционные части микрокоманд поступают с выходов поля операции блоков 6 и 7 памяти: микрокоманд на первый и второй информационные, входы мультиплексора 9 соответственно,Поле перехода каждой команды, содержит Два выходаг признак условного перехода в признак безусловного перехода.

Признаки условных переходов с аи- ходов полей перехода блоков 6 и 7 памяти микрокоманд поступают на вторые входы элементов И 26 и 25 соответственно.

5I

Признаки безусловных переходов с выходов полей перехода блоков 6 и 7 памяти микрокоманд поступают на вторые входы элементов ИЛИ 29 и 30 соответственно.

При нулевом значении сигнала 71 мультиплексор 9 коммутирует на свои выходы операционную часть микрокоман ды М:1 с выхода блока 6 памяти микрокоманд.

Формат операционной части любой микрокоманды следующий.

Операционная часть микрокоманды

Операцион- Пола про- ное поле верки условий

Операционное поле

Поле кон- Вит Входстант ного признака

Поле приемника результата поступает на УПРАВЛЯЮЩИЙ вход дешифратора 38 i В этом поле указывается но- мер регистра (Адресно го 35, информа- ционного 36 или одного из группы регистров 37 общего назначения), в который з исывается результат выполняемой- арифметико-логической one- РДЦИИ.

Поле операндов поступает на уп- .равляюаий вход мультиплексора 39. В этом поле указывается номер.источника второго операнда для выполнения арифметико-логической опера:ции. По этому номеру мультиплексор 39 передает на свой выход или информационный .код с входа 13 микропроцессора, или содергкимое одного из группы регистро 37 общего назначения, или содержимое ,ПРля констант. Поле констант поступает на второй вход мультиплексора 39.

Вит входного признака поступает одновременно на вход переноса сумма- тора 40 и на вход сдвига сдвигателя 44, Битом входного признак-а задается входной перенос или входной сд1виг при выполнении операций сложения или сдвига.

Поле операций поступает на управляющий вход дешифратора 51. В этом поле задается код арифметико-логи

57657в

Первый информационный выход мультиплексора 9 поступает на выход 10 управления обращением к внешним устройствам микропроцессора и предназнаг чен для управления режимом чтения записи внешнего запоминаиицего устройства. Значение выхода обращения к внешним устройствам управления, равное единице, соответствует режиму

JO чтения из внешнего запоминающего устройства. Если он равен нулю - выполняется режим записи во внещнее запоминающее устройство.

Операционное поле поступает с второ15 го вьгхода мультиплексора 9 на вход кода управления операционного блока 5 .

Формат операционного поля следующий.

Поле операций

ческой операции. По этому коду дешифратор 51 открывает одну из групп элементов И 45 - 50, вследствие чего результат соответствуквцей операции с выхода сумматора 40 или с выходов групп элементов И 41, ИЛИ 42, НЕ 43, или с выходов сдвигателя 44 н мультиплексора 39 поступает на информационные входы адресного 35, информационного 36 регистров и группы регистров 37 общего назначения.

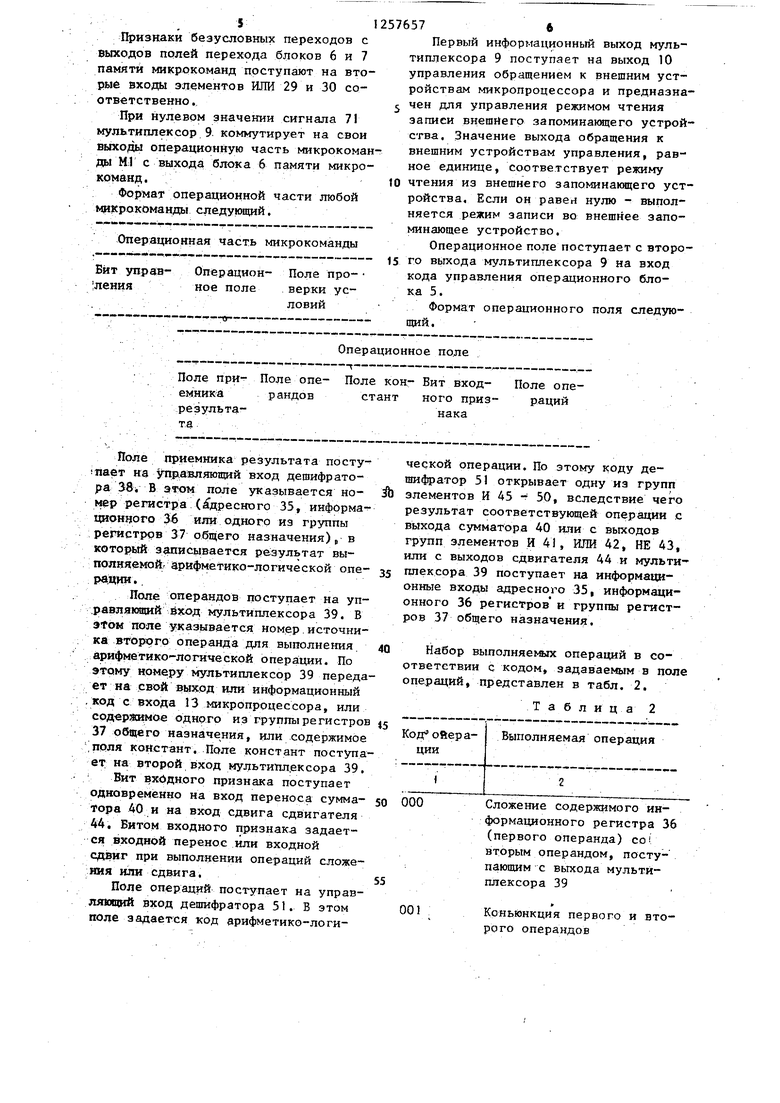

Набор выполняемых операций в соответствии с кодом, задаваемым в пол операций, представлен в табл. 2.

Таблица 2

Сложение содержимого информационного регистра 36 (первого операнда) со( вторым операндом, поступающим с выхода мультиплексора 39

Конъюнкция первого и второго операндов

Продолясение табл. 2

1

Дизъюнкция первого и второго операндов

Инверсия первого операнда

Сдвиг вправо на один разряд первого операнда

Прямая пересылка второго операнда ;

1

Если результат операции равен нулю - на выходе элемента И 53 вырабатывается единичный сигнал. Сигнал с выхода элемента И 53, также как и сигналы с выходов переноса сумматора 40 и сдвига сдвигателя 44, поступает на выход признаков операционного блока 5.

Сигнал с выхода призн.аков опера- .ционного блока 5 поступает на информационный вход блока 9 проверки условий, на управляющий вход которого поступает поле проверки условий операционной части микрокоманды с третьего выхода мультиплексора 9.

В поле проверки условий содерзшт- ся номер проверяемого условия и бит, указывающий на предлагаемое значение

30 ния сигнала (или одного из его раз- рядов) на выходе. В случае комбинации сигналов на входах блока 2 упра ления переходами, отличной от приведенной в табл. 3, сигнал (разряд)

проверяемого услоэня. Номер проверяемого условия поступает на управляющий е на выходе имеет нулевое значение.

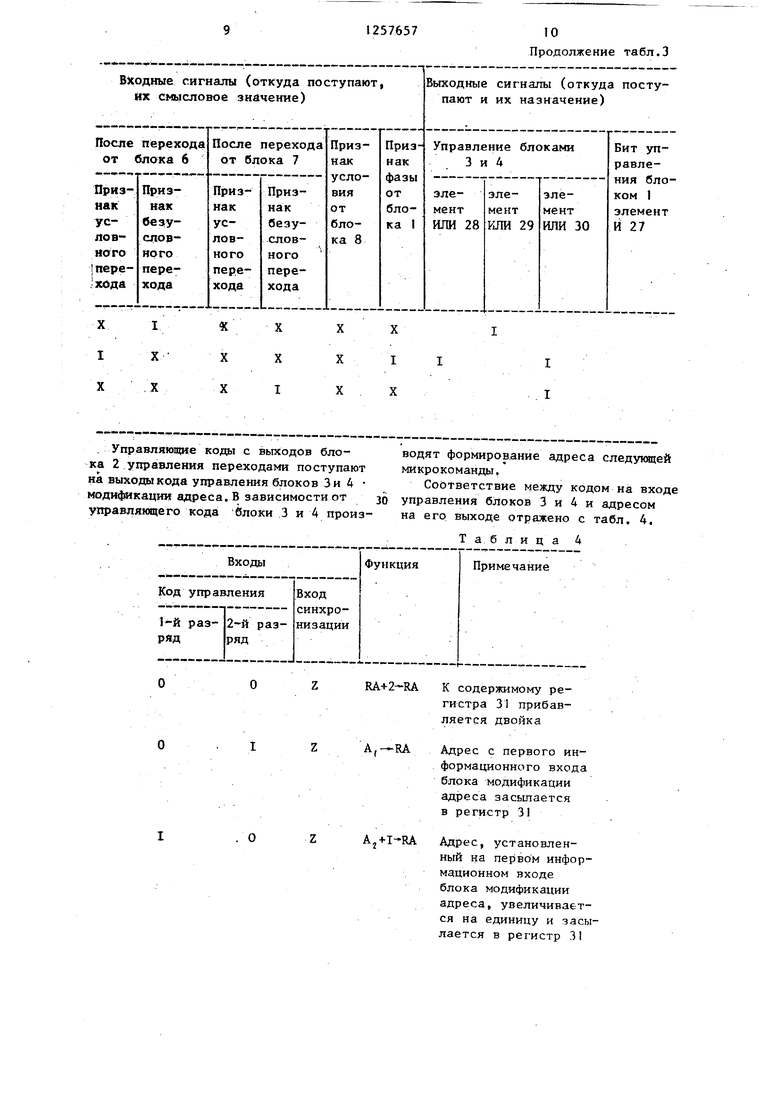

Та б л и да 3

Входные сигналы (откуда поступают, их смысловое значение)

10

вход мультиплексора 55, в результате чего последний подключает на первый вход сумматора 56 по модулю два сигнал соответствующего услбвия. На второй вход сумматора 56 по модулю два поступает бит, указывающий на предполагаемое значение проверяемого условия. Если реальное и предполагаемое значение условия совпадают -наввг ходе блока 8 проверки услобий присутст- вует нулевой сигнал,в случае несовпадения - единичный. Сигнал с вы- ;хода блока 8 проверки условий поступает на вход элемента 27 И блока 2

5 управления переходами.

Блок 2 управления переходами в зависимости от управляющих сигналов и кодов, поступающих на его входы, формирует на выходах коды управления

20 блоками 3 и 4 модификации адреса и сигнал управления блоком 1 синхронизации.

Значения сигналов на выходах блока 2 управления переходами в зависи25 мости от сигналов на его входах приведены в табл, 6.

В табл. 3 приведены комбинации сигналов на входах блока 2 управления переходами для еда1НИчного значе30 ния сигнала (или одного из его раз- . рядов) на выходе. В случае комбинации сигналов на входах блока 2 управления переходами, отличной от приведенной в табл. 3, сигнал (разряд)

е на выходе имеет нулевое значение.

Выходные сигналы (откуда поступают и их назначение)

Г I

Входные сигналы (откуда поступают, ИХ смысловое значение)

I X X

« X X

X X

I

X X X

. Управляющие коды с выходов блока 2 управления переходами поступают на выходы кода управления блоков 3 и 4 модификации адреса. В зависимости от управляющего кода блоки 3 и 4 произО

$ыходные сигналы (откуда поступают и их назначение)

X

I

X

I I

водят формирование адреса следукяцей микрокоманды.

Соответствие между кодом на входе управления блоков 3 и 4 и адресом на его выходе отражено с табл. 4.

Таблица 4

RA

-RA

к содержимому регистра 31 прибавляется двойка

Адрес с первого информационного входа блока модификации адреса засылается в регистр 31

Адрес, установленный на первом информационном входе блока модификации адреса, увеличивается на единицу и засылается в регистр 31

На линейном участке микропрограм- №1, к которому принадлежит микрокоманда HI, М2, .... поля переходов в микрокомандах равны нулю, в результате чего коды, поступающие на входы кода управления блоков 3 и 4 модифи- кации адреса, равны нулю.

При этом содержимое регистра 31 соответствующего блока модификации передается на информационный вход этого же регистра через сумматор 33 и мультиплексор 34, в результате чего код на информационном входе регистра 31 оказывается на Двойку боль ще, чем на его .выходе.

По импульсу 63 ВТ регистр 31 блока 3 модификации адреса записывается адрес A3 микрокоманды ИЗ.

По импульсу 62 результат арифметико-логической операции микрокоманды Ml с выхода группы элементов 52 ИЛИ записывается в один из приемников (адресный 35, информационный 36 регистры или один из .группы регистров 37 общего назначения), в зависимости от кода, заданного в поле приемника результата. Кроме того, пр импульсу 62 переключается триггер 16, в результате чего на выход мультиплексора 9 поступает операционная часть ьмкрокоманды М2 с выхода блока 7 памяти микроком.анд.

Информация с выхода адресного 35 и информационного 36 регистров поступает соответственно на выходы I1 и 12 микропроцессора. Выходы 10 - 12 микропроцессора предназначены дпя подключения к нему внепгаего запоминающего устройства (ВЗУ),

Если микропроцессор производит запись в ВЗУ, то по адресу, установRA

Адрес с второго информационного входа блока модификации адреса засылается в регистр 31

ленному на выходе И, и нулевом значении на. выходе Ю микропроцессора в ВЗУ записываются данные с выхода 12 микропроцессора. В режиме чтения при единичном зна чении на выход 10 по адресу, установленному на выходе П микропроцессора, из ВЗУ считывается информация и поступает на вход 13 микропроцессора.

По импульсу 64 блок 4 модификации адреса вырабатывает адрес-А4 микрокоманды М4.

После исполнения микрокоманды МЗ микропроцессор приступает к выполнению микрокоманды М4 (см. поз. 69). Микрокоманда М4 является микрокомандой условного перехода и в поле перехода этой микрокоманды бит признака условного перехода равен единице.

Сигналы, характ.еризующие результат выполнения арифметико-логической операции микрокоманды М4, поступают с выхода признаков операционного бло- - ка 5 на информационный вход блока 8 проверки условий. Мультиплексор 55 в соответствии с кодом, поступающим на его управляющий вход, подключает на первый вход сумматора 56 по модулю два сигнал необходимого условил. На второй вход сумматора 56 по модулю два поступает бит предлагаемого значения условия. Значение этого бита соответствует такому значени1О условия, при котором после выполнения микрокоманды М4 выполняется мик- юкоманда М5.

Например, реальное м предполагаемое значение условий совпадают. Тогда значение сигнала на выходе блока 8 проверки условий и сигналя 70 равно нулю. При этом после выполнения микрокоманды М4 выполняются микрокоманды М5, Мб, М7. Аналогично, если при выполнении микрокоманды М7 реальное и предполагаемое значения про- 5 веряемого условия совпадают, то после вьшолнения микрокоманды М7 выполняется микрокоманда М8.

В этих случаях условные переходы выполняются без нарушения естественного порядка следования адресов.

Например, при выполнении микрокоманды, М4 реальное и предполагаемое зна- .чения условий не совпадают (фиг, 10а).

0

тестЕгсгНного порядка следования адресов.

В адресной части микрокоманды М9 задан адрес микрокоманды МЗ. Признак безусловного перехода в поле перехода микрокоманды М9 равен единице. По импульсу 63 на выходе блока 3 модификации адреса устанавливается адрес A3 микрокоманды МЗ (см. поз. 65). В адресной части микрокоманды Mi О задан адрес микрокоманды М4. Признак безусловного перехода микрокоманды М10 равен единице. По импульсу 64 на выходе блока 4 модификации адреса

Сигнал 70 принимает единичное значе- 5 устанавливается адрес А4 микро.команды М4. .

После выполнения микрокоманд М9, М 10 выполняют микрокоманды МЗ и М4

В данном случае показано выполнение. Единичным сигналом с выхода элемента И 19 открываются оба элемента И 20 и 21, в результате чего при поступлении импульса 61 одновременно ВЬ рабатываются импульсы 63 и 64. При-20 ние безусловного перехода из микро- чем по импульсу 63 в регистр 31 бло команды Ml О в микрокоманду МЗ.

После выполнения микрокоманд М5, Мб выполняют микрокоманды М7 услов него перехода. На фиг. 10 Гпоказака 3 модификации адреса записывается адрес А9 следующий после условного - перехода микрокоманды М9 с вы.хода поля адреса блока 7 памяти мяк- 25 но выполнение микрокоманды М7 для рокоманд. По импульсу .64 в регистр 31 блока. 4 модификации адреса записывается адрес А10 микрокоманд М 10. Адрес микрокоманды Ml О формируется ..из адр-еса А9, .пост /пающего с выхо- 30 да поля адреса блока 7 памяти микрокоманд на первый информационный вход блб.ка 4 модификации адреса.

По и туль:су 61 устанавливаются в:

случая,- когда реальное и предполагаемое значение условия не совпадают. Микрокоманда М7 выполняется с нар.у- шением естественного порядка следования адресов аналогично рассмотренному выполнению .микрокоманды М4.

Тол.ько теперь адрес следующей по ле условного перехода микрокоманды (МП) формируется на выходе блока 4

единицу .триггеры 17 и 18 .(см. поз. 72 модификации адреса. Адрес микрои 73),

Сигналом с ип.версно.го выхода триггера. 17 закрывается элемент И 22, в .результате чего осуществляется приостановка работы операционного блока 5 0 логично выполнению безусловного пекоманды М 12 формируется на выходе блока 3 модификации адреса.

Выполнение безусловного перехода Из микрокоманды М13 выполняется ана(отсутствие импульсов 62) на два такта, чем предупрежда.ется неравномерное выполнение микрокоманд.

Сигналом .с инверсного выхода триггера 18 закрываются элементы И 20 ,5 .и 21.

.При поступлении следующего импульса 61 ни один из сигнал.ов 63 и 64 не вырабатывается. Триггер 18 у.станав.рехода из микрокоманды МЮ. Формула изоб.ретения

1. Микропроцессор, содержащий операционный блок первый и второй блоки модификации адреса, первый и второй блоки памяти микрокоманд, мультиплексор, блок проверки условий, блок синхронизации, причем выход первого блока модиФика.ции адреса соединен с адресным в.ходом первого блока памяти микрокоманд, выход поля адреса которого соединен с первым информационным входом первого блока модификации адреса и первым информационным входом второго . блока моди- фикации адреса, выход которого соеливается в ноль (см. поз. 73). В следующий тактовый период импульса 61 устанавливается в ноль триггер 17.. Пер.еключается триггер 16 и по сигналу 71 мультиплексор 9 подключает на выполнение микрокоманду М9 (см. поз. 69).

В рассмотренном случае условный переход выполняется с нарушением ес

тестЕгсгНного порядка следования адресов.

В адресной части микрокоманды М9 задан адрес микрокоманды МЗ. Признак безусловного перехода в поле перехода микрокоманды М9 равен единице. По импульсу 63 на выходе блока 3 модификации адреса устанавливается адрес A3 микрокоманды МЗ (см. поз. 65). В адресной части микрокоманды Mi О задан адрес микрокоманды М4. Признак безусловного перехода микрокоманды М10 равен единице. По импульсу 64 на выходе блока 4 модификации адреса

ды М4. .

После выполнения микрокоманд М9, М 10 выполняют микрокоманды МЗ и М4.

В данном случае показано выполнение безусловного перехода из микро- команды Ml О в микрокоманду МЗ.

но выполнение микрокоманды М7 для

случая,- когда реальное и предполагаемое значение условия не совпадают. Микрокоманда М7 выполняется с нар.у- шением естественного порядка следования адресов аналогично рассмотренному выполнению .микрокоманды М4.

Тол.ько теперь адрес следующей после условного перехода микрокоманды (МП) формируется на выходе блока 4

модификации адреса. Адрес микрологично выполнению безусловного пекоманды М 12 формируется на выходе блока 3 модификации адреса.

Выполнение безусловного перехода Из микрокоманды М13 выполняется ана

.рехода из микрокоманды МЮ. Формула изоб.ретения

1. Микропроцессор, содержащий операционный блок первый и второй блоки модификации адреса, первый и второй блоки памяти микрокоманд, мультиплексор, блок проверки условий, блок синхронизации, причем выход первого блока модиФика.ции адреса соединен с адресным в.ходом первого блока памяти микрокоманд, выход поля адреса которого соединен с первым информационным входом первого блока модификации адреса и первым информационным входом второго . блока моди- фикации адреса, выход которого сое

динен с адресным входом второго блока памяти ми.крокоманд,. выход поля адреса которого соединен с вторым информационным входом второго блока модификации адреса и с вторым информационным входом первого блока модификации адреса, выходы поля операции первого и второго блоков памяти мяк- рокоманд соединены соответственно с первым и вторым информационными входами мультиплексора, первый, второй и третий информационные выходы которого соединены соответственно с управлением обращения к внешним устройствам микропроцессора, с входом кода управления операционного блока и с входом кода управления блока проверки условий, вхрдь начальной установки первого и второго блоков модификации адреса соединены с входом на- чальной установки микропроцессора, информационный вход операционного блока соединен с информационным входом микропроцессора, выход признаков результата, первый и второй информа- ционные выходы операционного блока соединены соответственно с информационным входом блока проверки условий, с первым и вторым информационными выходами микропроцессора, о т - лич ающийся тем, что, с целью повышения производительности, блок синхронизации содержит три IK- триггера, четыре элемента И и два элемента ИЛИ, в микропроцессор введен блок управления переходами, содержащий три элемента И и три эле- ме.нта ИЛИ, причем входы синхронизаци первого, второго и третьего 1К-триг- геров блока синхронизации соединены с первыми входами второго, третьего и четвертого элементов И блока синхронизации и с входом синхронизации микропроцессора, вых.од первого IK- триггера блока синхронизации соеди- йе.н с первым входом первого элемен- та ИЛИ блока синхронизации, с управ- лякндим входом мультиплексора, с первым входом второго элемента И и с инверсным входом первого элемента И блока управления переходами, I и К- входы и вход сброса первого 1К-триг- гера бло-ка синхронизации соединены соответственно с входом л гической единицы микропроцессора и с входом начальной установки микропроцессора, инверсный выход первого 1К-триггера блока синхронизации соединен с Первы

1.0

520 25

JO

35

0

5

0

5

входом второго элемента ШМ блока синхронизации, выходы первого и второго элементов ИЛИ блока синхронизации соединены с вторыми входами соответственно второго и третьего элементов И блока синхронизации, выходы второго и третьего элементов И блока синхронизации соединены с входами синхронизации соответственно второго и первого блоков модификации адреса, выход признака условного перехода и выход признака безусловного перехода поля перехода первого блока памяти микрокоманд соединень с вторыми входами соответственно вто рого элемента И и второго элемента ИЛИ блока управления переходами, выход признака условного перехода и выход признака безусловного перехода поля управ.ления второго блока памяти микрокоманд соединены с вторыми входами соответственно первого элемента И и третьего элемента ИЛИ блока управления переходами, выход первого элемента И блока управления переходами соединен с первыми входами первого и второго элементов ИЛИ блока управления переходами, выход второго- элемента И блока управления переходами соединен с первым входом третьего элемента ИЛИ и со вторым входом первого элемента ИЛИ блока управления переходами,, выход второго и третьего элементов ИЛИ блока управления переходами соединены с первым входом управления модификацией адреса соотО

ветственно первого и второго блоков модификации адреса, выход первого элемента ИЛИ блока управления переходами соединен с первым входом третьего элемента И блока управления переходами и с вторым входом управления модификацией адреса первого и второго блоков модификации адреса, выход третьего элемента И блока управления переходами соединен с первым входом первого элемента И блока синхронизации, выход первого элемента И блока синхронизации соединен с вторыми входами первого, второго элементов ИЛИ и с входами I второго и третьего 1К-триггеров блока синхронизации, инверсный выход второго 1К-триггера блока синхронизации соединен с вторыми входами первого и четвертого элементов И блока синхронизации, инверсный выход третьего 1К-триггера. блока синхронизации соединен с третьими входами второго и третьего элементов И и с входом К второго IK- триггера блока синхронизации, прямой выход третьего 1К-триггера блока синхронизации соединен с входом К третьего 1К-триггера блока синхронизации, выход четвертого элемента И блока синхронизации соединен с входом синхронизации операционного блока, выход блока проверки условий соединен со вторым входом третьего элемента И блока управления переходами ,

2, Микропроцессор, по п. 1, о т - л и ч а ю щ и и с я тем, что блок модификации адреса содержит регистр, два сумматора и мультиплексор, приче первый инФ зрмационный вход мультиплексора соединен с вторым информационным входом блока, второй инфор- мационный вход мультиплексора соединен с выхрдом первого сумматора, первая группа входов которого соеди - нена с третьим информационным входом мультигагексора и с первым информаци-

онным входом блока, вход младшего разряда второй группы входов первого сумматора соединен с шиной логической единицы, о.етальные входы второй группы первого сумматора подключены к шине логического нуля, первый и второй разряды управляющего входа мультиплексора соединены соответственно с .первым и вторым разрядами входа управления блока, выход мультиплексора соединен с информационным входом регистра, входь сброса И записи которого соединены соответственно с входом начальной установки и с входом синхронизации блока, выход регистра соединен с вьгходом блока и с первой группой входов второго сумматора, второй разряд второй групгвд входов второго сумматора .соединен с шиной логической единицы, остальные входы второй группы второго сумматора соединены с шиной логического нуля;, выход второго сумматора соединен с четвертым информационным входом мультиплексора.

epug.l

tptatf,5

фа9.6

:zrL53

tpt/e.7

I-J1-JT J1JLJT

лльл-лтлыиг

л

я

л

л

JL.

Л

К

л

п

/«/

/W

т у I i Г

л

л

JL.

К

л

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1984 |

|

SU1164721A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Микропроцессор | 1985 |

|

SU1273939A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1254481A1 |

| Микропрограммный процессор | 1982 |

|

SU1037264A1 |

| Процессор | 1984 |

|

SU1200294A1 |

Изобретение относится к вычислительной технике и может быть использовано для обработки данных в системах управления. Целью изобретения является повьшение производительности микропроцессора. Микропроцессор содержит блок синхронизации, блок управления переходами, блоки модификации адреса, операционный блок. блоки памяти микрокоманд, блок проверки усло1бий, мультиплексор, управляющий, адресный и информационный выходы, информационный вход, вход синхронизации и вход начальной уста новки. В данном микропроцессоре не производится разбиение микропрограм- мл на четные и нечетные последовательности микрокоманд, что приводит к потере производительности микропроцессора при выполнении безусловных переходов. В обоих блоках памяти хранится полный нг.бор микрокоманд, а исполнение их производится поочередно: то из одного блока памяти, то из другого. Позтому вьтолнение безусловных переходов не зависит от того, производатся переход между микрокомандами в одноименной последова- тельности или между разноименными последовательностями микрокоманд, В результате безусловные переходы всегда выполняются без холостых циклов, что в целом повышает производительность микропроцессора. 1 з.п. ф-лы, 10 ил, 7 табл. СП

| Микропроцессор | 1982 |

|

SU1045231A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мультипроцессорная система | 1978 |

|

SU742943A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-15—Публикация

1984-11-19—Подача