1

Изобретение относится к области -вычислительной техники и может быть использовано для конструирования сложных систем при оптимизации структуры систем, состоящей из п подсистем различного типа, по критерию минимума суммарной характеристики выбранных вариантов подсистем с учетом связей междуними.

Известны устройства, проидводящие выборку и суммирование значений параметров 1, однако они решают ограниченный класс задач. Наиболее близким по технической сущности к изобретению является устройство для оптимизации размещения центров радиальной сети по минимуму суммарной стоимости линии с§язи 2, содержащее блок памяти, сумматор, блок сравнения-И блок выдачи.

Недостатком известного устройства является невозможность решейия: задачи оптимизации систем со сложной структурой.

Целью изобретения является расширение класса решаемых задач.

Поставленная цель достигается тем, что в предложенное устройство введены коммутатор, блок управления и блок задания вариантов структуры.

Первый вход блока задания вариантов .структуры подключен к первому входу блока выдачи результатов и hepBOMy входу коммутатора, выход которого соединен с первым входом сумматора, выход KOToi 6rd к первому входу блока сравнения и ко второму блока выдачи результатов. Выход блока сравнения соединен с третьoим входом блока выдачи результата, . выход которого подключен ко второму входу блока сравнения. Первый, второй, третий, четвертый и пятый вы- , ходы блока управления соединены со5ответственно со входом блока задания

варйантЬв б рУ1к руры7 йо вттэрйй вхЬдом коммутатора, со вторым входом сумматора, со вторым входом блока сравнения и с четвертТйм входом бло0ка выдачи результата. Вход блока управления подключён ко второму выходу блока задания вариантов.структуры. Выход блока памяти соединен с трёт.ьим входом коммутатора.

5

Блок задания вариантов структуры содержит регистр, выходы которого через дешифратор соединены с первыми входами элементов И, вторые входы которых объединены и являются

0 входами блока задания вариантов

структуры. Выход ; одного элемента И Й дключён k первому ВХОДУ первого

узла выбора варианта структуры, ёы 5сйда|других элементов и - с первыш входами элементов fflffi,Iffо 1даГШШГ котЬ1Ш 1шШпйчШеГ Т1ТШр- -вйМ вйходам соответствующих узлов Bfci6opa варианта структуры кроме последнего, первый выход котбрбгб : объединен с выходами дешифратора и является вторым выходом блока задания вариантов структуры. Выходы элементов ИЛИ подключены к первым вхо Ш Ъбо ёётствующих узлов выбора варианта структуры. Вторые входы узлов выбора варианта структуры обЪеди ены и являются входом блока задания вариантов структуры. выхода узлов выбора варианта структуры объединены и являются йервйм выходом блока задания вариантов структуры.

Узел выбора варианта струкгуры Ъсэд ржит регистр, выходы йоторото соединены со входами дешифратора, ввСхбдЁГ КЬторогр непосредственнр под лй1ены к первым входам элементов И первой группы.и через элементы НЕ к первым входам элёме:нтов и втЪрой группы. Втбрые входы элементов И первой и второй групп подключ е1Ш

выход м сооТвёТствуюадих три Геров,

кроме последнего, а последнего - f -fsjfgp-a сОединен & пё ЬвйМ Входом эле;мента ИЛИ. ;вход §лшён;та ;;

ИЛИ уГйЗГйГется втЬрым входом У8ГлаВЫ65pt 1арианта ет)Укту;риГ-еодавёТ(5твуйщие входы элемента ИЛИ подключеЙЫ к выходам элементов И группы. Выходы элементов И f ftnlSr-ч рез элементы задержки дйнейы с первыми входами трйггеров, кроме первого. Вторые входы триггеров объединёны и являются первым входом узла выбора варианТов ст ктуры. Первый вход первого 1 1г а объединен со входом элемента задерж%1 й яёляется вторь м входо лу зла выбора варианта структуры. Вьахода элемейта задержки подключен к выходу эл5лента ЯИ и яйляетс-я первым вй зсодомузла выбора вариайт аТГТб)уктуры.

БлЪ й угфавления содержит первый, второй К третий Т15йггёры, генератор, первый,-и второй элементы И, первый, вторбйхи третий дешифраторы,пёрвйй и вторЬй шифраторы, первый второй и третий счетчики. Выход первого,триг ifepa подключен к первому входу первого, элемента И, второй вход которого сое дин ей с выходом генератора и 1Э ШрШй входом второго элемента И, -в ор5й йбтЬ ибго: подключен к выходу Второго триггера, первый и второй входы которого соединены со тёётствейно с первым и вторым вхо °-ЩШ пёрВОго триггера и с первыми -- ,:|-ШШ« пёрвого и второго дешифра678489

:торов. Выход второго элемента И подключен ко входу первого счетчика, вйхОд которого соединен со входом первого дешифратора, первый выход которого подключен к первому входу рёТьегЬ TjiHrrepa и является первым выходом блока управления. Второй и Т ретий выходы первого дешифратора

явйяйтся соответственно четвертым и пят.ым выходами блока управления. Второй вхбд третьего триггера объединен со входами первого шифратора и является входом блока управления. Выход третьего триггера соединен со входом генератора. Входы первого шифт 1тора подключены ко входу блока управления. Выход первого шифратора

соёданен егПёе)Шй входом второго ёчетчйкй, й1аХОД которого подключен ко входу второго дешифратора, собтветствующиевыходы которого объеЙйнёны и являются вторым входом блока у1траёлёййя и соединены со входа Ш вто1эбгб шифратора, ВЙХОД которого подключён к первому входу третьего счетчика, второй вход которого соедийён с вйходом первого элемента И и являё тся третьим выходом блока управления . Выхбд третьего счетчика соеДинёй со входом третьего дешифратора, первый выход которого подклю feHi«o tffBt30is s Входу второго счетчика, а соответствующие выходы подйлюЧ:еньа ко второму . блока управления. Второй вход- первого т&иггёра яйЛяется вторым входом блбка

уг1равления - ..

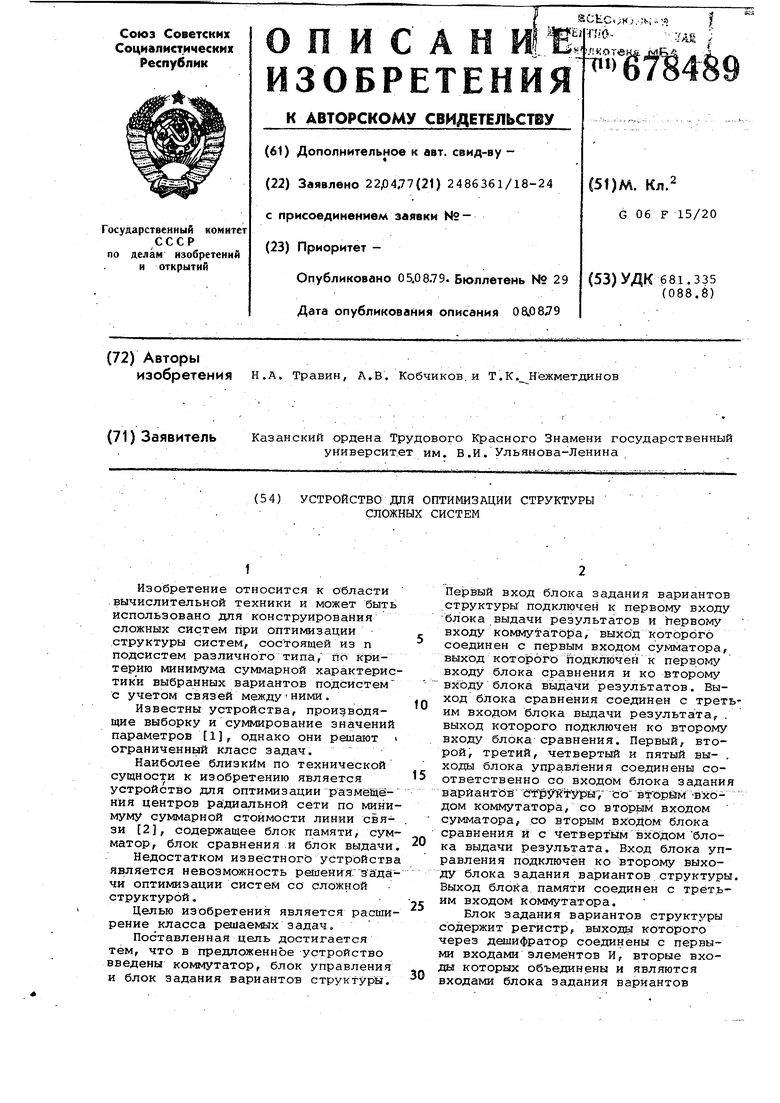

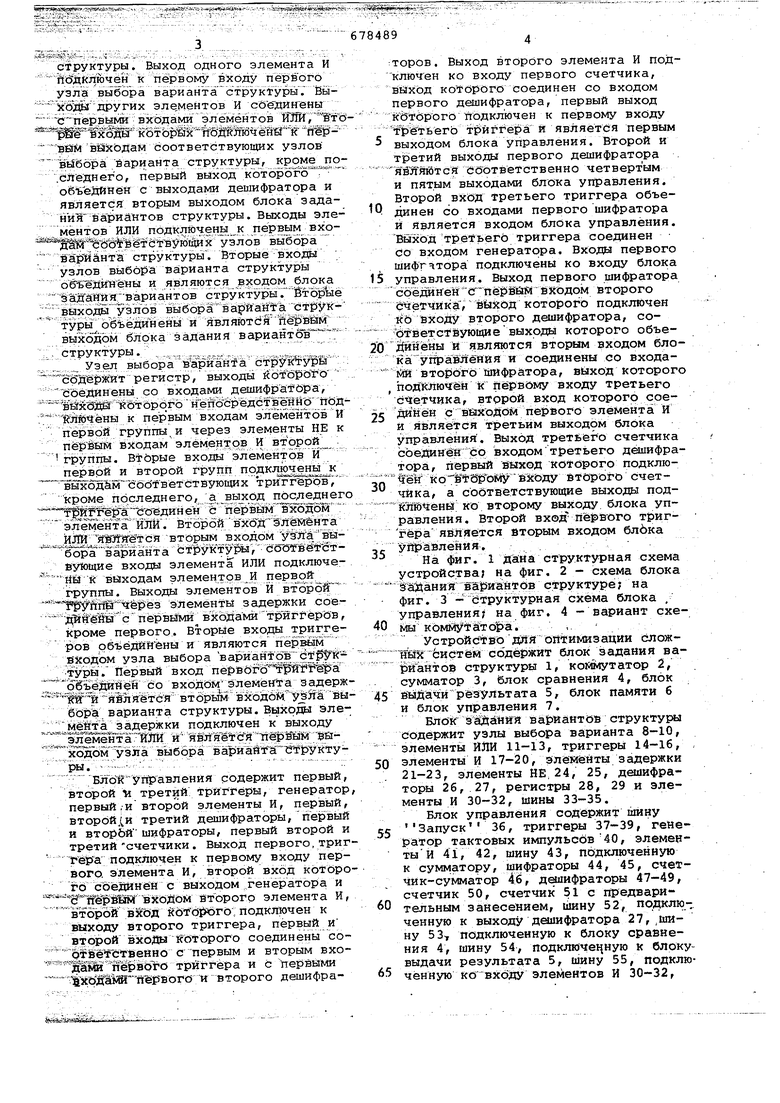

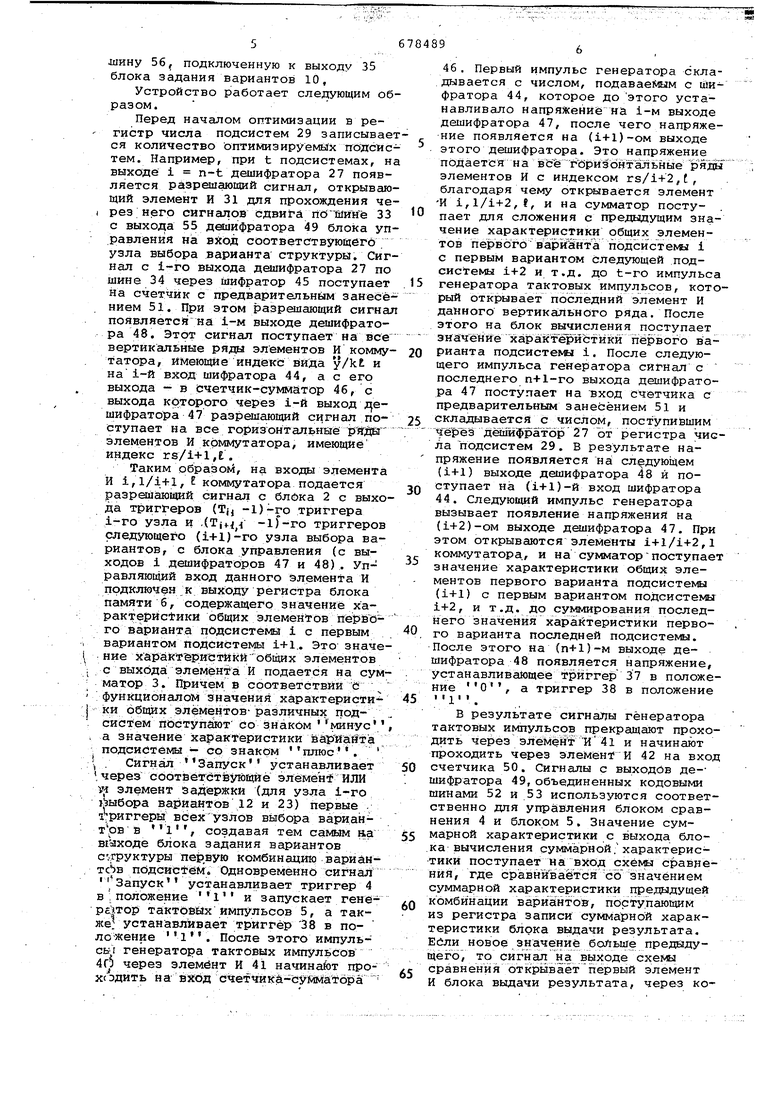

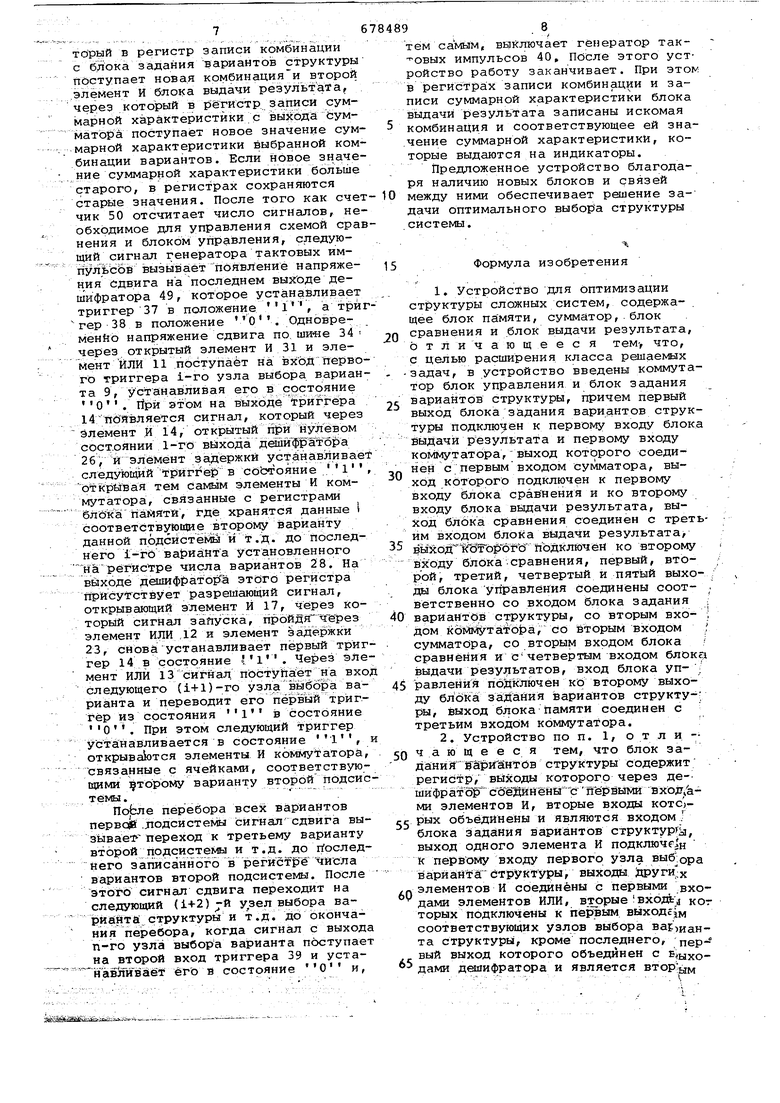

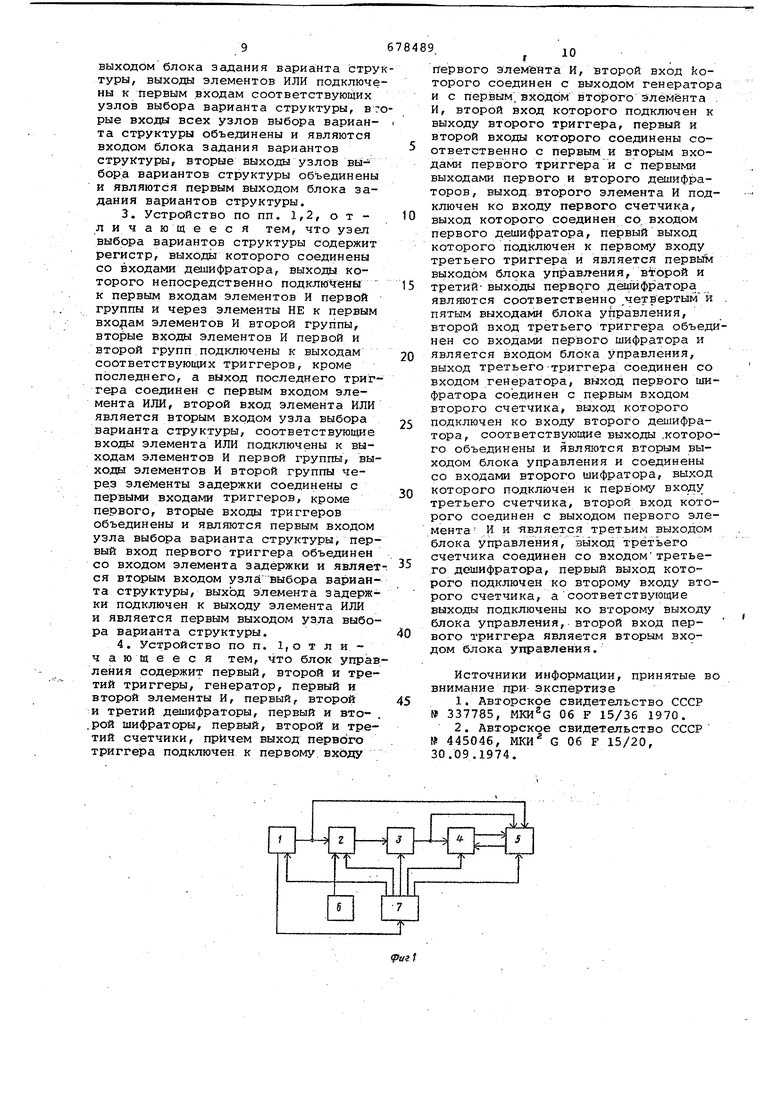

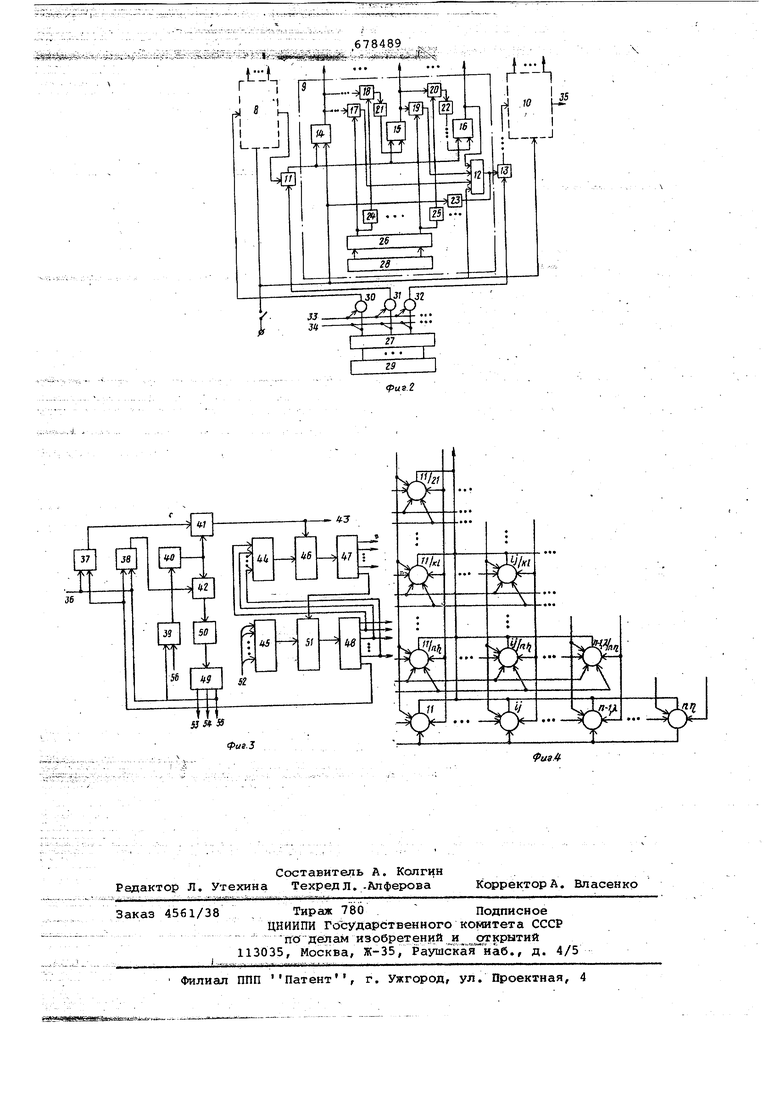

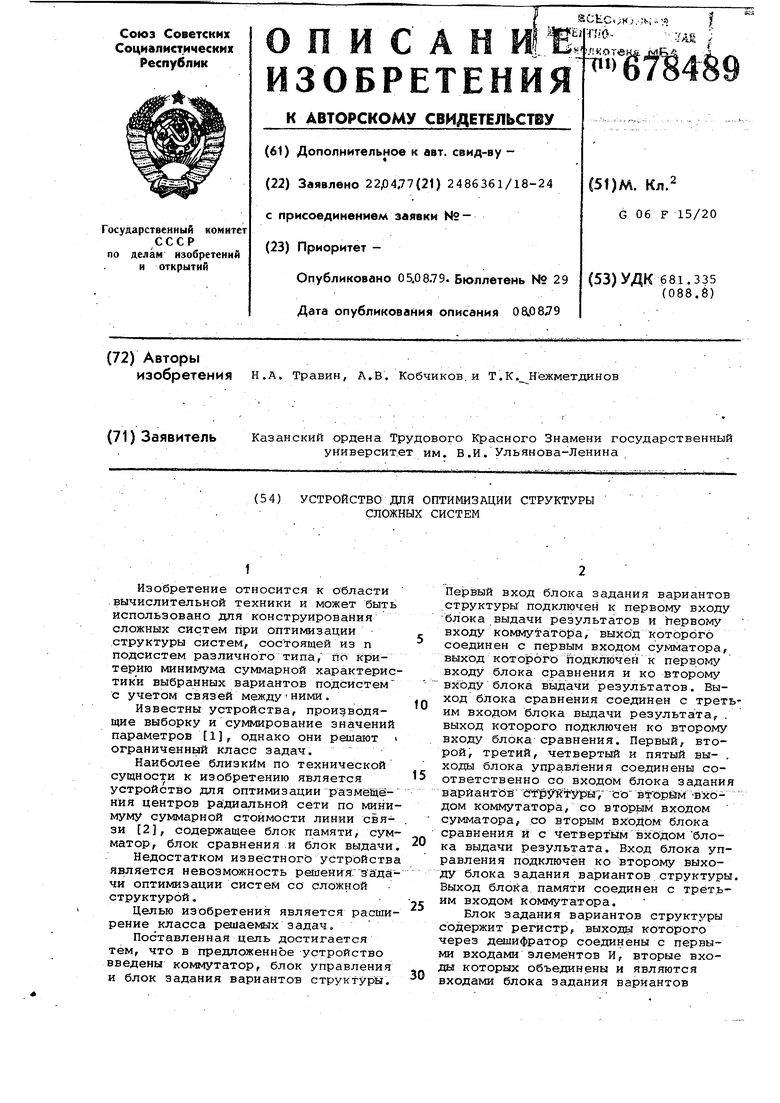

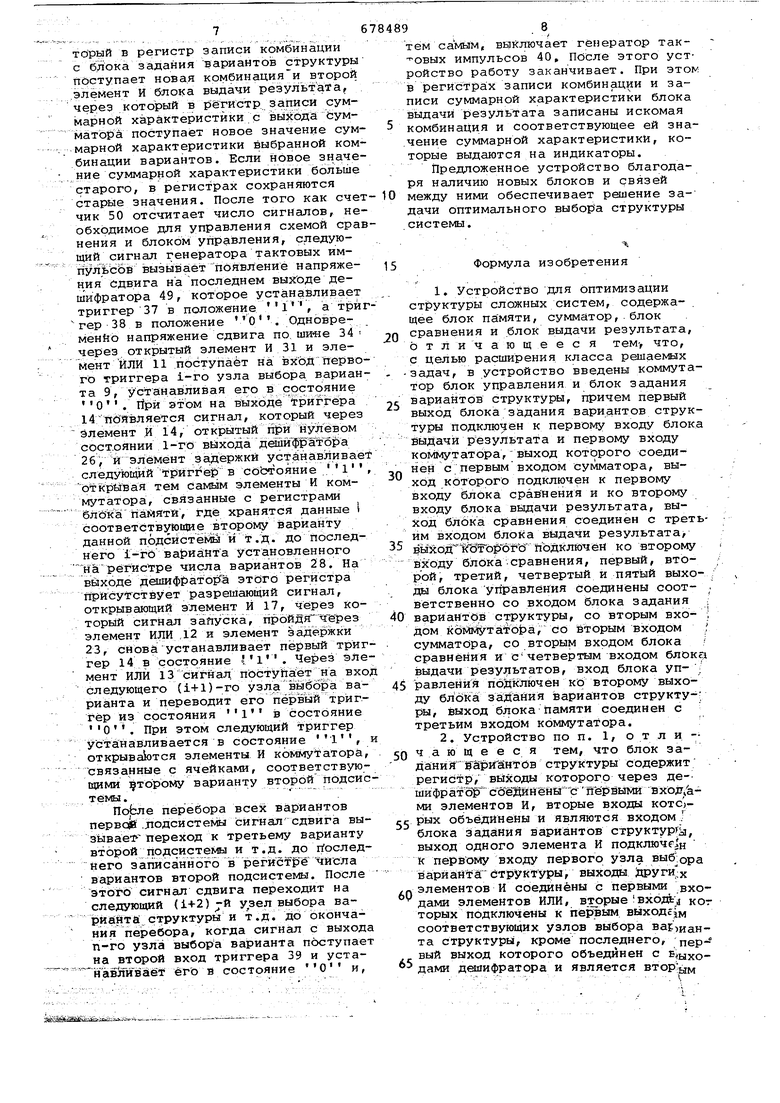

На фиг. 1 дана структурная схема устройства; на фиг. 2 - схема блока §Шания вариайтов структуре г н а фиг. 3 - структурная схема блока управления; на фиг. 4 - вариант схеШ KbMMytMTolxa.,.

Устройство ДЛЯ оптимизации ьлож

ШхЬистем содержит блок задания ва йайтов структуры 1, ко15 Йутатор 2, сумматор 3, блок сравнения 4, блбк В1лйачй результата 5, блок памяти б и блок управления 7.

ЗсЩанйЯ ва)Иайтов структуры содержит узлы выбора варианта 8-10, элементы ИЛИ 11-13, триггеры 14-16, элементы И 17-2 О, элемёйтй задержки 21-23, элементы НЕ,24, 25, дешифраторы 26, 27, регистры 28, 29 и элементы И 30-32, ШИНЫ 33-35.

Блок управления содержит шйну Запуск 36, триггеры 37-39, гене1затор тактовых импульсбв 40, злемзйтйИ 4i, 42, шину 43, подключенную к сумматору, шифраторы 44, 45, счетчик-сумматор 4б, дешифраторы 47-49, счетчик 50, счетчик 51 с предварительным занесением, шину 52, подкл1о ченную к выходу дваифратора 27, ,1ийну 53, подключенную к блоку сравнения 4, шину 54, подключенную к блокувыдачи результата 5, шйну 55, подключённую ко вхдДу эле1 1ентов И 30-32, шину 56, подключенную к выходу 35 блока задания вариантов 10, Устройство работает следующим о разом. Перед началом оптимизации в регистр числа подсистем 29 записыва ся колйчество оптимиз тем. Например, при t подсистемах, н выходе i n-t дешифратора 27 появляется разрешающий сигнал, открываю щий элемент И 31 для прохождения че I рез него сигналов сдвига поШййё 33 с выхода 55 дешифратора 49 блока уп равления на вход соответствующего узла выбора варианта структуры. Сиг нал с i-ro выхода дешифратора 27 по шине 34 через 1)аифратор 45 поступает на счетчик с предварительным занесе нием 51. При этом разрешающий сигна появляется на 1-м выходе дешифратора 48. Этот сигнал поступает на все вертикальные ряды элементов И комму татора, имеющие индекь вида y/kt и на±-й вход шифратора 44, а с его выхода - в счетчик-сумматор 46, с выхода которого через i-й выход j eшифратора 47 разрешающий сигнал поступает на все гориз-онтальннё i5frS 3 элементов И коммутатора, имеющие индекс rs/i+l,t.. Таким образом, на входы элемента И 1,1/1+1, I коммутатора подается разроаающий сигнал с блока 2 с выхо да триггеров (Т-ц -1)-го триггера 1-го узла и .{Tjfi v -1)-го триггеров следующего (i+l)-ro узла выбора вариантов, с блока управления (с выходов i дешифраторов 47 и 48). Управляющий вход данного элемента И подключен.к выходу регистра блока памяти б, содержащего значение карактерйсфики общих элементов первОго варианта подсистемы i с первым вариантом подсистемы 1+1.. Это значе ние характ рнстИкй общих элементов с выхода: элемента И подается на сум матор 3. Причем в соответствий и функционалом значения характеристик ки обпшх элементов-различных под. систем яоступают Со знаком минус , а значение Характеристики варШй; подсистемы - со знаком плюс. , . Сигнал Запуск устанавливает через соответствующие элёмен ИЛИ vi элемент задержки (для узла 1-го выбора вариантов 12 и 23) первые а риггеры. вЬехузлов выбора вариантрв в 1, создавая тем самым на В1аходе блока задания вариантов с .;груктуры комбинацию вариантсЬв подсистем. Одновременно сигнал Запуск устанавливает триггер 4 в;положение и запускает генеРс|.тор тактовых импульсов 5, а также: устанавливает триггер 38 в поло-женйе . После этого импульCKI генератора тактовых импульсов 4г5 через элемент И 41 начинает проходить на вход С етчйка-суйМатора 46. Первый импульс генератора складывается с числом, подаваемым с шифратора 44, которое до этого устанавливало напряжение на 1-м выходе дешифратора 47, после чего напряжение появляется на (1+1)-ом выходе этого дешифратора. Это напряжение подается на вСё г-ОризонТальные pSS элементов И с индексом rs/i+2,t, благодаря чему открывается элемент И 1,1/1+2,f, и на сумматор посту- . пает для сложения с предьщущим значение характеристики общих элементов первого ва1рйанта подсистемы 1 с первым вариантом Следующей подсисТемы 1+2 и т.д. до t-ro импульса генератора тактовых импульсов, который открывает последний элемент И дайного вертикального ряда. После этого на блок вычисления поступает значение Ха:рактёрйстйкн первого варианта подсистема 1. После следующего импульса генератора сигнал с последнего п+1-го выхода дешифратора 47 поступает на вход счетчика с предварительным занесением 51 и складывается с числом, поступившим дешифратор 27 от регистра числа подсистем 29. В результате напряжение появляется на следующем (1+1) выходе дешифратора 48 и поступает на (1+1)-и вход шифратора 44. Следующий импульс генератора вызывает появление напряжения на (1+2)-ом выходе дешифратора 47. При этом открываются элементы 1+1/1+2,1 коммутатора., и на сумматорпоступает значение характеристики общих элементов первого варианта подсистемы (1+1) с первым вариантом подсистемы 1+2, и т.д. до суммирования последнего значения характеристики первого варианта последней подсисте «л. После этого на (п+1)-м выходе дешифратора 48 появляется напряжение, устанавливающее триггер 37 в положение О, а триггер 38 в положение I 11 I I в результате сигналы генератора тактовых импульсов прекращают проходить через элеМей И41 и начинают проходить через элемент И 42 на вход счетчика 50. Сигналы с выходов дешифратора 49, объединенных кодовыми шинами 52 и 53 используются соответственно для управления блоком сравнения 4 и блоком 5. Значение суммарной характеристики с выхода блока вычисления суммарной, характеристики поступает на вход схет сравнения, где сравнйваётся со значением суммарной характеристики предыдущей комбинации вариантов, поступающим из регистра записи суммарной характеристики блока выдачи результата, вели новое значение больше предйдуще1 6, то сигнал на вых:оде сравнения открываетпервый элемент И блока выдачи результата, через коорый в регистр записи комбинации блока задания варианто1в структуры оступает новая комбинациями второй

лемент И блока выдачи результата, ерез который в Е ёгистр записи сумарной характеристики с вьахбда суматора поступает новое значение сумарной характеристики выбранной комбинации вариантов. Если новое значение суммарной характеристики больше старого, в регистрах сохраняются старые значения. После того как счетчик 50 отсчитает число сигналов, необходимое для управления схемой сравения и блоком управления, следуюий сигнал генератора тактовых имйульсйв вызывает появление напряжения сдвига на последнем выходе деифратора 49, которое устанавливает триггер 37 в положение , а трйггер 38 в положение О . Одновременйо напряжение сдвига по. ши«е 34 через открытый элемент И 31 и элемент ИЛИ 11 поступает на вход первого триггера i-ro узла выбора варианта 9, устанавливая его в состояние О. Йрй этом на выходу ригрера 14 1т6йвляется сигнал, который через элемент .И 14, открытый нулевом сост.оянии 1-го захода fliaiiHlppaT opa 26, и элемент задержки устанавливает следу1ющий триггер в ссЬтояние . 1 ,

откривая тем самым элементы И коммутатора, связанные с регистрами блоТка памяти, где хранятся данные соответствующие второму варианту данной подсйстёки и т.д. до последнего Г-говарианта установленного

а.рёгкст ре числа вариантов 28. На выходе дешифратор а этого регистра прйсутствУет разрешающий сигнал, открывающий элемент И 17, через который сигнал запуска, пройдЯ 1ерез элемент ИЛИ .12 и элемент задержки 23, снова устанавливает первый триггер состояние . Через элемент ИЛИ 13 сигнал поступает на вхой Следующего (i+l)-ro узла выбора варианта и переводит его первый триггер из Состояния 1 в состояние О . При этом следующий триггер устанавливается в состояние , и открываЬтся элементы И коммутатора. Связанные с ячейками, соответствующими второму варианту второй подсистемы. .

ПоЬле перебора всех вариантов первой .лодсистемы сигнал сдвига вызываетпереход к третьему варианту второй подсистемы и т.д. до последнего записанного в регистрёчисла

вариантов второй подсистемы. После этого сигнал сдвига переходит на следующий (1+2)й выбора варианта структуры и т.д. д6 окончания перебора, когда сигнал с выхода п-го узла выбора варианта поступает на второй вход триггера 39 и устаНafiimiaaeT его в состояние О и.

IMESisaiteii-JEiis

тем самым, выключает генератор импульсов 40, После этого устройство работу заканчивает. При 3TON: в региСтра:х записи комбинации и записи суммарной характеристики блока выдачи результата записаны искомая комбинация и соответствующее ей зна,чение суммарной характеристики, которые выдаются на индикаторы.

Предложенное устройство благодаря наличию новых блоков и связей между ними обеспечивает решение задачи оптимального выбора структуры системы.

Формула изобретения

15

1. Устройство для оптимизации структуры сложных систем, содержащее блок памяти, сумматор,.блок

сравнения и блок выдачи результата, о т Ji и ч а ю щ е е с я тем-, что, с целью расширения класса решаемых

задач, в устройство введены коммутатор блок управления и блок задания

вариантов структуры, причем первый выход блока задания вариантов структуры подключен к первому входу блока

выдачи результата и первому входу коммутатора,выход которого соединен с первым входом сумматора, выход которого подключен к первому входу блока сравнения и ко второму входу блока выдачи результата, выход блока ср авнения соединен с третьим входом блока выдачи результата,

вы:хоД 1этЬ)6гЪ поДклйчеН ко второму входу блока сравнения, первый, второй, третий, четвертый и пятый выходы блока уйравления Соединены соот- / вётственно со входом блока задания ;

вариантов структуры, со вторым вхо- ; Дом коййутатора. Со йторым входом f сумматора, со вторым входом блока сравнения и счетвертым входом блокс выдачи РезyjfibTaTOB, вход блока уп- ;

равлейия подключен ксз второму выходу блдка задания вариантов структу-; ры, выход блока памяти соединен с третьим входом коммутатора. 2. Устройство по п. 1, о т л и -ч а ю щ е е с я тем, что блок заания Га рйЙнтов структуры содержит . регистр, вйходы которого через деифрат Ш сГдедйн%йа С первыми вход/ами элементов И, вторые входы котс)рых объединены и являются входом Г блока задания вариантов структург д, выход одного элемента И подключе|н к первому входу первого узла выб.ора иарйайтйСтруктуры, выходы шуги;х

элементов И соединены с первыми входами элементов ИЛИ, вторые входа ог торых подключены к первым выходе м оответствующих узлов выбора вариана структурЬ, кроме последнего, первый выход которого объединен с Е ЫХОами дешифратора и является

выходом блока задания варианта струтуры, выходы элементов ИЛИ подключены к первым входам соответствуюгцих узлов выбора варианта структуры, в :рые входы всех узлов выбора варианта структуры объединены и являются входом блока задания вариантов структуры, вторые выходы узлов выбора вариантов структуры объединены и являются первым выходом блока задания вариантов структуры.

3.Устройство по пп. 1,2, отличающееся тем, что узел выбора вариантов структуры содержит регистр, выходы которого соединены со входами дешифратора, выходы которого непосредственно подключены

к первым входам элементов И первой группы и через элементы НЕ к первым входам элементов И второй группы, вторые входы элементов И первой и второй групп подключены к выходам соответствующих триггеров, кроме последнего, а выход последнего триггед)а соединен с первым входом элемента ИЛИ, второй вход элемента ИЛИ является вторым входом узла выбора варианта структуры, соответствующие входы элемента ИЛИ подключены к выходам элементов И первой группы, выходы элементов И второй группы через элементы задержки соединены с первыми входами триггеров, кроме первого, вторые входы триггеров объединены и являются первым входом узла выбора варианта структуры, первый вход первого триггера объединен со входом элемента задержки и являет ся вторым входом узли выбора варианта структуры, выход элемента задержки подключен к выходу элемента ИЛИ и является первым выходом узла выбора варианта структуры,

4.Устройство по п. 1,о т л и чающееся тем, что блок управления содержит первый, второй и третий триггеры, генератор, первый и второй элементы И, первый, второй

и третий дешифраторы, первый и вто.рой шифраторы, первый, второй и третий счетчики, причем выход первого триггера подключен к первому, входу

первого злемёйта И, второй вход koторого соединен с выходом генератора и с первым, входом второго элемента . И, второй вход которого подключен к выходу второго триггера, первый и второй входы которого соединены соответственно с первым и вторым входами первого триггера и с первыми выходами первого и второго дешифраторов, выход второго элемента И подключен ко входу первого счетчика,

0 выход которого соединен со. входом первого дешифратора, первый выход которого подключен к первому входу третьего триггера и является первьш выходом блока управления, второй и третий- выходы первого дешифратора

5 являются соответственнр .четвертым и пятым выходами блока управления, второй вход третьего триггера объединен со входами первого шифратора и является входом блЬка Управления,

0 выход третьего-триггера соединен со входом генератора, выход первого шифратора соединен с первым входом второго счетчика, выход которого подключен ко входу второго дешифра5тора, соответствующие выходы ,которого объединены и являются вторым выходом блока управления и соединены со входами второго шифратора, выход которого подключен к первому входу

0 третьего счетчика, второй вход которого соединен с выходом первого элемента И и -является третьим выходом блока управления, выход третьего счетчика соединен со входомтретье5го дешифратора, первый выход которого подключен ко второму входу второго счетчика, асоответствующие выходы подключены ко второму выходу блока управления, второй вход пер0вого триггера является вторым входом блока управления.

Источники информации, принятые во внимание при экспертизе

5

1.Авторское свидетельство СССР № 337785, Об F 15/36 1970.

2.Авторское свидетельство СССР № 445046, МКИ G 06 F 15/20, 30.09.1974.

, |.-,.-.i®jb

,

-гЫ Й H

r

JJ.

J«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оптимизации струк-ТуРы СлОжНыХ СиСТЕМ | 1979 |

|

SU840917A1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| Устройство для сортировки данных | 1990 |

|

SU1784967A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для определения минимальных сечений графа | 1980 |

|

SU888134A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

sisty

Фае.З

ЙЦ

1

Авторы

Даты

1979-08-05—Публикация

1977-04-22—Подача