(54) УСТРОЙСТВО ДЛЯ ОПТИМИЗАЦИИ СТРУКТУРЫ СЛОЖНЫХ СИСТЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оптимизации структуры сложных систем | 1977 |

|

SU678489A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Устройство для сопряжения | 1983 |

|

SU1124277A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ МНОГОКАНАЛЬНОЙ ИЗМЕРИТЕЛЬНОЙ СИСТЕМОЙ | 2009 |

|

RU2395831C1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ СИТУАЦИЙ | 2000 |

|

RU2195703C2 |

| Устройство для программногоупРАВлЕНия | 1979 |

|

SU830310A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОЛУЧЕНИЕМ ОЦЕНКИ КАЧЕСТВА ЗНАНИЙ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2001 |

|

RU2248610C2 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

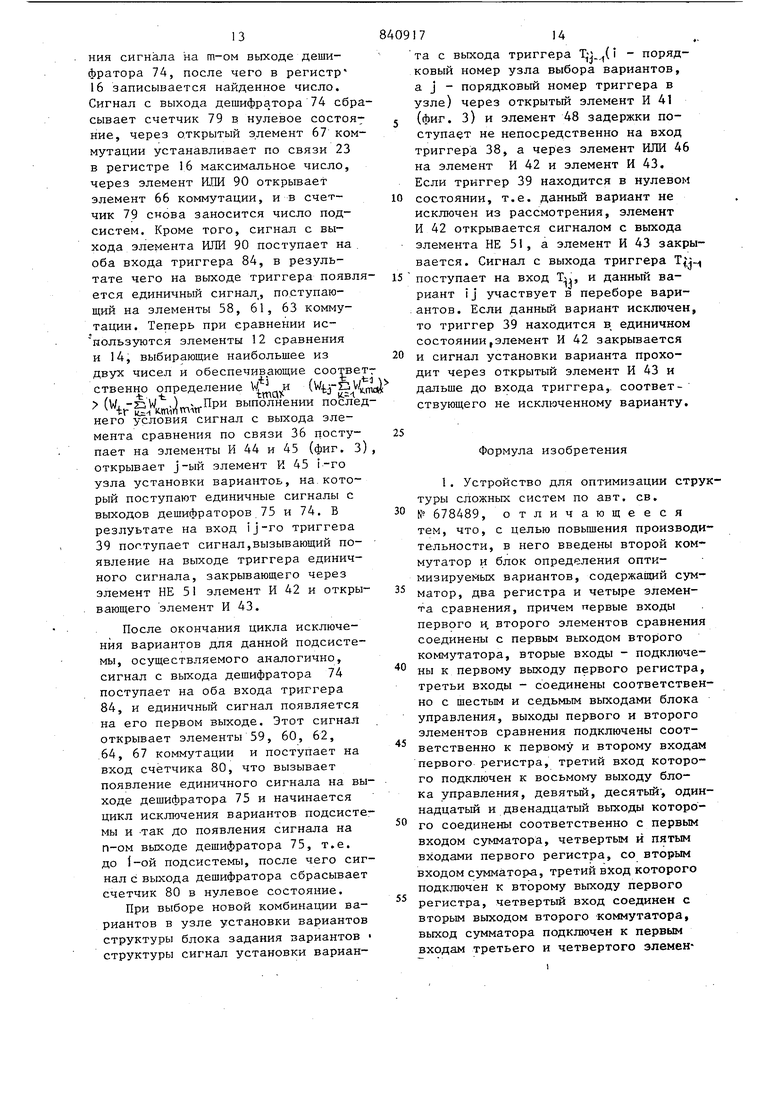

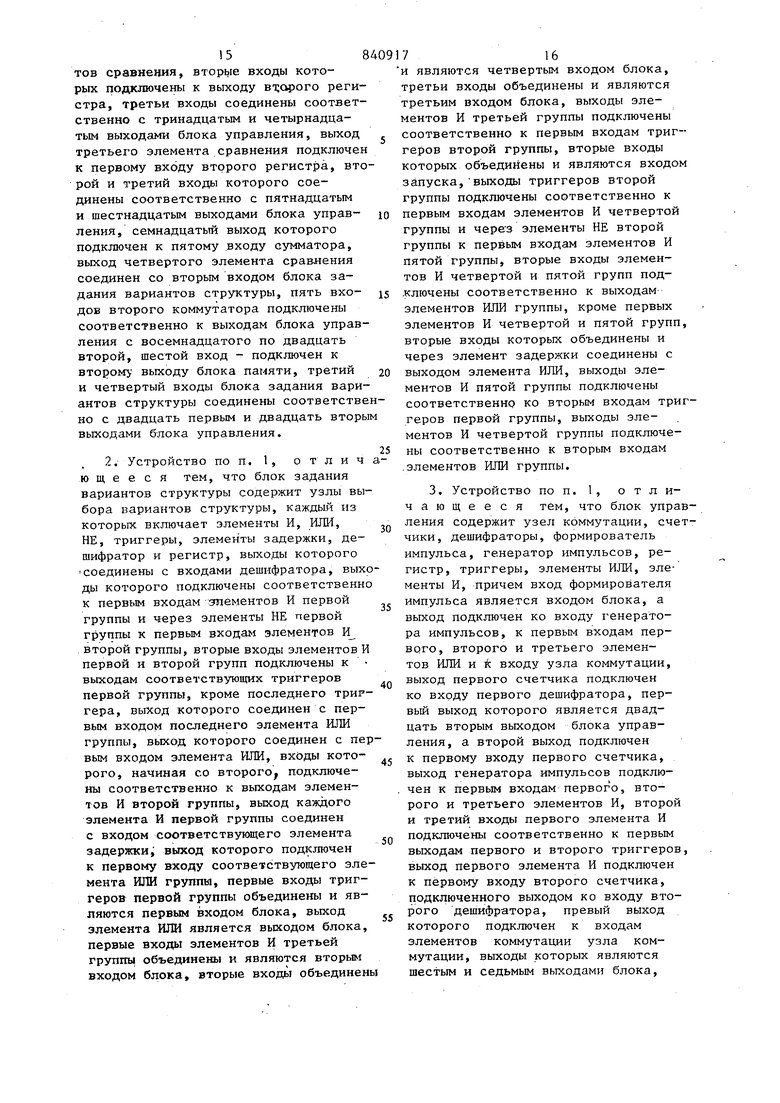

Изобретение относится к вычисли-i гельной технике и может быть исполь Зовано для конструирования сложных систем при оптимизации структуры систем, состоящих из подсистем различного типа, по критерию минимума суммарной характеристики выбранных вариантов подсистем с учетом связей между ними. По основному авт. св. № 678489 известно устройство, которое содержит блок памяти, сумматор, блок срав нения, блок выдачи результата, комму татор, блок заданиявариантов-структуры и блок управления, причем первый выход блока задания вариантов структуры подключен соответственно к первому входу блока выдачи результата и первому входу коммутатора, выход которого соединен с первым BXO дом сумматора, выход которого подклю чен к первому входу блока сравнения и ко второму входу блока выдачи резул тата, выход блока сравнения соединен С-третьим входом блока вьщачи результата, выход которого подключен ко второму входу блока сравнения, первый, второй, третий, четвертый и пятый выходы блока управления соединены соответственно со входом блока задания вариантов структуры, со вторым входом коммутатора, со вторым входом сумматора, третьим входом блока сравнения и с четвертым входом блока вьщачи результата, вход блока управления подключен ко второму выходу блока задания ва:риантов структуры, выход блока памяти соединен с третьим входом коммутатора. В известном устройстве блок задания вариантов структуры содержит регистр, выходы которого через дешифратор соединены с первыми входами элементов И, вторые входы которых объединены и являются входами блока задания вариантов структуры, выход одного элемента -И подключен к первому входу первого узла выбора ва3риантов стр,уктуры, выходы других элементов И соединены с первыми входами элементов ИЛИ, вторые входы которых подключены к первым выходам соответствующих узлов выбора вариантов структуры, кроме последнего, первый выход которого объединен. с выходами дешифратора и является вторым выходом блока задания вариантов структуры, выходы элементов ИЛИ подключены к первым входам соответствующих узлов выбора вариантов структуры, вторые входы всех узлов выбора вариантов структуры объединены и являются первым выходом блока задания вариантов структуры. Узел выбора вариантов структуры содержит регистр, выходы которого непосредственно подключены к первым входам элементов И первой.группы и через элементы НЕ к первым входам элементов И второй группы, вторые вхо ды элементов И первой и второй группы подключены к выходам соответствующих триггеров, кроме последнего, а выход последнего триггера соединен с первым входом элемента ИЛИ, второй вход эле мента ИЛИ является вторым входом узла выбора вариантовструктуры, соотв ствующие входы элемента ИЛИ подключе ны к выходам элементов И первой груп пы, -выходы элементов И второй группы через элементы задержки соединены с первь ш входами триггеров, кроме пер вого, вторые входь триггеров объединены и являются первым входом узла выбора вариантов структуры, первый вход первого триггера объединен со входом элемента задержки и является вторым входом узла выбора вариантов структу ры, выход элемента задержки подключе к выходу элемента ИЛИ и является первым выходЪм узла выбора вариантов структуры. Блок управления содержит первый, второй, третий триггеры , генератор, первьй, второй элементы И, первый, в рой, третий дешифраторы, первый, вто рой шифраторы, первый, второй, третий счетчики, причем выход первого триггера подключен к первому входу первого элементаИ, второй вход кото рого соединен с выходом генератора и с первым входом второго элемента И, второй вход которого подключен к вых ду второго триггера, первый и второй входы которого соединены соответстве но с первым и вторым входами первого 74 триггера и с первыми входами первого и второго дешифраторов, выход второго элемента И подключен ко входу первого счетчика, выход которого соединен со входом первого дешифратора, первый выход которого подключен к первому входу третьего триггера и является первым выходом блока управления, второй и третий выходы первого дешифратора являются соответственно четвертым и пятым выходами блока управления, второй выход третьего триггера объединен со входами первого -.шифратора и является входом блока управления, выход третьего триггера соединен со входом генератора, выход первого шифратора соединен с первым входом второго счетчика, выход которого подключен ко входу второго дешифратора, соответствующие выходы которого объединены и являются вторым выходом блока управления и соединены со входами второго шифратора, выход которого подключен к первому входу третьего счетчика, второй вход которого соединен с выходом первого элемента И и является третьим выходом блока управления, выход третьего счетчика соединен со входом третьего дешифратора, первый выход которого подключен ко второму входу второго счетчика, а соответствующие выходы подклзочены ко второму выходу блока управления, второй вход первого триггера является вторым входом блока управления 01Недостатком известного устройства является большое время решения задачи. Это вызвано тем, что при определении оптимальной структуры поочередно рассматриваются все комбинации имеющихся вариантов построения подсистем,. При этом рассматриваются и комбинации, содержащие варианты, из отношения которых до оптимизации можно установить, что они не входят в оптимальную структуру. Цель изобретения - повЬш1ение производительности. Поставленная цель достигается тем, что в устройство введены второй коммутатор и блок определения оптимизируемых вариантов, содержащий сумматор, два регистра и четыре элемента сравнения, причем первые входы первого и второго элементов сравнения соединены с первым выходом второго коммутатора, вторые входы - подключены к первому выходу первого регистра, третьи входы 58соединены соответственно с шестым и седьмым выходами блока управления, выходы первого и второго элементов сравнения подключены соответственно первому и второму входам первого регистра, третий вход которого подключен к восьмому выходу блока управления, девятый, десятый, одиннадцатый и двенадцатый выходы которого соединены соответственно с первым входом сумматор-а, четвертым и пятым входами первого регистра, со вторым входом сумматора, третий вход которого подключен к второму выходу первого регистра, четвертый вход соединен с вт рым выходом второго коммутатора, выход сумматора подключен к первым вхо дам третьего и четвертого элементов сравнения, вторые входы которых подключены к выходу второго регистра, третьи входы соединены соответственно с тринадцатым и четырнадцатым выходами блока управления, выход треть го элемента сравнения подключен к первому входу второго регистра, второй и третий входы которого соединен соответственно с пятнадцатым и шестнадцатым выходами блока управления, семнадцатый выход которого подключен к пятому входу сумматора, выход четвертого элемента сравнения соединен со вторым входом блока задания вариантов структуры, пять входов второго коммутатора подключены соответственно к выходам блока управления с восемнадцатого по двадцать второй, шестой вход - подключен к второму выходу блока памяти, третий и четвертый вхо ды блока задания вариантов структуры соединены соответственно с двадцать первым и двадцать- вторьм выходами блока управления. Блок задания вариантов структуры содержит узлы выбора вариантов стру туры, каждый из которых включает эле менты И, ИЛИ, НЕ триггеры, элементы задержки, дешифратор, и регистр, выхо ды которого соединены с входами деши фратора, выходы которого подключены соответственно к первым входам элеме тов И первой группы и через элементы НЕ первой группы к первым входам элементов И второй группы, вторые входы элементов И первой и второй групп подключены к выходам соответствующих триггеров первой группы, кроме послед ;него триггера, выход которого соединен с первым входом последнего элемен 76 та- ИЛИ группы, выход которого соеди- нен с первым входом элемента ИЛИ, входы которого, начиная со второго,подключены соответственно к выходам элементов И второй группы, выход каждого элемента И первой группы соединен с входом соответствующего элемента задержки, выход которого подключен к первому входу соответствующего элемента ИЛИ группы, первые входы триггеров первой группы соединены и являются первым входом блока, выход элемента ШШ является выходом блока, первые входы элементов И третьей группы объединены и являются вторым входом блока, вторые, входы объединены и являются четвертым входом блока, третьи входы объединены и являются третьим входом блока, выходы элементов И третьей группы подключены соответственно к первым входам триггеров второй группы, вторые входы которых объединены и являются входом запуска, выходы триггеров второй группы подключены соответственно к первым входам элементов И четвертой группы и через элементы НЕ второй группы к первым входам элементов-И пятой группы, вторые входы элементов И по четвертой и пятой групп подключены соответственно к выходам элементов ИЛИ группы, кроме первых элементов И четвертой и пятой групп, вторые входы которых объединены и через элемент задержки соединены с выходом элемента ИЛИ, выходы элементов И пятой группы подключены соответственно ко вторым входам триггеров первой группы, выходы элементов И четвертой группы подключены соответственно к вторым входам элементов ИЛИ группы. Блок управления содержи.т узел коммутации, счетчики, дешифраторы, формирователь импульса, генератор импульсов, регистр, триггеры, элементы ИЛИ, элементы И, причем вход формирователя импульса является вхоом блока, а выход подключен ко входу генератора импульсов, к первым входам первого, второго и третьего элементов ШШ и к входу узла оммутации, выход первого счетчика одключен ко входу первого дешифраора, первый выход которого является вадцать вторым выходом блока управ- . ения, а второй выход подключен к ервому входу первого счетчика, выкод генератора импульсов подключен

. 7.

к первым входам первого, второго и третьего элементов И, второй и третий входы первого элемента И подключены соответственно к первьм выходам первого и второго триггеров, выход .первого элемента И подключен к первому входу второго счетчика, подключенного выходом ко входу второго дешифратора, первый выход которого подключен к входам элементов коммутации узла коммутации, вь1ходы которых являются шестым и седьмым выходами блока, второй выход второго дешифратора подключен ко второму входу второго счетчика и первому выходу че вертого элемента ИЛИ, соединенного вторым входом с выходом второго элемента И, второй вход которого подключен к второму выходу первого триггера, подключенного первым входом к выходу первого элемента ИЛИ, к выходу которого подключены входы элементов коммутации узла коммутации, выходы которых являются десятым и одиннадцатым выходами блока, и вход элемента коммутации, выход которого соединен с первым входом третьего счетчика, выход четвертого элемента ИЛИ подключен к второму входу третьего счетчика, соединенного выходом со входом третьего дешифратора первый выход которого является восемнадцатым выходом блока, второй выход подключен ко второму входу первого триггера, третий выход является девятым выходом блока, четвертый выход третьего дешифратора под-ключен к третьему входу третьего счечика, к первому входу пятого элемента ИШ и к второму входу первого элемента ИЛИ, выход второго элемента ИЛИ подключен к входу узла коммутаци и к первому входу второго триггера, второй выход которого подключен ко второму входу третьего элемента И, соединенного выходом со вторым входо пятого элемента ИЛИ, выход которого подключен к первому входу четвертого счетчикаj соединенного выходом со входом четвертого дешифратора, первый выход которого является девятнадцатым выходом блока, второй выход подключен ко второму входу второго триггера, третий выход - к первому входу третьего триггера, чет вертый выход является двенадцатым выходом блока, пятый выход четвертого де111ифратора подключен ко вто -

78

рому входу третьего триггера, выход которого является двадцатым выходом блока, шестой и седьмой выходы четвертого дешифратора подключены к входам элементов коммутации узла коммутации, выходы которых являются тринадцатым, четырнадцатым и пятнадцатым .выходами блока, восьмой выход является шестнадцатым выходом блока и подключен к второму входу четвертого счетчика, к второму входу второго элемента ИЛИ и к первому входу пятого счетчика, соединенного выходом со входом пятого дешифратора, пер.вый выход которого является двадцать первым выходом блока, и второй выход подключен ко второму входу пятого счетчика, к второму входу третьего элемента ИЛИ и к входу элемента коммутации узла коммутации, выход которого является семнадцатым выходом блока, выход третьего элемента ИЛИ подключен к входам четвертого триггера и к входу элемента коммутации узла коммутации, выход которого соединен с вторым входом пятого счетчика, первый выход четвертого триггера подключен к второму входу первого счетчика и к соответствующему входу узла коммутации, второй выход четвертого триггера и выход регистра соединены соответственно с входами узла коммутации, выходы которого подключены соответственно к третьим входам первого второго и пятого счетчиков.

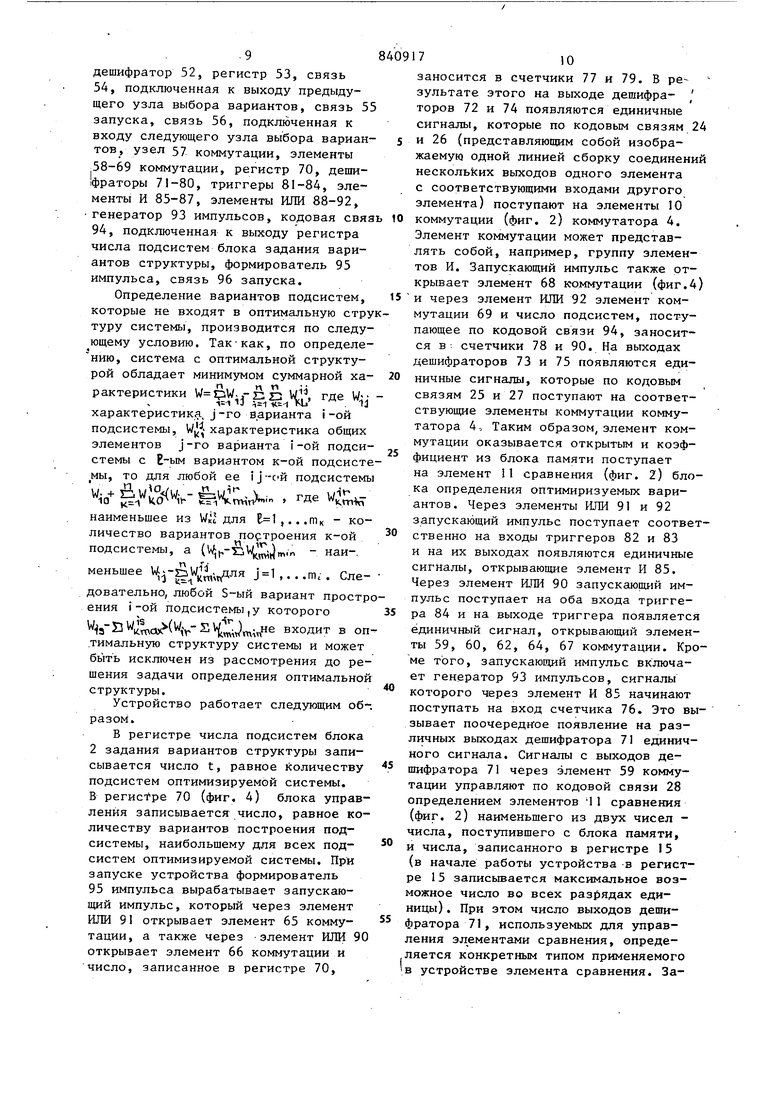

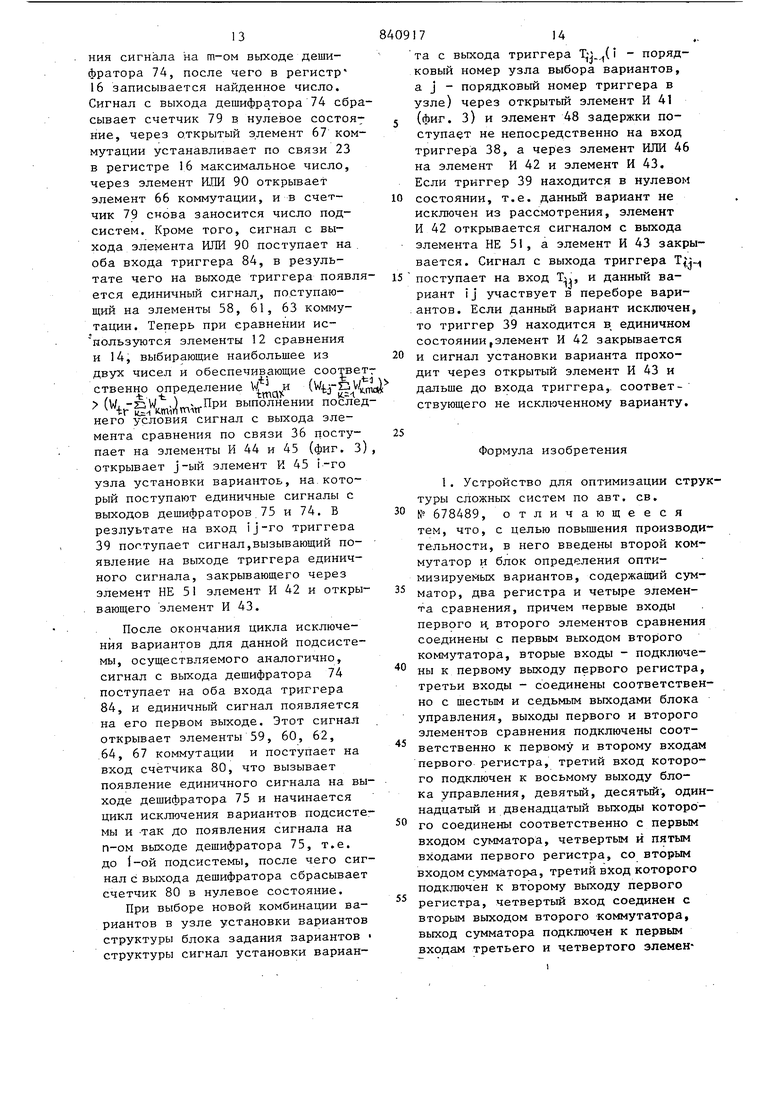

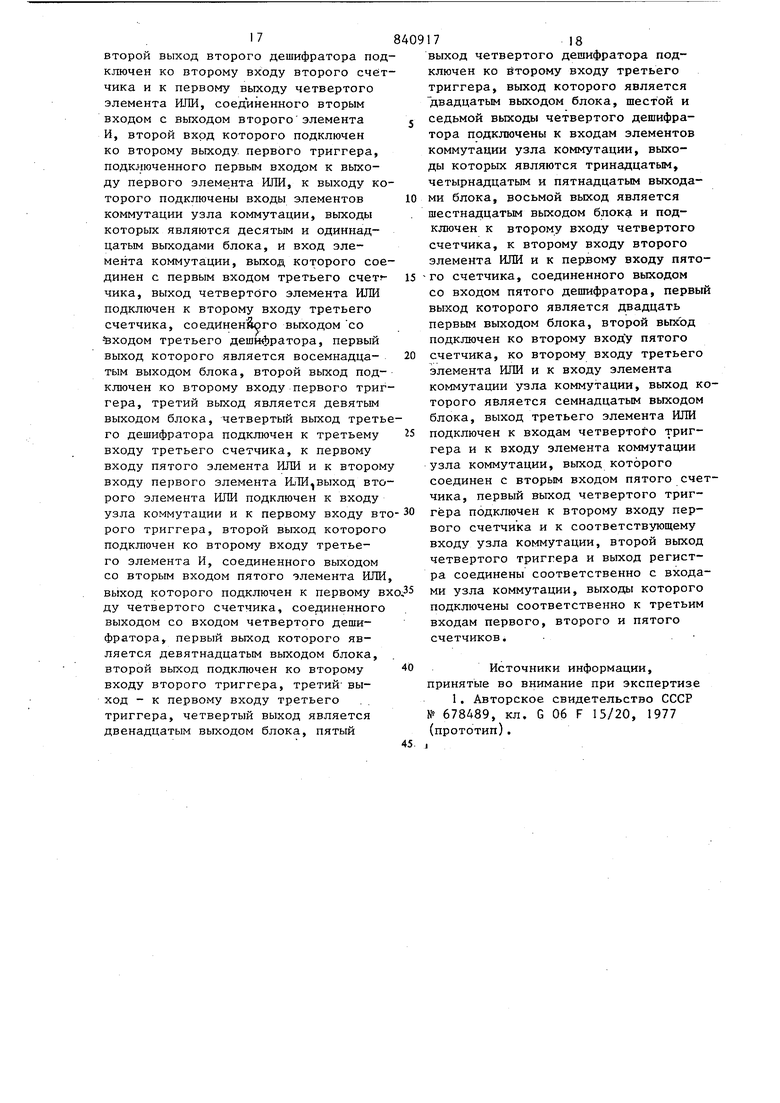

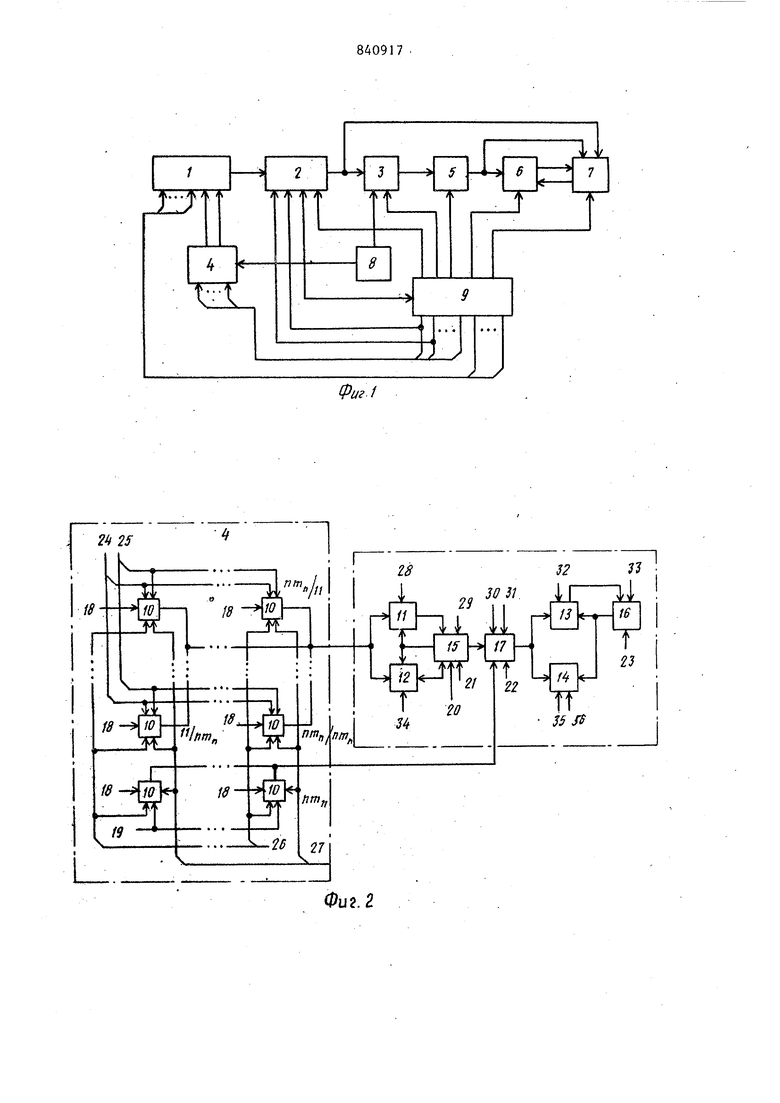

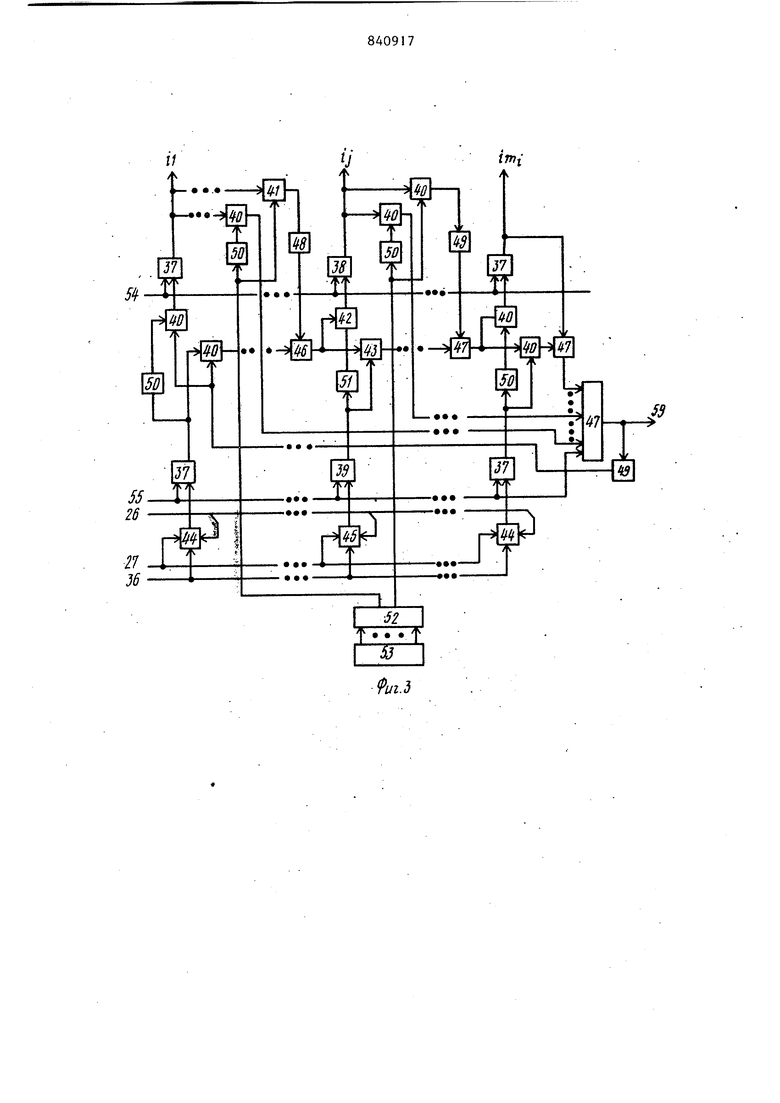

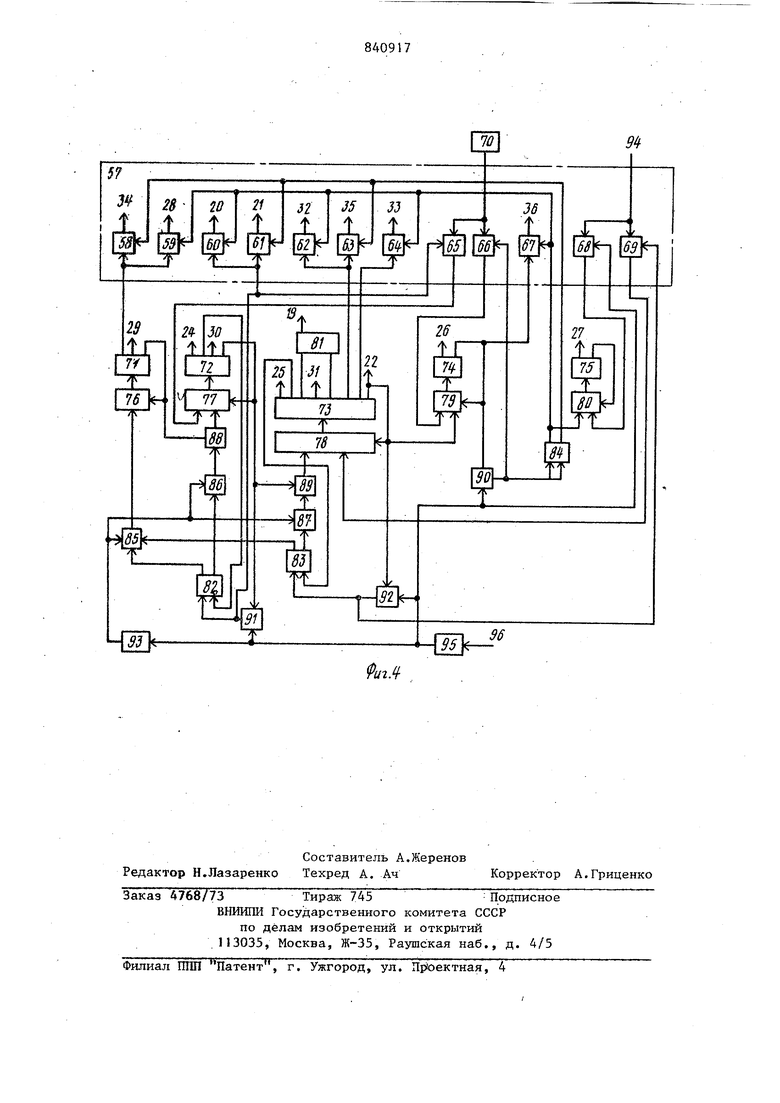

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема блока определения оптимизируемых вариантов, соединенная с коммутатором; на фиг. 3схема узла выбора вариантов структуры блока задания вариантов структуры; на фиг. А - схема блока управления.

Устройство включает блок 1 определения оптимизируемых вариантов, блок 2 задания вариантов структуры, коммутаторы 3 и 4, сумматор 5, блок 6 сравнения, блок 7 вьщачи результата, блок 8 памяти, блок 9 управления, элемент 10 коммутации, элементы 11-14 сравнения регистры 15 и 16, сумматор 17, связь 18, подключенная к ячейке блока памяти связи 19-23, кодовые связи 24 и 25, подключенные к выходам блока управления, связи 26-35, связь 36 с входом блока задания вариантов структуры, триггеры 37-39, элементы И 40-45, элементы ИЛИ 46 и 47 элементы 48 и |49 задержки, элементы НЕ 50 и 51, дешифратор 52, регистр 53, связь 54, подключенная к выходу предыдущего узла выбора вариантов, связь 55 запуска, связь 56, подключенная к входу следующего узла выбора вариантов, узел 57 коммутации, элементы |58-69 коммутации, регистр 70, дешифраторы 71-80, триггеры 81-84, элементы И 85-87, элементы ИЛИ 88-92, генератор 93 импульсов, кодовая связ 94, подключенная к выходу регистра числа подсистем блока задания вариантов структуры, формирователь 95 импульса, связь 96 запуска. Определение вариантов подсистем, которые не входят в оптимальную стру туру системы, производится по следующему условию. Так-как, по определению, система с оптимальной структурой обладает минимумом суммарной характеристики ..-Ec где ) 13 ti-i Нл . ТЗ характеристика, j-го варианта i-ой подсистемы, характеристика общих элементов j-ro варианта i-ой подсистемы с вариантом к-ой подсисте .мы, то для любой ее ij-ой подсистемы v §,.- где наименьшее из WiJt для ,...тк - количество вариантов построения к-ой подсистемы, а (Wj..v, - наи-. меньшее .ля ,. , .m. . Следовательно, любой S-ый вариант простр ения i-ой подсистемы,у которого (,)тл«ие входит в оп тимальную структуру системы и может быть исключен из рассмотрения до решения задачи определения оптимальной структуры. Устройство работает следующим образом. В регистре числа подсистем блока 2 задания вариантов структуры записывается число t, равное количеству подсистем оптимизируемой системы. В регистре 70 (фиг. 4) блока управления записывается число, равное количеству вариантов построения подсистемы, наибольшему для всех подсистем оптимизируемой системы. При запуске устройства формирователь 95 импульса вырабатывает запускающий импульс, который через элемент ИЛИ 91 открывает элемент 65 коммутации, а также через -элемент ИЛИ 90 открывает элемент 66 коммутации и число, записанное в регистре 70, 710 заносится в счетчики 77 и 79, В результате этого на выходе дешифра- ; торов 72 и 74 появляются единичные сигналы, которые по кодовым связям 24 и 26 (представляющим собой изображаемую одной линией сборку соединений нecкoльkиx выходов одного элемента с соответствующими входами другого элемента) поступают на элементы 10 коммутации (фиг. 2) коммутатора 4. Элемент коммутации может представлять собой, например, группу элементов И. Запускающий импульс также открывает элемент 68 коммутации (фиг.4) и через элемент ИЛИ 92 элемент коммутации 69 и число подсистем, поступающее по кодовой связи 94, заносится В: счетчики 78 и 90. На выходах дешифраторов 73 и 75 появляются единичные сигналы, которые по кодовым связям 25 и 27 поступают на соответствующие элементы коммутации коммутатора 4, Таким образом,элемент коммутации оказывается открытым и коэффициент из блока памяти поступает на элемент 11 сравнения (фиг. 2) блока определения оптимиризуемых вариантов. Через элементы ИЛИ 91 и 92 запускающий импульс поступает соответственно на входы триггеров 82 и 83 и на их выходах появляются единичные сигналы, открывающие элемент И 85. Через элемент ИЛИ 90 запускающий импульс поступает на оба входа триггера 84 и на выходе триггера появляется единичный сигнал, открывающий элементы 59, 60, 62, 64, 67 коммутации. Кроме того, запускающий импульс включает генератор 93 импульсов, сигналы которого через элемент И 85 начинают поступать на вход счетчика 76. Это вызывает поочередное появление на различных выходах дешифратора 71 единичного сигнала. Сигналы с выходов дешифратора 71 через элемент 59 коммутации управляют по кодовой связи 28 определением элементов Ч 1 сравнения (фиг. 2) наименьшего из двух чисел числа, поступившего с блока памяти, и числа, записанного в регистре 15 (в начале работы устройства в регистре 15 записывается максимальное возможное число во всех разрядах единицы) . При этом число выходов дептфратора 71, используемых для управления элементами сравнения, определяется конкретным типом применяемого в устройстве элемента сравнения. Затем сигнал ,со следующих выходов дешифратора управляет по кодовой связи 29 записью меньшего из двух чисел в регистр 15. Сигнал с последнего выхода дешифратора 29 сбрасывает счечик 76 в нулевое состояниенчерез элемент ИЛИ 88 поступает на вход счетчика 77, что вызывает появление единичного сигнала на соответствующем выходе дешифратора 72, Этот сигнал по связи 24, открывает требуемый элемент коммутации и коэффициент поступает на элемент 11 сравнения, где он сравнивается с числом, записанным в регистре 15, и наименьшее из них записывается в регистр 15. Так продолжается далее до появления сигнала на т-ом выходе, дешифратора 72, в результате чего на вход схемы сравнения поступает коэффициент,после чего выбор минимального значения заканчивается

Затем сигнал следующего выхода дешифратора поступает на вход- триггера 82 и на выходе триггера появляется единичный сигнал, в результате чего элемент И 85 закрывается, а элемент И 86 открывается, и сигналы генератора 93 через элемент . ИЛИ 88 начинают поступать на вход счетчика 77. Теперь единичные сигналы поочередно появляются на следующих выходах дешифратора 72, используемых для управления по связи 30 сумированием с отрицательным знаком полученного минимального значения с числом, накопленным в сумматоре 1 Сигнал, появившийся на последнем выходе дешифратора 72, сбрасывает счетчик 77 в нулевое состояние, через элемент 60 коммутации Но связи 20 устанавливает в регистре 15 максимальное число, а также через элемент ИЛИ 89 (фиг. 4) поступает на вход счетчика 78, в результате чего на выходе дешифратора 73 появлется единичный сигнал, который постпает на соответствующий элемент коммутации. Кроме того, сигнал с последнего выхода дешифратора 72 открывает; элемент коммутации 65 и число из регистра 70 снова заносится в счетчик 77, этот же сигнал че .рез элемент ИЛИ 91 переводит тригге 82 в новое состояние, после чего сигналы генератора 93 начинают поступать через элемент И 85 на счетчик 76 и начинается цикл значений коэффициента W .аналогичный описанному. Лосле чего,

как будет подсчитана .(единичный сигнал появляется на выходе дешифратора 73 и поступает на вход триггера 83. В результате элемент И 85 закрывается, а элемент И 87 открывается и сигналы

генератора 93 начинают поступать на вход счетчика 78. На следующем выходе дешифратора 73 появляется сигнал, поступающий на вход триггера 81, на выходе которого появляг тся сигнал, открывающий по связи 19 элемент 10 коммутации, и,на вход сумматора 17 из блока памяти поступает коэффициент. Сигналы со следующих выходов дешифратора 73 поступают по связи 31 на вход сумматора 17 и управляют суммированием коэффициентов. Сигнал со следующего выхода дешифратора 73 изменяет сое- . тояние триггера 81 и элемент коммутации закрывается. Затем сигналы со следующих выходов дешифратора 73 через открытый элемент коммутации 62 управляют по связи 32 выбором элементов 13 сравнения наименьшего из двух чисел, поступающего с сумматора 17 и записанного в регистре 16 (в начале цикла определения в регистре записано максимальное число).

Сигналы следующих выходов дешифратора через открытые элементы 64 коммутации управляют по связи 33 записью наименьшего из сравниваемых чисел в регистр 16.

Сигнал с последнего выхода дешифратора 73 сбрасывает счетчик 78 и по связи 22 сумматор 17 в нулевое состояние, а также через элемент ИЛИ 92 открывает элемент 69 коммутации, и число снова заносится в счетчик 78. Одновременно сигнал с последнего выхода дешифратора 73 поступает на вход счетчика 79, после чего, на выходе дешифратора 74

появляется единичный сигнал, которьй по связи 26 поступает на элемент коммутации. Кроме того, сигнал с. выхода элемента ИЛИ 92 поступает на вход триггера 83, и в

результате элемент И 87 закрывается, элемент И 85 открывается и начинается цикл определения наименьшего из двух чисел и так до появления сигнала на т-ом выходе дешифратора 74, после чего в регистр 16 записывается найденное число. Сигнал с выхода дешифратора 74 сбр сывает счетчик 79 в нулевое состоя ние, через открытый элемент 67 ком мутации устанавливает по связи 23 в регистре 16 максимальное число, через элемент ИЛИ 90 открывает элемент 66 коммутации, ив счетчик 79 снова заносится число подсистем. Кроме того, сигнал с выхода элемента ИЛИ 90 поступает на оба входа триггера 84, в результате чего на выходе триггера появл ется единичный сигнал,, поступающий на элементы 58, 61, 63 коммутации. Теперь при сравнении используются элементы 12 сравнения и 14, выбирающие наибольшее из двух чисел и обеспечивающие соотве Uo. ственно определение W, .и (W A-SHV (4j-p) ( выполнении после него условия сигнал с выхода элемента сравнения по связи 36 поступает на элементы И 44 и 45 (фиг, З открывает j-ый элемент И 45 i-го узла установки вариантов, на который поступают единичные сигналы с выходов дешифраторов 75 и 74. В резлуьтате на вход ij-ro триггера 39 поступает сигнал,вызывающий появление на выходе триггера единичного сигнала, закрывающего через элемент НЕ 51 элемент И 42 и откры вающего элемент И 43. После окончания цикла исключения вариантов для данной подсистемы, осуществляемого аналогично, сигнал с выхода дешифратора 74 поступает на оба входа триггера 84, и единичный сигнал появляется на его первом выходе. Этот сигнал открывает элементы 59, 60, 62, 64, 67 коммутации и поступает на вход счетчика 80, что вызывает появление единичного сигнала на вы ходе дешифратора 75 и начинается цикл исключения вариантов подсисте мы и -так до появления сигнала на п-ом выходе дешифратора 75, т.е. до 1-ой подсистемы, после чего сиг нал с выхода дешифратора сбрасывает счетчик 80 в нулевое состояние. При выборе новой комбинации вариантов в узле установки вариантов структуры блока задания вариантов структуры сигнал установки вариан1714 та с выхода триггера Xfj.,( i - порядковый номер узла выбора вариантов, а j - порядковый номер триггера в узле) через открытый элемент И 41 (фиг. З) и элемент 48 задержки поступает не непосредственно на вход триггера 38, а через элемент ИЛИ 46 на элемент И 42 и элемент И 43. Если триггер 39 находится в нулевом состоянии, т.е. данный вариант не исключен из рассмотрения, элемент И 42 открывается сигналом с выхода элемента НЕ 51, а элемент И 43 закрывается . Сигнал с выхода триггера Т| поступает на вход Ъч, и данный вариант ij участвует в переборе вариантов. Если данный вариант исключен, то триггер 39 находится в единичном состоянии,элемент И 42 закрывается и сигнал установки варианта проходит через открытый элемент И 43 и дальше до входа триггера,, соответствующего не исключенному варианту. Формула изобретения 1. Устройство для оптимизации структуры сложных систем по авт. св. № 678489, отличающееся тем, что, с целью повьш1ения производительности, в него введены второй коммутатор и блок определения оптимизируемых вариантов, содержащий сумматор, два регистра и четыре элемента сравнения, причем первые входы первого и, второго элементов сравнения соединены с первым выходом второго коммутатора, вторые входы - подключены к первому выходу первого регистра, третьи входы - соединены соответственно с шестым и седьмым выходами блока управления, выходы первого и второго элементов сравнения подключены соответственно к первому и второму входам первого регистра, третий вход которого подключен к восьмому выходу блока управления, девятьш, десятый, одиннадцатый и двенадцатый выходы которого соединены соответственно с первым входом сумматора, четвертым и пятым входами первого регистра, со вторым ходом сумматора, третий вход которого подключен к второму выходу первого регистра, четвертый вход соединен с вторым выходом второго коммутатора, выход сумматора подключен к первым входам третьего и четвертого элемен15тов сравнения, вторые входы которых подключены к выходу вт орого реги стра, третьи входы соединены соответ ственно с тринадцатым и четырнадцатым выходами блока управления, выход третьего элемента сравнения подключе к первому входу второго регистра, вт рой и третий входы которого соединены соответственно с пятнадцатым и шестнадцатым выходами блока управления, семнадцатый выход которого подключен к пятому входу сумматора, выход четвертого элемента сравнения соединен со вторым входом блока задания вариантов структуры, пять входов второго коммутатора подключены соответственно к выходам блока управ ления с восемнадцатого по двадцать второй, шестой вход - подключен к второму выходу блока памяти, третий и четвертый входы блока задания вари антов структуры соединены соответств но с двадцать первым и двадцать втор выходами блока управления. 2. Устройство по п. 1, отлич ющееся тем, что блок задания вариантов структуры содержит узлы вы бора вариантов структуры, каждый из которых включает элементы И, ИЛИ, НЕ, триггеры, элементы задержки, де шифратор и регистр, выходы которого Соединены с входами дешифратора, вы ды которого подключены соответственн к первым входам :зг(ементов И первой группы и через элементы НЕ первой группы к первьм входам элементов И второй группы, вторые входы элементов первой и второй групп подключены к выходам соответствующих триггеров первой группы, кроме последнего триг гера, выход которого соединен с первым входом последнего элемента ИЛИ группы, выход которого соединен с пе вым входом элемента ИЛИ, входы которого, начиная со второго подключены соответственно к выходам элементов И второй группы, выход каждого элемента И первой группы соединен с входом соответствующего элемента задержки; выход которого подключен к первому входу соответствующего эл мента ИЛИ группы, первые входы триггеров первой группы объединены и являются первым входом блока, выход элемента ИЛИ является выходом блока первые входы элементов И третьей группы объединены и являются вторым входом блока, вторые входь объедине 716 и являются четвертым входом блока, третьи входы объединены и являются третьим входом блока, выходы элементов И третьей группы подключены соответственно к первым входам триггеров второй группы, вторые входы которых объединены и являются входом запуска,выходы триггеров второй группы подключены соответственно к первым входам элементов И четвертой группы и через элементы НЕ второй группы к первым входам элементов И пятой группы, вторые входы элементов И четвертой и пятой групп подключены соответственно к выходам элементов ИЛИ группы, кроме первых элементов И четвертой и пятой групп, вторые входы которых объединены и через элемент задержки соединены с выходом элемента ИЛИ, выходы элементов И пятой группы подключены соответственно ко вторым входам триггеров первой группы, выходы элементов И четвертой группы подключены соответственно к вторым входам .элементов ИЛИ группы. 3. Устройство по п. 1, отличающееся тем, что блок управления содержит узел коммутации, счетчики, дешифраторы, формирователь импульса, генератор импульсов, регистр, триггеры, элементы ШШ, элементы И, причем вход формирователя импульса является входом блока, а выход подключен ко входу генератора импульсов, к первым входам первого, второго и третьего элементов ИЛИ и к входу узла коммутации, выход первого счетчика подключен ко входу первого дешифратора, первьш выход которого является двадцать вторым выходом блока управления, а второй выход подключен к первому входу первого счетчика, выход генератора импульсов подключен к первым входам первого, второго и третьего элементов И, второй и третий входы первого элемента И подключены соответственно к первьм выходам первого и второго триггеров, выход первого элемента И подключен к первому входу второго счетчика, подключенного выходом ко входу второго дешифратора, превый выход которого подключен к входам элементов коммутации узла коммутации, выходы которых являются шестым и седьмым выходами блока.

второй выход второго дешифратора подключен ко второму входу второго счбтчика и к первому выходу четвертого элемента ИЛИ, соединенного вторым входом с выходом второгоэлемента И, второй вход которого подключен ко второму выходу, первого триггера, подключенного первым входом к выходу первого элемента ИЛИ, к выходу которого подключены входы элементов коммутации узла коммутации, выходы которых являются десятым и одиннадцатым выходами блока, и вход элемента коммутации, выход которого соединен с первым входом третьего чика, выход четвертого элемента ИЛИ подключен к второму входу третьего счетчика, соедйненйрго выходом со - входом третьего дешифратора, первый выход которого является восемнадцатым выходом блока, второй выход подключен ко второму входу первого триггера, третий выход является девятым выходом блока, четвертый выход третьего дешифратора подключен к третьему входу третьего счетчика, к первому входу пятого элемента ИЛИ и к второму входу первого элемента ИлТИ выход второго элемента ИЛИ подключен к входу узла коммутации и к первому входу вто рого триггера, второй выход которого подключен ко второму входу третьего элемента И, соединенного выходом со вторым входом пятого элемента ИЛИ, выход которого подключен к первому вх ду четвертого счетчика, соединенного выходом со входом четвертого дешифратора , первый выход которого является девятнадцатым выходом блока, второй выход подключен ко второму входу второго триггера, третий выход - к первому входу третьего триггера, четвертый выход является двенадцатым выходом блока, пятый

выход четвертого дешифратора подключен ко йторому входу третьего триггера, выход которого является двадцатым выходом блока, шестой и седьмой выходы четвертого дешифратора подключены к входам элементов коммутации узла коммутации, выходы которых являются тринадцатым, четырнадцатым и пятнадцатым выходами блока, восьмой выход является шестнадцатым выходом блока, и подключен к второму входу четвертого счетчика, к второму входу второго элемента ИЛИ и к первому входу пятого счетчика, соединенного выходом со входом пятого дешифратора, первы выход которого является двадцать первым выходом блока, второй выход подключен ко второму входу пятого счетчика, ко второму входу третьего элемента ИЛИ и к входу элемента коммутации узла коммутации, выход кторого является семнадцатым выходом блока, выход третьего элемента ИЛИ подключен к входам четвертого триггера и к входу элемента коммутации узла коммутации, выход которого соединен с вторым входом пятого счечика, первый выход четвертого триггера подключен к второму входу первого счетчика и к соответствующему входу узла коммутации, второй выход четвертого триггера и выход регистра соединены соответственно с входами узла коммутации, вьгходы которого подключены соответственно к третьим входам первого, второго и пятого счетчиков.

Источники информации, принятые во внимание при экспертизе

Фиг. 2 SfП

Авторы

Даты

1981-06-23—Публикация

1979-09-12—Подача