(54) УСГРОЯСТЗО ДЛЯ СЛОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1977 |

|

SU682894A1 |

| Устройство для сложения | 1980 |

|

SU920709A1 |

| Устройство для сравнения чисел | 1981 |

|

SU959066A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Вычитающее устройство | 1979 |

|

SU771668A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Устройство для сложения | 1981 |

|

SU991415A1 |

| Система для трансляции с проблемноориентированного языка | 1976 |

|

SU674028A1 |

| Устройство для прямого и обратного преобразования кода системы остаточных классов в двоичный код | 1982 |

|

SU1075254A1 |

Изобретение относится к области цифровой вычислительной техники и предназначено для вычисления алгебраической суммы двух чисел, представленных в прямом двоичном коде.

И-звестны устройства, реализующие операции сложения и вычитания двух чисел, содержащие генератор импульсов счета, несколько счетчиков-рагистров, а также логические , управляющие процессом вычислений 1 .

Устройства эти имеют недостатки.. заключающиеся в там, что в них используется сравнительно большой объем оборудования, а в некоторых требуется предварительное преобразование прямых кодов слагаемых в обратный код.

Из известных устройств наиболее близким по технической сущности является устройство для сложения 12, Данное устройство содержит два регистра, один из которых счетный, соединенные своими выходами через схему сравнения с входом вентиля, второй вход которого подключен к выходу ге нератора импульсов, а выход - к выг:одам счетного регистра, а также третьего, дополнительного счетчика-регистра.

Недостатком данного устройства является то, что оно может оперировать только положительными числами, а при вычислении разности необходима предварительная селекция большего из чисел.

Целью предлагаемого изобретения является расширение функциональных возможностей устройства в смысле обеспечения выполнения действий сложения и вычитания над числами с любыми знаками, то есть возможность алгебраического сложения.

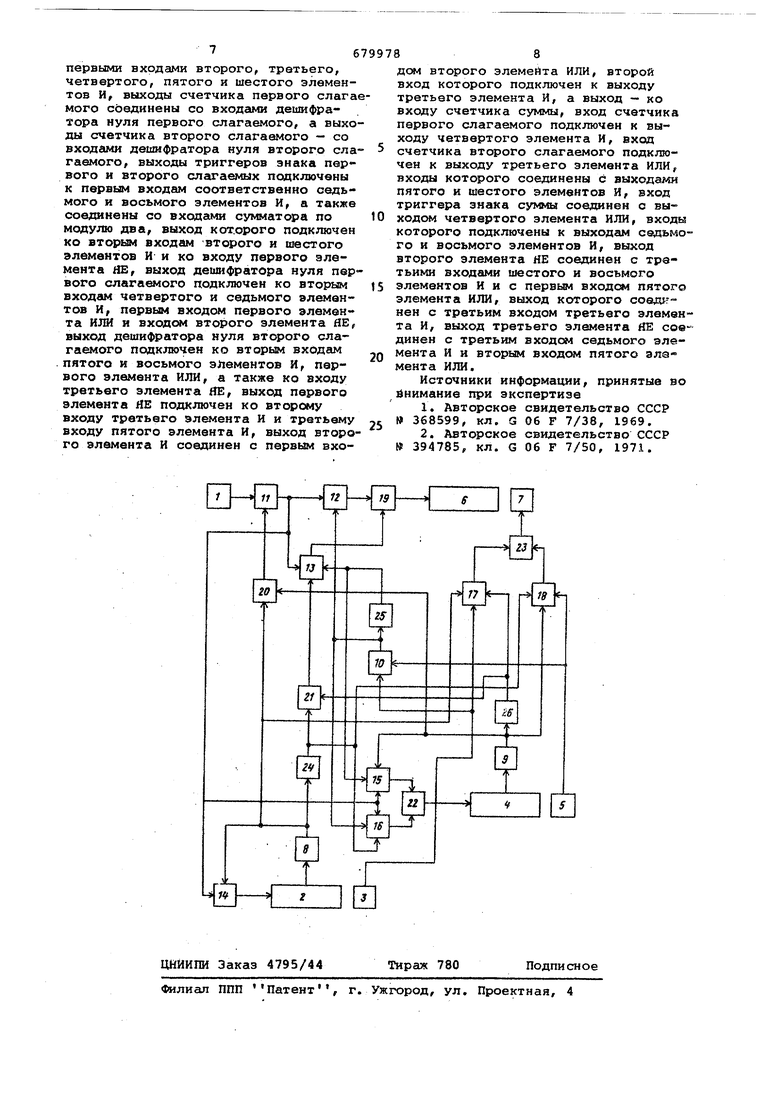

Для достижения поставленной цели, устройство для сложения дополнительно содержит сумматор по модулю два, триггеры знаков слагаемых и суммы, дешифраторы нуля первого и второго слагаемых, элементы И, ИЛИ и НЕ, причем второй вход первого злемента И соединен с выходом первого элемента ИЛИ, а выход - с первыми входагж второго, третьего, четвертого, пятого и шестого элементов И, выходы счетчика первого слагаемого соадине™ ны со входами дешифратора нуля первого слагаемого, а выходы счетчика второго слагаемого - со входами дешифратора нуля второго слагаемого, выходы триггеров знака первого и вто рого слагаемых подключены к пераык5 входам соответственно седьмого и восьмого элементов И, а также соединены со входами cyMiviaTopa по модулю два, выход которого подключен ко вторым входам второго и шестого эле,мектов И и ко входу первого элемента НЕ, выход дешифратора нуля первого слагаемого подключен ко вторым входам четвертого и седьмого элементов И, первым входом первого элемента ИЛИ и входом второго элемента ЯЕ, выход дешифратора нуля второго слага емого подключен ко вторьм входам пятого и восьмого элементов И, первого элемента ИЛИ а также ко входу треть го элемента НЕ, выход первого элемен та НЕ подключен ко второму входу третьего элемента И и третьему входу пятого элемента И, У а выход - ко входу счетчика суммы, вход счетчика первого слагаемого подключен к выход четвертого элемента И, вход счетчика второго слагаемого подключен к выход третьего элемента ИЛИ, входы которого соединены с выходалш пятого и шес того элементов И, вход триггера знак суммы соединен с выходом четвертого элемента ИЛИ, входы которого подключены к выходам седьмого и восьмого элементов Hj, выход второго элемента riE соединен с третьими входами шестого и восьмого элементов И и с первым входом пятого элемента ИЛИ, выход которого соединен с третьим входом третьего элемента И, выход третьего элемента НЕ соединен с третьим входом седьмого элемента И и вторым входом пятого элемента ИЛИ Выход второго элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу третьего элемента И, На чертеже представлена структ;,грная схема предлагаемого устройства. Устройство содержит генератор 1 импульсов, вычитающий счетчик 2 первого слагаемого, в который запигллвается модуль первого слагавмого, триггер 3 знака первого слагаемого,вычитающий счетчик 4 второго слагав™ мого, в которьзй эаписьшается модуль второго слагаемого, триггер 5 знака второго слагаемого, суммирующий счетчик б суммы, триггер 7. знака суммы, дешифраторы 8 и 9 нуля соответственно первого и второго слагаемых, сумматор 10 по Monyjm .два, элв менты И , элементы ИЛИ 19-23, элементы НЕ 24-26, Работу устройства рассмотрим, сначала для случая, когда знаки слагаемых не совпадают. Заметим, что в случае алгебраического сложения двух чисел с раэньгми знакс1Ми модуль суммы равняется разности между болыяим и меньшим МОДУЛЯ1-1И слагаемых, а знак совпадает со знаком слагаемого с большим модулем. Покажем, как данное положение реализуется в предлагаемом устройстве. Пусть в счетчики 2 и 4 записаны слагаемые с несовпадающими знаками, а счетчик б приведен в нулевое состояние. Тогда на выходах дешифраторов 8 и 9 образуется разрешающий уровень напряжения, а на выходе сумматора 10 по модулю два образуется запрещающий уровень. Разрешающий уровень с выхода дешифратора 8 подается на элементы И 14 и 17, а также на элементы ИЛИ 20 и НЕ 24. Разрешающий уровень с выхода дешифратора 9 подается на элементы И 15 и 18, а также на элемент ИЛИ 20 и ЙЕ 26, Запрбцдсшщий уровень с выхода сумматора 10 по модулю два подается на элементы И 12 и 16, а также на элемент ЯЕ 25.При этом на выходе элемента ИЛИ 20образуется разрешающий уровень, а на выходе элемента ИЛИ 21 запрешающий уровень, который подается на вход элемента И 13, на другой вход которого с выхода элемента НЕ 25 подается разрешающий уровень. С выхода элемента НЕ 25 разрешающий уровень поступает также на вход элемента И 15, Запрещающий уровень с выхода элемента НЕ 24подается также на входы элементов И 16 и 18, а запрешающий уровень с выхода элемента НЕ 26 подается на элемент И 17. Заметим, что на неупомянутые выше входы элементов И 17 и 18 поданы уровни напряжений G единичных выходов триггеров 3 и 5 соответственно. Разрешающим уровнем, снимаемым с выхода элемента ИЛИ 20, элемент И ц отпирается, обеспечивая поступление испульсов счета на входы элементов И 12 и 13, заперных уровнями напряжений с выходов суъшатора 10 по модулю два, и элемента ИЛИ 21соответственно, Иг тульсы счета поступают такясе на открытые элементы И 14 и 15, а также на закрытый элемент И 16. С выхода элемента И 14 импульсы счета поступают на счетный вход счетчика 2, а с выхода элемента ,И 15 через элемент ИЛИ 22 - на счетный вход счетчика 4. Тем Сс1мым обеспечивается синхронное вычитание единиц с модулей обоих слагae tыx. Как только счетчик одного из слагаемых обнулится (в этот момент в счетчике другого слагаемого будет сформирована разность модулей слагаемых) , счетный вход его запрещающим уровнем, снимаемым с выхода соответстБ:,1ощего дешифратора нуля, блокируется, на выходе элемента ИЛИ 21 образуется разрешаюгдий уровень, который открывает элемент И 13, и импуль сы счета через элемент ИЛИ 19 начи нают поступать на счетный вход счетчика 6 до тех пор, пока счетчик слагаемого сбольшим модулем тоже не обнулится. Тогда на выходе элемента ИЛИ 20 мы получим запрещающий уровень (так как уже на обоих его входах будет запреьцающий уровень) , и элемент И 11 остановит счет. В счетчике 6 получена разность модулей слагаемых.

Допустим, что первым обнуляется счетчик 2. Тогда на выходе дешифратора 8 уровень напряжения становится запрешакхиим, а на выходе элемента НЕ 24 - разрешающим. Этот уровень подается на вход элемента И 18, на одном из входов которого уже имеется раэрешающий уровень с выхода дешифратора 15 9, а на другой вход подан уровень с единичного плеча триггера 5. Если триггер 5 находится в нулевом состоянии (слагаемое с большим модулем, записанное в счетчик 4, положительно), элемент И 18 не сработает и тригрег 7 не изменит свого исходного нулевого состояния, и знак суммы получится отрицательным. Заметим, что по обнулении счетчика 4, знак обнулившегося ранее слагаемого (то есть информация записанная в триггере 3) уже не перепишется в триггер 7, так как элемент И 17 по обнулении счетчика 2 будет сблокирован запрещающим уровнем напряжения, снимаемым с выхода дешифратора 8. Если же ранее обнулится счетчик 4, разрешающий уровень напряжения с выхода элемента НЕ 26 посредством элементов И 17 и ИЛИ 23 перепишет информацию относительно знака слагаемого, записанного в триггере 3 в триггер 7, обеспечив при этом соот ветствие знака алгебраической суъФ1ы знаку слагаемого с большим модулем. Запрешающий уровень с выхода дешифратора 9 при этом сблокирует поступление информации относительно знака слагаемого с меньшим модулем в триггер 7 . Таким образом получаем прямой код алгебраической суммы. Рассмотрим теперь случай, когда знаки слагаемых совпадают. Заметим, что в случае алгебраического сложения двух чисел с одинаковыми знаками модуль суммы равняется сумме модулей слагаемых, а знак совпадает со знаками слагаемых. Данное положение в предлагаемом устройстве реализуется посредством последовательного перевода сначала модуля, записанного в счетчике 2, затем модуля, записанного в счетчике 4, в счетчик 6. Формирование знака осуществляется при этом так же, как и в случае несовпадения знаков слагаемых. Естест™ венно, что в этом случае в силу последовательности в обнулении счетчико 2 и 4 знак алгебраической суммы будет совпадать со знаком слагаемого, записанного в триггере 5 (знак слага

мого, записанный в триггере 3, имеет тот же знак).

При записи чисел с совпа,цающими знаками Б счетчики 2 и 4 соответственно уровни напряжений на выходах элементов схемы установятся такими же, как и при описан юм выше случав несовпадения знаков слагае Щ1х, за исключением уровней напряжений на выходе су - матора 10 по модулю два и, как следствие, на выходе элемента НЕ 25, которые меняются на противоположные. В силу этого на все время счета элементы Н 13 и 15 блокируются элемент И 12 отпирается, а элемент Vi 16 подготавливается к отпиранию по обнулении счетчика 2. Разрешающий уровень напряжения с выхода элемента ИЛИ 20 отпирает элемент И 11, и импульсы счета поступают на счетные входы счетчиков 2 и 6. По обнулении счетчика 2 в счетчике б получаем модуль первого слагаемого, при этом высоким уровнем напряжения, снимаемым с выхода элемента ЯЕ 24, отпирается элемент И 16 и начинается сложение содержимого счетчика 4 (модуля второго слагаемого) с уже введенным в счетчик 6 модулем первого слагаемого. Когда обнулится счетчик 4, на выходе элемента ИЛИ 20 получаем запрешающий уровень напряжения, который будучи поданным на вход элемента И 11 останавливает счет, В счетчике 6 получен прямой двоичный код алгебраической сумьты. Предлагаемое устройство позволяет получать алгебраическую двух двоичных чисел, представленных в прямом двоичном коде, что не обеспечивается ни в одном из известных устройств для сложения, построенных на счетчиках. Благодаря предложенному техническому решению обеспечивается существенное расширение функциональных возможностей сумматора, в которых вычисления организуются посредством счетчиков-регистров. Формула изобретения Устройство для сложения, содержащее генератор импульсов, счетчики первого и второго слагаемых, счетчик суммы, первый элемент И, первый вход которого соединен с выходом генератора импульсов, отлич ающее с я тем, что, с целью расширения функциональных возможностей устройства, заключающемся в возможности алгебраического сложения, устройство содержит дополнительно сумматор по модулю два, триггеры знаков слагаемых и , дешифраторы нуля первого и второго слагаемых, элементы И, ИЛИ и НЕ, причем второй вход первого элемента И соединен с выходом первого элемента ИЛИ, а выход - с

Авторы

Даты

1979-08-15—Публикация

1977-03-14—Подача