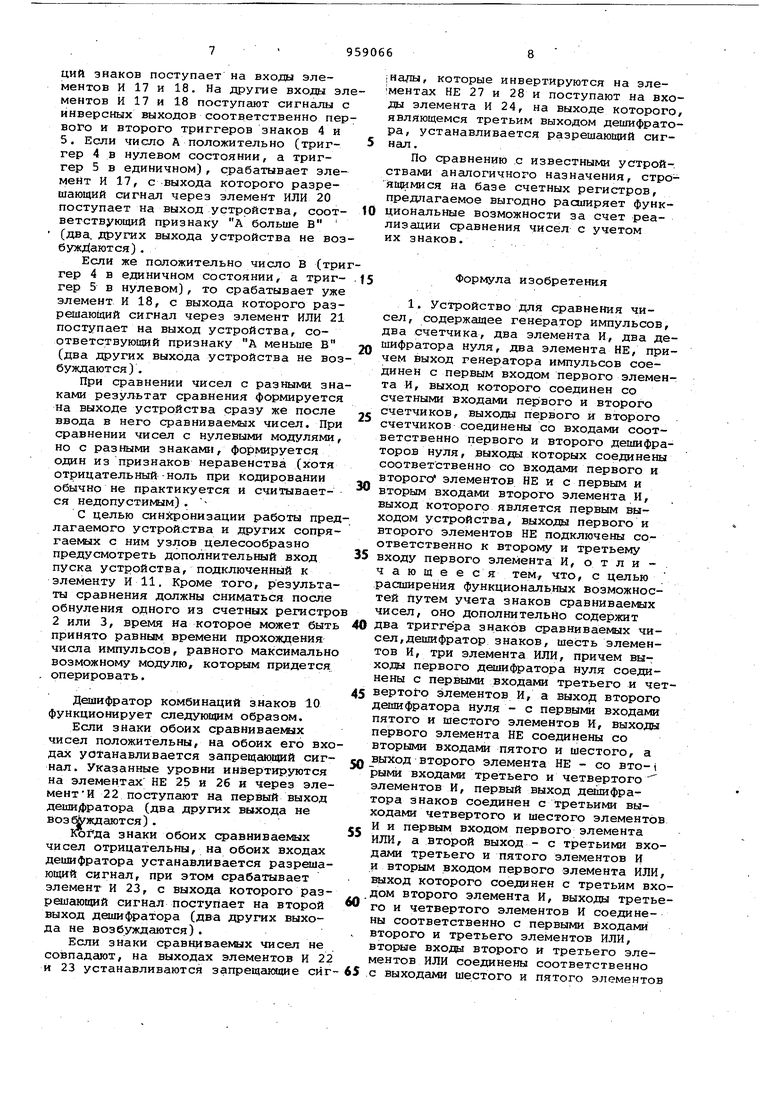

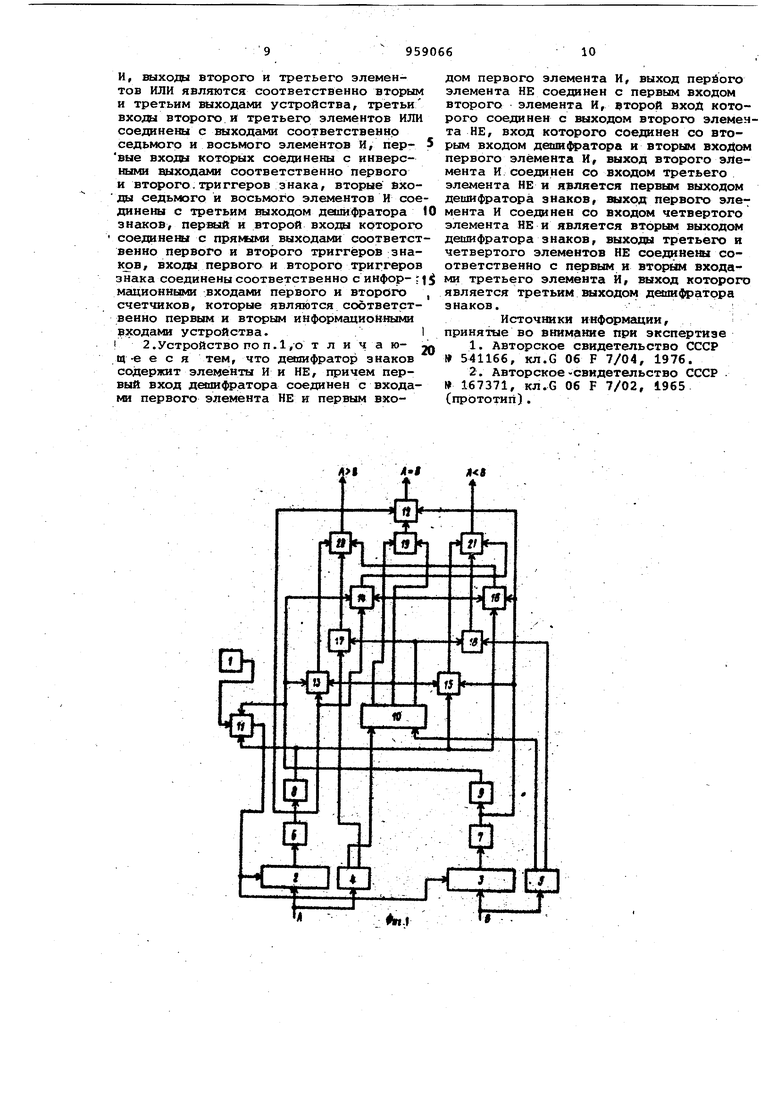

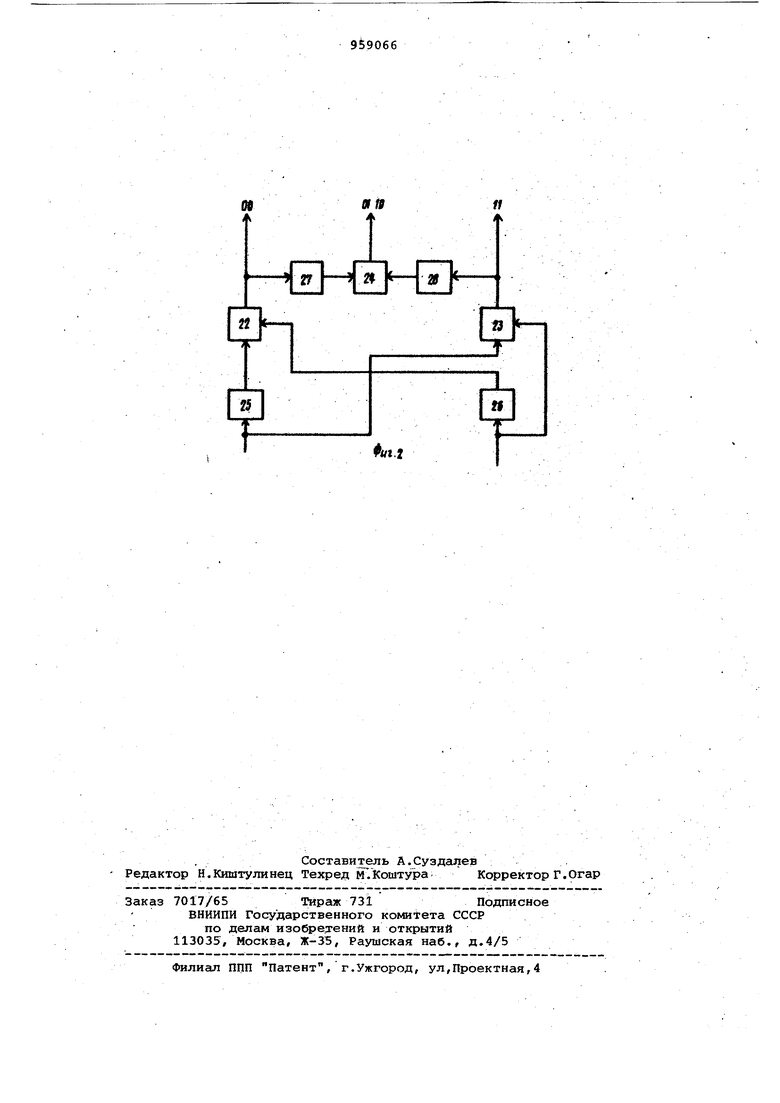

го и второго дешифраторов нуля, выходы которых соединены соответственно со входами первого и второго элементов НЕ и с первым и вторым выхода ми второго элемента И, выход которого является первым выходом устройства, выходы первого и второго элементов НЕ подключены соответственно к второму и третьему входу первого эле мента И, содержит два триггера знаков сравниваемых чисел, дешифратор знакоэ ,L4ecTb элементов И,три элемента ИЛИ, причем выходы первого дешифрато нуля соединены с первыми входами третьего и четвертого элементов И, а выход второго дешифратора нуля - с первыми входами пятого и шестого эле ментов И, выходы первого элемента НЕ соединены соответственно со вторы ми входами пятого и шестого, а выхо второго элемента НЕ - со вторыми вхо дами третьего и четвертого элементов И, первый ВЫХОД-дешифратора знаков соединен с третьими входами четверто го и шестого элементов И и первым входом первого элемента ИЛИ, а второ выход - с третьими входами третьего и пятого элементов И и вторым входом первого элемента ИЛИ, выход которого соединен с третьим входом второго элемента И, выходы третьего и четвертого элементов И соединены соответствейно с первыми входами второго и третьего элементов ИЛИ,- вторые вхо ды второго и третьего элементов ИЛИ соединены соответственно с выходами шестого и пятого элементов И, выходы второго и третьего элементов ИЛИ являются соответственно вторым и третьим выходами устройства, третьи входы второго и третьего элементов ИЛИ соединены с выходами соответственно седьмого и восьмого элементов И, первые входы которых соединены с инверсными выходами соответственно первого и второго триггеров.знака, вторые входы седьмого и восьмого элементов И соединены с третьим выходом дешифратора знаков, первый и второй входы которого соединены с прямыми выходами соответственно первого и второго триггеров знака, входы первого и второго триггеров знака соединены соответственно с информационными входами первого и второго счеягчиков, которые являются соответcTi HHo первым и вторым информационными входами устройства. Дешифратор знаков ссадержит элемен ты И и НЕ, причем первый вход дешифратора соединен с входами первого элемента НЕ и первым входом первого элемента И, выход первого элемента НЕ соединен с первым входом второго элемента И, второй вход которого соединен с выходом второго элемента НЕ вход которого соединен со вторым входом дешифратора и вторым входом первого элемента И, выход второго . элемента И соединен со входом третьего элемента НЕ и является первым выходом дешифратора знаков, выход первого элемента И соединен со входом четвертого элемента НЕ и является вторым выходом дешифратора знаков, выходы третьего и четвертого элементов НЕ соединены соответственно с первым, и вторым входами третьего элемента И, выход которого является третьим выходом дешифратора знаков. На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема дешифратуэра комбинаций знаков. Устройство для сравнения, чисел содержит генератор импульсов 1, счетчики 2 и 3, триггеры 4 и 5, два дешифратора нуля 6 и 7, элементы НЕ 8 и 9, дешифратор знаков 10, элементы И 11-18 и элементы ИЛИ 19-21. Дешифратор комбинаций знаков содержит элементы И 22-24 и элементы НЕ 25-28. Предлагаемое устройство р ботает следующим образом. Предварительно устройство устанавливается в исходное состояние, при этом счетные регистры 2 и 3, а также триггеры знаков 4 и 5 обнуляются. В исходном сортоянии На выходе дешифраторов нуля 6 и 7 устанавливаются разрешающий сигнал, а на выходе элементов НЕ 8 и 9 - запрещающий. С выходов элементов НЕ запрещающие сигналы поступают на входы элемента И 11, который блокирует прохождение импульсов с выхода генератора 1 на счетные входы счетных регистров 2 и 3. .Далее сравниваемые числа,представЯенные в прямом коде со знаком, вводятся в устройство, при этом модуль числа А записывается в счетный регистр 2, знак его - в триггер 4, модуль числа В записывается в счетный регистр 3, а знак числа В - в триггер 5. После ввода сравнивае1«лх чисел начинается сравнивание чисел (если модули обоих сравниваемых чисел не равны нулю). Если оба сравниваемых числа А и В отрицательны (оба триггера 4 и 5 при записи знаков устанавливаются в единичное состояние), причем при алгебраическом сравнении отрицательных чисел в случае неравенства модулей число с меньшим модулем принимается большим, в случае же равенства . модулей числа принимаются равными, после ввода сравниваемлх чисел в устройство на втором выходе дешифратора комбинаций знаков 10 восстанавливается разрешающий сигнал, на остальных выходах - запрещаквдий. Разрешающий сигнал со второго выхода дешифратора комбинаций знаков поступает на

входы элементов И 13 и 15. На другие входы элемента И 13 поступает разрешающий сигнал с выхода элемента НЕ 9 и запрещающий сигнал с выхода дешифратора нуля 6. На другие входа элемента И 16 поступают разрешающий сигнал с выхода элемента НЕ 8 и запрещающий сигнал с выхода дешифратора нуля 7.

Если модули обоих сравнительных чисел не равны нулю, разрешающими сигнёшами напряжения, снимаемлми с выходов элементов НЕ 8 и 9, элемент И 11 отпирается. При этом импульсы с выхода генератора 1 проходят на счетные входы счетных регистров 2 и 3, синхронно уменьшая их содержимое.

Если первым обнуляется счетный регистр 2, то на выходе дешифратора нуля 6 устанавливается разрешающий сигнал, а на выходе элемента НЕ 8 запрещающий,который блокирует элемент И 11. Разрешающий сигнал с выхода дешифратора нуля 6 поступает на вход элемента И 13, на выходе которого также устанавливается разрешающий сигнал, поступающий через элемент ИЛИ 20 на выход устройства, соответствующий признаку А больше В ва других выхода устройства не возбуждаются).

Когда первым обнуляется счетный регистр 3, то аналогично по мере его обнуления срабатывает элемент И- 15, и высокий сигнал с его выхода через элемент ИЛИ 21 проходит на выход устройства, соответствующий признаку А меньше В (два других выхода устройства не возбуждаются).

Если счетные регистры 2 и 3 обнуляются одновременно, то запрещающими сигналами с выходов элементов НЕ 8 и 9 оба элемента И 13 и 15 блокируются. При этом разрешакяцке сигналы с выходов дешифраторов нуля 6 и 7 поступают на входы элемента И 12, на третий вход которого поступает также разрешающий сигнал со второго выхода дешифратора комбинаций знаков 10 через элемент ИЛИ 19. Вследствие этотр на выходе устройства, соответствующем признаку А равно В, устанавливается разрешающий сигнал (два других выхода устройства не возбуждаются) .

Когда оба сравниваемых числа А и В положительны,(триггера 4 и 5 при записи знаков сохраняют исходное нулевое состояние), причем при сравнении положительных чисел в случае не равенства модулей число с большим модулем принимается большим, в случае же равенства модулей числа принимаются равными, после ввода сравнивае1иых чисел в устройство на первом выходе дешифратора комбинаций знаков 10 устанавливается разрешакяций сигнал, на остальных выходах - запрещающий. Разрешающий сигнал с первого выхода дешифратора комбинаций знаков поступает на входы эле 1ентов И 14 и 16. На другие входы элемента И 14 поступают разрешающий сигнал с выхода элемента НЕ 9 и запрещающий сигнал с выхода дешифратора нуля 6. На другие входы элемента И 16 поступают разрешающий сигнал с выхода элемента НЕ 8 и запрещающий сигнал с вы0хода дешифратора нуля 7.

Если модули обоих сравниваемых чисел не равны нулю, разрешающими сигналами, снимаегФ1Ми с выходов элементов НЕ 8 и 9, элемент И 11 отпирается. При этом импульсы с вы5хода генератора 1 проходят на счетные входы счетных регистров 2 и 3, синхронно уменьшая их содержимое.

Когда первым обнуляется счетный регистр 2, на выходе дешифратора

0 нуля 6 устанавливается разрешающий сигнал, а на выходе элемента НЕ 8 запрещающий, который блокирует элемент И 11. Разрешаннций сигнал «с выхода дешифратора нуля 6 поступает

5 на вход элемента И 14, на выходе которого также устанавливается разрешающий сигнал, поступающий через элемент ИЛИ 21 на выход устройства, соответствующий признаку А меньше

0 В (два других выхода устройства не возбуждаются).

В случае, если первым обнуляется счетный регистр 3, то аналогично по мере его обнуления срабатывает эле-)

5 мент И 16, и разрешающий сигнал с его выхода через элемент ИЛИ 20 проходит на выход устройства, соответствукаций признаку А больше В (два других выхода устройства не воз0буждаются) .

В случае равенства, если счетные регистра 2 и 3 обнуляются одновременно, то запрещающими сигнашами с выходов элементов НЕ 8 и 9 оба элемента И 14 и 16 блокируются. При этом

5 разрешающие сигналы с выходов дешифраторов нуля 6 и 7 поступают на входы элемента И 12, на третий вход которого поступает также разрешающий сигнал с первого выхода дешифратора

0 комбинаций знаков 10 через элемент ИЛИ 19. Вследствие этого на выходе устрЬйства, соответствуннцем признаку А равно В, устанавливается разрешающий сигнал (два других выхода

5 устройства не возбуждаются).

Когда сравниваемые числа А и В имеют разные знаки (при сравнении чисел с разными знаками положительное число принимается большим), после

о ввода срсшниваемых чисел в устройство на третьем выходе дешифратора комбинаций знаков 10 устанавливается разрешающий Сигнал, на остальных входах запрещающий. Разрешающий сигнал с

5 .третьего выхода дихшфратора комбинаций знаков поступает на входы элементов И 17 и 18. На другие входы эл ментов И 17 и 18 поступгиот сигналы с инверсных выходов соответственно пер вого и второго триггеров знаков 4 и 5. Если число А положительно (триггер 4 в нулевом состоянии, а триггер 5 в единичном), срабатывает элемент И 17, с выхода которого разрешающий сигнал через элемент ИЛИ 20 поступает на выход устройства, соответствующий признаку А больше В (два. других выхода устройства не воз буждаются) . Если же положительно число В (три гер 4 в единичном состоянии, а триггер 5 в нулевом), то срабатывает уже элемент И 18, с выхода которого разрешающий сигнал через элемент ИЛИ 21 поступает на выход устройства, соответствующий признаку А меньше В Сдва других выхода устройства не воз буждаются) . При сравнении чисел с разными зна ками резул ьтат сравнения формируется на выходе устройства сразу же после ввода в него сравниваег«их чисел. При сравнении чисел с нулевыми модулями, но с разными знаками, формируется один из признаков неравенства (хотя отрицательный-ноль при кодировании обычно не практикуется и считывается недопустимым). С целью синзфонизации работы пред лагаемого устройства и других сопрягаемых с ним узлов целесообразно предусмотреть дополнительный вход пуска устройства, подключенный к элементу И 11. Кроме того, результаты сравнения должны сниматься после обнуления одного из счетных регистро 2 или 3, время на которое может быть принято равным времени прохождения числа импульсов, равного максимально возможному модулю, которым придется оперировать. Дешифратор комбинаций знаков 10 функционирует следующим образом. Если знаки обоих сравниваемых чисел положительны, на обоих его вхо дах уотанавливается запрещающий сигнал . Указанные уровни инвертируются на элементах НЕ 25 к 26 и через элемент И 22 поступают на первый выход деши/фратора (два других выхода не возбуждаются). Тштда знаки обоих сравниваемых чисел отрицательны, на обоих входах дешифратора устанавливается разрешающий сигнал, при этом срабатывает элемент И 23, с выхода которого разретагиощий сигнал поступает на второй выход дешифратора (два других выхода не возбуждаются). Если знаки сравниваемых чисел не созвпадают, на выходах элементов И 22 и 23 устанавливаются эапрещакяцие сиг ;напы, которые инвертируются на элементах НЕ 27 и 28 и поступают на входы элемента И 24, на выходе которого, являющемся третьим выходом дешифратора, устанавливается разрешающий сигнал. По сравнению .с известными устрой-, ствами аналогичного назначения, строящимися на базе счетных регистров, предлагаемое выгодно расширяет функциональные возможности за счет реализации сравнения чисел с учетом их знаков. Формула изобретения 1. Устройство для сравнения чисел, содержащее генератор импульсов, два счетчика, два элемента И, два дешифратора нуля, два элемента НЕ, причем выход генератора импульсов соединен с первым входом первого элемента И, выход которого соединен со счетными входами первого и второго счетчиков, выходы первого и второго счетчиков соединены со входами соответственно первого и второго дешифраторов нуля, выходы которых соединены соответственно со входами первого и BToporoi элементов НЕ и с первым и вторым входами второго элемента И, выход которого является первым выходом устройства, выходы первого и второго элементов НЕ подключены соответственно к второму и третьему входу первого элемента И, о т л и чающееся тем, что, с целью расширения функциональ:ных возможностей путем учета знаков сравниваемых чисел, оно дополнительно содержит два триггера знаков сравниваемых чисел, дешифратор знаков, шесть элементов И, три элемента ИЛИ, причем выходы первого дешифратора нуля соединены с первыми входами третьего и четвертого элементов И, а выход второго дешифратора нуля - с первыми входами пятого и шестого элементов И, выходы первого элемента НЕ соединены со вторыми входами пятого и шестого, а В;ыход второго элемента НЕ - со BTO-J рыми входами третьего и четвертого элементов И, первый выход дешифратора знаков соединен с третьими выходами четвертого и шестого элементов И и первым входом первого элемента ИЛИ, а второй выход - с третьими входами третьего и пятого элементов И и вторым входом первого элемента ИЛИ, выход которого соединен с третьим входом второго элемента И, выходы третьего и четвертого элементов И соединены соответственно с первыми входами второго и третьего элементов ИЛИ, вторые входы второго и третьего элементов ИЛИ соединены соответственно .с выходами шестого и пятого элементов

И, выходы второго и третьего элементов ИЛИ являются соответственно вторым и третьим выходами устройства, третьи входы второго и третьего элементов ИЛИ соединены с выходгиии соответственно седьмого и восьмого элементов И, пер- 5 вые входы которых соединены с инверсными выходами соответственно первого и второго,триггеров знака, вторые входы седьмого и восьмого элементов И соединены с третьим выходом дешифратора 10 знаков, первый и второй входы которого соединею с прямыми выходами соответственно первого и второго триггеров знакоз, входа первого и второго триггеров знака соединены соответственно с инфор- : мациониыми входами первого и второго , счетчиков, которые являются собтветственно первым и вторым информациойными эходами устройства.I

I 2.Устройство по п.1/0 т л и ч а ю- 20 щ -е е с я тем, что дешифратор знаков содержит элементы и и НЕ, причем первый вход дешифратора соединен с входами первого элемента НЕ и первым входом первого элемента И, выход перйого элемента НЕ соединен с первым входом второго элемента И, эторой вход которого соединен с выходом второго элемента НЕ, вход которого соединен со вторым входом деши(1 атора и вторым вхоДсм первого элемента И, выход второго элемента И соединен со входом третьего элемента НЕ и является первым выходом дешифратора знаков, аыход первого эле мента И соединен со входом четвертого элемента НЕ и является вторьм выходом дешифратора знаков, выходы третьего и четвертого элементов НЕ соединены соответственно с первым и вторым входами третьего элемента И, выход которого является третьим выходом дешифратора знаков.

Источники информгщии, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 541166, кл.С 06 F 7/04, 1976.

2.Авторское-свидетельство СССР 167371, кл.С 06 F 7/02, 1965 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1977 |

|

SU682894A1 |

| Устройство для сложения | 1977 |

|

SU679978A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Устройство для индикации | 1982 |

|

SU1057982A1 |

| Устройство для сложения | 1980 |

|

SU920709A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU991430A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

| Устройство для вычитания | 1985 |

|

SU1309018A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

{7

И

р

и

У

а

и

Фиг.г

Авторы

Даты

1982-09-15—Публикация

1981-01-14—Подача