ключены шины деления и умножеиия, а к второму входу первого элемента И подключена шина алгебраического сложения. Третий вход первого элемента И соединен с выходом первого элемента ИЛИ, а выход - с первыми входами четвертого, пятого, шестого и седьмого элементов И. Выход счетчика второго операнда подключен к входу дешифратора нуля второго операнда, первый вход восьмого элемента И соединен с выходом дешифратора нуля первого опер-анда, выход .восьмого элемента И - с входом счетчика первого операнда, выход дешифратора нуля первого операнда - с первым входом первого элемента ИЛИ, с третьим входом третьего элемента И, с входом первого элемента НЕ, с первы-м входом девятого элемента И. Выход дешифратора нуля второго операнда связан с первым входом десятого элемента И, с входом второго элемента НЕ, с вторым входом первого элемента ИЛИ, с третьим входом второго элемента И и с четвертым входом третьего элемента И. Выход триггера знака первого операнда соединен с первым входом элемента неравнозначности и с вторым входом девятого элемента И, выход триггера знака второго операнда - с вторым входом элемента неравнозначности и с вторым входом десятого элемента И, выход элемента неравнозначности - с входом третьего элемента НЕ, с вторым входом шестого элемента И и с вторым -входом четвертого элемента И, выход которого подключен к nepiBOMy входу второго элемента ИЛИ. Выход, первого элемента НЕ соединен с первым входом одиннадцатого элемента И, с первым входом третьего элемента ИЛИ, с третьим входом десятого элемента И, с первым входом двенадцатого элемента И и с третьим входом шестого элемента И, подключенного своим выходом к первому входу четвертого элемента ИЛИ. Выход второго элемента НЕ соединен с третьим входом девятого элемента И и с вторым входом третьего элемента ИЛИ, подключенного выходом к второму входу пятого элемента И. Выход третьего элемента НЕ подключен к третьим входам пятого и седьмого элементов И, а также к первым входам тринадцатого и четырнадцатого элементов И. Выход второго элемента И соединен с первым входом пятого элемента ИЛИ и с вторым входом четвертого элемента ИЛИ, третий и четвертый входы которого подключены :к выходам седьмого и двенадцатого элементов И соответственно. Выход первого элемента И соединен с вторым входом пятого элемента ИЛИ, подключенного своим выходом к второму входу восьмого элемента И, выход третьего элемента И - с третьим входом пятого элемента ИЛИ и с вторым входом второго элемента ИЛИ, третий и четвертый входы которого подключены к выходам пятого и одиннадцатого элементов И соответственно, и выход -к входу счетчика результата. Выходы девятого, десятого, тринадцатого .и четырнадцатого элементов И соединены с входами

шестого элемента ИЛИ, выход которого подключен к входу триггера знака результата. Выход четвертого элемента ИЛИ соединен с входом счетчика второго операнда, шина алгебраического сложения - с чет1верть ми входами девятого и десятого элементов И, шина умножения - с вторыми входами двенадцатого и четырнадцатого элементов И, а шина деления - с вторыми входами одиннадцатого и тринадцатого элементов И.

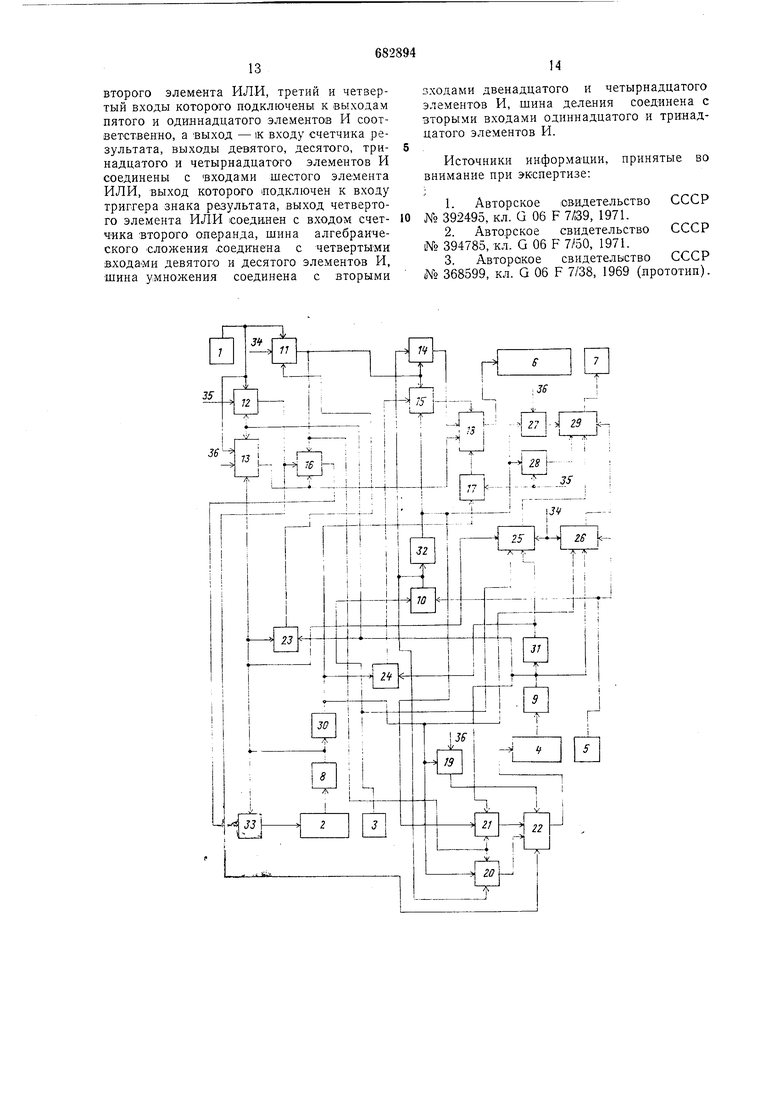

На чертеже представлена структурная схема арифметического устройства.

Устройство содержит в своем составе

генератор / имлульсов, вычитающий счетчик 2 первого операнда, триггер 3 знака первого операнда, вычитающий счетчик 4 второго операнда, триггер 5 знака второго операнда, суммируюший счетчик 6 результата и триггер 7 знака результата. В состав устройства входят также дешифраторы 8 и 9 нуля первого и второго операндов соответственно, элемент 10 неравнозначности, элементы И //, 12 и 13, предназначенные

для блокировки генератора / импульсов по окончании операдии соответственно при алгебраическом сложении, делении и умножении, элементы И /4 и 15, обеспечиваюшие при алгебраическом сложении поступление

импульсов счета на вход счетчика 6 соответственно при совпадении и несовпадении знаков операндов, элемент ИЛИ 16, через который проходят Импульсы счета на вход счетчика 2, элемент И 17, обеспечиваюший

формирование модуля частного при делении, элемент ИЛИ 18, через который импульсы счета поступают на вход счетчика

6,элемент И 19, с помощью которого вычитается единица информации из модуля сомножителя, помещенного в счетчик 4 при умножении, элементы И 20 к 21, обеспечивающие при алгебраическом сложении поступление импульсов счета на вход счетчика 4 соответственно при совпадении и несовпадении знаков слагаемых, элемент ИЛИ 22, через который импульсы счета поступают на счетный вход счетчика 4, элементы ИЛИ 23 и 24, управляющие счетом при алгебраическом сложении, элеме11ты И

25-28, предназначенные для формирования знака результата, элемент ИЛИ 29, транслирующий знак результата в триггер

7,элементы НЕ 30, 31 и 32, элемент И 33, блокирующий счетный Вход счетчика 2. К

входам устройства подключены шина 34 алгебраического слолсения, шина 35 деления и шина 36 умножения.

Рассмотрим работу устройства при выполнении алгебраического сложения, умножения и деления.

Реализация операции алгебраического сложения.

Сначала рассмотрим случай, т-согда знаки слагаемых не совладают. При этом необходимо принять во внимание, что при алгебраическом сложении двух чисел с разными знаками модуль суммы равен разности модулей слагаемых, а знак суммы совпадает со знаком слагаемого с большим модулем. Данное положение реализуется в описываемом арифметичеоком устройстве следующим образом.

Пусть iB счетчики 2 и 4 записаны в прямом коде слагаемые с несовпадающими знаками, а счетчик 6 при веден в нулевое состояние. Тогда на выходах деш ифраторов 8 к 9 образуется разреш ающий уровень напряжения, а на выходе элемента 10 неравнозначности - за прещаю1дий уровень. Разрешающий уровень с выхода дешифратора 8 подается на элементы И 55 и 25, а также н-а элемент ИЛИ 23 vi на вход элемента НЕ 30. Разрешающий уровень с выхода дешифратора 9 подается на элементы И 2У и 26, а также на элемент ИЛИ 23 и на вход элемента НЕ 31. Запрещающий уровень с выхода элемента 10 неравнозначности подается на элементы И 74 и 20, а также на вход элемента НЕ 52. При этом на выходе элемента ИЛИ 24 (благодаря элементам НЕ 30 vi 31) образуется запрещающий уровень, который подается на вход элемента И 15, на другой вход которого с выхода элемента НЕ 52 попадает разрешающий уровень. С выхода элемента НЕ 52 разрешающий уровень поступает также на вход элемента И 21. Запрещающий уровень с выхода элемента НЕ 30 подается та,кже на элементы И 20 и 26, а запрещающий уровень с выхода элемента НЕ 31 - также на элемент И 25. На входы элементов И 25 и 26 поданы уровни надряжений с единичных выходов триггеров 5 и 5 соответственно.

Разрешающий уровень, снимаемый с выхода элемента ИЛИ 23, подается на вход элемента И 11, который -при возбуждении щины 34 алгебраического сложения отпирается, обеспечивая поступление импульсов счета на входы элементов И 14 и .15, запертых уровнями напряжений, снимаемых с ;выходов элемента 10 неравнозначности и элемента ИЛИ 24 соответственно. Импульсы счета поступают также на запертый элемент И 20 и на открытый элемент И 2/ и, кроме того, через элемент ИЛИ /б на открытый элемент И 35. С выхода опкрытого элемента И 55 импульсы счета поступают на счетный вход счетчика 2, а с выхода открытого элемента И 21 через элемент ИЛИ 22 - на счетный вход счетчика 4. Тем самым обеспечивается синхронное вычитание «единиц с модулей обоих слагаемых.

Как только счетч,ик одного из слагаемых обнулится (в этот момент в счетчике другого слагаемого будет сформирована разность модулей слагаемых), счетный вход его запрещающим уровнем, снимаемым с выхода соответствующего дешифратора нуля, блокируется, на выходе одного из элементов НЕ 30 и 31 образуется разрешающий уровень, который через элемент ИЛИ 24 транслируется на вход элемента И 15. Последний отпирается, и импульсы счета через элемент ИЛИ 18 начинают поступать на счетный вход счетчика 6 до тех пор, пока не обнулится счетчик также и другого слагаемого. Тогда на обоих входах элемента ИЛИ 25 уровни напряжений становятся запрещающими, на его выходе также устанавливается залрещаюЩНЙ уровень напряжения, вследствие чего элемент И 11 останавливает счет. В счетчике 6 разность модулей слагаемых.

Знак алгебраической суммы формируется следующим образом.

Пусть при счете первым обнуляется счегчик 2, тогда на выходе дешифратора 8 уровень нап.ряжения становится запрещающим, а на выходе элемента НЕ 30 разрешающим. Этот уровень подается на вход элемента И 26, на одном из входов которого уже имеется разрещающий уровень с выхода дешифратора 9 (так как счетчик 4 пока не обнулен). На вход элемента И 26 подведена возбужденная в рассматриваемый момент щина 34 алгебраического сложения, а также единичный выход триггера 5. Если триггер 5 находится в нулевом состоянии (слагаемое с большим модулем положительное) элемент И 26 не срабатывает и триггер 7 не изменяет своего исходного (нулевого) состояния, чем обеспечивается соответствие знака алгебраической суммы знаку слагаемого с большим модулем. Если же триггер 5 установлен в единичное состояние (слагаемое с большим модулем отрицательное), элемент И 26 через элемент ИЛИ 29 транслирует высокий уровень с единичного выхода этого триггера на вход триггера 7, который благодаря этому тоже перебрасывается в единичное состояние, и знак алгебраической суммы получается отрицательным. При последующем же обнулении счетчика 4 знак обнулившегося ранее слагаемого (т. е. информация, записанная в триггере 5) не переписывается в триггер 7, TaiK ка;К элемент И 25 по обнзлении счетчика 2 блокируется запрещающим уровнем напряжения, снимаемым с выхода дещифратора 8.

В случае же более раннего обнуления счетчика 4 разрешающий уровень напряжения, снимаемый с выхода элемента НЕ 3 через элементы И 25 и ИЛИ 29, переписывает информацию относительно знака слагаемого, записанного в триггер 7, чем опятьтаки обеспечивается соответствие знака алгебраической суммы з11аку слагаемого с

большим модулем. За1Прещающий уровень с .выхода дешифратора 9 (подаваемый на элемент И 26), блокирует при этом поступление информации относительно знака слагаемого с меньшим модулем в триггер 7.

Рассмотрим случай, когда знаки слагаемых совпадают. При этом следует отметить, ЧТО . в случае алгебраического сложения двух.чнсел с одинаковыми знаками модуль сум.мы равняется сумме модулей слагаемых,, а знак совпадает со знаками слагаемых. Данное положение в устройстве реализуе. посредством последовательного перевода сначала модуля, записанного -. счетчЕке 2, затем модзля, записанного в счетчике 4, в счетчик 6. ФорМираваяие знака суммы осуществляется при этом так же, KaiK ив случае несовпадения знаков слагаемых. Естественно, что в этом случае в силу последовательности в обнулении счетчикоз 2, и 4, знак алгебраической суммы совпадает со знаком слагаемого, записанного в триггере 3 слагаемого, записанного в триггер 5.

При записи чисел с совпадающими знаками соответственно в счетчики 2 н 4 уров«и нацряжений на выходах элементов уст;ройства устанавливаются такими .же, как J-I При описанном случае несовладения знаков слагаемых, за исключением уровней напря/кений на выходе элемента W неравнозначности и, как следствие, на выходе эле.мента НЕ 32, которые меняются на противоположные. В силу этого на все время счета элементы И 15 и 21 блокируются. Элемент И 14 отпирается, а элемент И 20 подготавливается к отпиранию по обнулении счетчика. Разрешающий уровень напряжения с выхода элемента ИЛИ 23 при возбуждении шины 34 алгебраического еложения отпирает элемент И 11, и импульсы счета поступают через отпертый элемент И 14 к элемент ИЛИ 18 на счетный вход счетчика 6 и через элемент ИЛИ 16 на счетный вход счетчика 2. По обнулении счетчика 2 в счетчике 6 получается модуль первого слагаемого. При этом высоким уровнем напряжения, снимаемым с выхода элемента НЕ 30, отпирается элемент И 20 и начинается сложение содерл имого счет iикa 4 (модуля второго слагаемого) с уже введенны.м в счетчик 6 модзлем первого слагаемого. Когда обнуляется и счетчик 4, на выходе элемента ИЛИ 23 з станавливается запрещающий уровень напряжения, который будучи поданным на вход элемента И // останавливает счет.

Итак, записав предварительно в счетчики 2 И 4 прямые коды слагаемых, при любой возможной комбинации модулей и знаков (Последних имеется возможность, возбудив шину 34 алгебраического сложения, получить прямой КОД алгебраической сум.мы с соот1вет1ствующим знаком.

Реализация операции умножения.

Операщия умножения в предлагаемом арифметическом устройстве реализованае соответствии с равенством

А . В В + В + . . + В,

А слагаемых,

следуя которому модуль произведения можно получ1ить, сложив 1одуль одного Hs со.множителей с самим собой столько раз, сколько содержится единиц в модуле другого сомножителя. При этОМ произведению приписывается положительный знак при совпадении знаков сомножителей и отрицательный - в противном случае.

Отмеченные положения реализуются в описываемом арифметическом устройстве следующим образом.

После записи в прямом коде сомнол-;ителей соответственно в счетчике 2 и 4 на выходах дещифраторов 8 к 9 устанавливается разрешающий уровень напряжения (если только модули сомно.жителей не равны нулю). Разрещающий уровень напряжения с выхода дешиф.ратора подается на в.ход элементов И ,1.3, 33, а также на вход элемента НЕ 30, с выхода которого запрещающий уровень напряжения проходит на вход элемента И 13. Разрешающий уровень напряжения с выхода дешифратора 9 поступает на другой ВХОД эле.мента И 13. При возбуждении шины 36 умножения импульсы счета с выхода генератора / через отпертый элемент И 13 подаются на входы элементов ИЛИ 16 и 18. С выхода элемента ИЛИ 16 через отпертый элемент И 33 импульсы счета поступают на счетный вход вычитающего счетчика 2, а с выхода элемента ИЛР1 18 импульсы счета попадают на счетный вход суммирующего счетчика 6. Тем самым обеспечивается перевод модуля сомножителя, записанного в счетч.ик 2, в счетчик 6. Как только счетчик 2 обнуляется, В нем до поступления очередного и.мпульса счета восстанавливается прямой код, соответствующий величине модуля, записанного iB счетчик 2. Процесс обнуления счетчнка 2 с последующим восстановлением в нем кода модуля соответствующего со.множителя .вызывает повеление на выходе элемента НЕ 30 положительного импульса напряжения, который через отпертый элемент И 19 (шина 36 умножения возбуждена) и через элемент ИЛИ 22 поступает на счетный вход вычитающего счетчика 4 и уменьшает содержимое последнего на единицу. Тажим образом, после каждого обнуления - восстановления счетчика 2 содержимое счетчика 6 увеличивается на величину, равную величине модуля сомнол ителя, записанного в счетчик 2, а содержимое счетчика 4 уменьшается на единицу. Счет продолжается до тех пор, пока не обнулится счетчик 4. Как только счетчик 4 обнуляется, на выходе дешифратора 9 образуется

запрещающий уровень валряжения, который будучи поданным на вход элемента И 13 перекрывает поступление импульсов счета в устройство. В счетчике 6 получается модуль произведения чисел, записанных в счетчике 2 и 4.

Бели какой-либо из сомножителей равен нулю, на выходе соответствующего из дешифраторов (8 или 5) образуется запрещающий уровень напряжения, который будучи поданным на вход элемента И 13 перекрывает поступление импульсов счета в устройство, счетчик 6 остается -в исходном (нулевом) состоянии, чем и обеспечивается равенство пулю модуля произведения.

Знак произведения формируется посредством элемента 10 ыера1Внозначности, элемента НЕ 32, элемента И 27 и элемента ИЛИ 29. При совпадении знаков у сомножителей на выходе элемента НЕ 32 получается запрещающий уровень, вследствие чего на выходе элемента И 27 также наблюдается запрещающий уровень и триггер 7 свое исходное пулевое состояние ле меняет, тем самым произведению приписывается положительный знаж. При несовпадении знаков у сомножителей на выходе элемента НЕ 32 получается разрешающий уровень напряжения, который через отпертый элемент И 27 (шина 36 умножения, подключенная к второму входу элемента И 27, возбуждена) и через элемент ИЛИ 29 поступает на вход триггера 7 и перебрасывает его в единичное состояние, тем произведению приписывается отрицательный знак.Итак, записав предварительно в счетчики 2 и соответственно прямые коды сомножителей с любыми знаками, имеется возможность, Возбудив шину 36 умножения и восстанавливая .в нроцессе счета в счетчике 2 (по мере его обнуления) .код, соответствующий модулю сомножителя, записанного в этот счетчик, получить прямой код произведения с соответствующим знаком.

Реализация опера-ции деления.

В предлагаемом арифметическом устройстве олераци1Я деления реализуется в соответствии со следующим очевидным положением:

А:В N, то 1МОЖНО утверждать, что выражение

- В-... - В

N вычитаний

равно нулю с избытком. При этом, если А кратно В, имеет место строгое равенство.

Из сказанного следует, что модуль частного двух чисел с соответствующей точностью можно получить, определив сколько раз .модуль делителя можно вычесть из модуля делимого. При этом частному приписывается (как и при умножении, положительный знаж при совпадении знаков операндав и отрицательный в противном случае).

Отмеченное в описываемом ариф.метическом устройстве реализуется следующим образом.

Делимое ;в прямом коде записывается в счетчики 4, делитель - в счетчики 2, счетчик ,6 приводится в исходное (нулевое) состояние. При этом резрешающий уровень напряжения с выхода дещифратора 8 подается на выходы элемента НЕ 30 и элемента И 33, отпира.:Я последний, а разрешаюший

уровень напряжения с выхода дещифратора 9 (если только делимое не равно нулю) проходит на вход элемента И 12, Запрещающий уровень напрялчения с выхода элемента НЕ 30 поступает на вход элемента

И /7. При возб; ждении шины 35 деления импульсы счета с выхода генератора / через открытый элемент И 12 подаются на входы элементов ИЛИ 16 и 2{2. С выхода элемента ИЛИ ,16 через отпертый элемент

И 33 импульсы счета поступают на счетный вход вычитающего счетчика 2, а с выхода элемента ИЛИ 22 - на счетный вход вычитающего счетчика 4. Тем самым обеспечивается синхронное вычитание единиц с модулей и делимого, и делителя. Как только счетчик 2 обнуляется, в нем до поступления очередного импульса счета восстанавливается прямой код, соответствующий величине модуля делителя.

Процесс обнуления счетчика 2 с последующим восстановлением в .нем прямого кода, соответствующего величине модуля делителя, сопровождается появлением на выходе элемента НЕ 30 положительного

импульса напряжения, который через отпертый элемент И /7 (шина деления возбуждена) и через элемент ИЛИ 18 поступает на счетный вход суммирующего счетчика 6 и увеличивает содержимое последнего (равное первоначально нулю) на единицу. Таким образом, после каждого обнуления-(восстановления счетчика 2 содержимое счетчика 4 уменьшается ,на величину модуля делителя, а содержимое счетчика 6 увеличивается на единицу. Счет продоллчается до тех пор, пока не обнулится счетчик 4. Как только счетчик 4 обнуляется, на выходе дешифратора 9 образуется запрещающий уровень напряжения, который будучи

поданным на вход элемента И 12 перекрывает поступление импульсов счета в устройство. В счетчике 6 получается модуль частного.

Если делимое, записываемое в счетчике 4 равно нулю, то на выходе дешифратора 9 образуется запрешающий уровень напряжения, который будучи поданным на вход элемента И 12 перекрывает поступление импульсов счета в устройство, тем временем счетчик 6 остается в исходном (нуле11

BOM) состоянии, чем и обеопечивается равенство нулю модуля частного.

Знак частного лри делении формируется аналогично тому, как это делается при умножении, только «место элемента И 27 при этом пр,ИНИмает участие элемент И 28.

Таким образом, залисав делимое и делитель с любыми знаками в прямом коде соответственно в счетчике 2 и -возбудив шину 35 деления, имеется возможность, восста«авливая в .процессе ючета в счетчике 2 (по мере его обнуления) код, соответствующий модулю делителя, .получить прямой (приближенный) код частного с соответствующим знакам.

Точность вычислений при выполнении олерации деления может быть увеличена. Для этого нео.бходи1мо помещать модуль делимого ,в счетчик 4 не ю первого разряда счетчика, а с некоторого г-го разряда. Тогда последние г-1 разрядов модуля частного, получаемого в счетчике 6, с соответствующей точностью представляют дробную часть частного.

По сравнению с .прототипом в рассмотренном арифметическом устройстве иопользуется одним счетным .регистром меньше, благодаря чему обеопечивается выигрыщ в обо,рудова.нии. Кроме того, в нем, в отличие от .прототипа, .как операнды, так и результат 01пера)ции участвуют только IB прямом коде, что избавляет от необходимости преобразования кодов операндов.

Преимущество описаиного устройства по сравнению с традиционным арифметическим устройством, .построенным на трех регистрах (один из которых накапливающий), заключается .в существенном уменьшении используемого на один разряд вычислений оборудования. Это достигается за счет исключения цепей сдвигав и уменьшения объемов оборудования в щепях переносов. Кроме того оно, в отличие от традиционного арифметического устройства, не требует предварительного преобразования кодов операндов.

Формула изобретения

Арифметическое устройство, .содержащее генератор импульсов, элементы И, счетчик результата, счетчик первого и .второго операндов, дешифратор нуля .первого операнда, причем выход генератора импульсов подключен к первому входу первого элемента И, выход счетчика пер.вого операнда соединен с входом дешифратора нуля первого операнда, отличающееся тем, что, с целью уменьшения объема используемо.го оборудования, устройство допол.нительно содержит элементы ИЛИ, НЕ, элемент .неравнозначности, триггеры знакав операндов и результата, дешифратор нуля второго операнда, причем выход генератора импульсав соединен с первыми вхо12

дами второго и третьего элементов И, к вторым входа1М которых подключены соответственно шины деления и умножения, к вто.рому входу первого элемента И подключе.на шина алгебраического сложения, третий вход первого элемента И соединен с выходом первого элемента ИЛИ, а выход - с пер.выми входами четвертого, тятого, .шеето и седьмого элементов И, выход счетчика

второго опера.нда соединен с входом дешифратора нуля второго операнда, первый вход восьмого элемента И соединен с выходом дешифратора нуля первого операнда, (ВЫХОД восьмого элемента И соединен с

входом счетчика первого операнда, выход дешифратора нуля .пер.вого операнда .соединен с первым входом первого элемента ИЛИ, с третьим входом третьего элемента И, с входом первого элемента НЕ и с первым входом девятого элемента И, выход де|щифратора нуля второго операнда .соединен с первым (ВХОДОМ десятого элемента И, с входом второго элемента НЕ, с вторым входом первого элемента ИЛИ, с третьим

входом второго элемента И и с четвертым входом третьего элемента И, выход тригге,ра знака первого операнда соединен с первым входом элемента .неравнозначности и с вторым входом четвертого элемента И,

ВЫХО.Д триггера знака второго операнда соединен с вторым входом элемента неравнозначности и с вторым входом десятого элемента И, выход элемента неравнозначности соединен с входом третьего эле мента

НЕ, с вторым входом шестого элемента И и с вторым входом четвертого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход первого эле|Мента НЕ соединен с первым входом одиннадцатого элемента И, с первым входом третьего элемента ИЛИ, с третьим входом десятого элемента И, с первым входом двенадцатого элемента И и с третьим входам шестого элемента И, подключенного своим

выходам к первому входу четвертого элемента ИЛИ, выход второго элемента НЕ соединен с третьим входом девятого элемента И и с (вторым входом третьего элемента ИЛИ, подключенного выходом к второму входу Нятого элемента И, выход третьего элемента НЕ подключен к третьим входам пятого и седьмого элементов И, а также к первым входам тринадцатого и четырнадцатого элементов И, выход второго

элемента И соединен с первым входом пятого элемента ИЛИ и с вторым входом четвертого элемента ИЛИ, третий и четвертый входы которого подключены к выходам седьмого и двенадцатого элементов И соотвстственно, выход первого элемента И соединен с вторым входом .пятого элемента ИЛИ, выход которого подключен к второму входу восьмого элемента И, выход третьего элемента И соединен с третьим входом

пятого элемента ИЛИ .и с вторым входом второго элемента ИЛИ, третий и четвертый входы которого подключены к выходам пятого и одиннадцатого элементов И соответственно, а ВЫХОД - 1К входу счетчика результата, выходы девятого, десятого, тринадцатого и четырнадцатого элементов И соединены с входами шестого элемента ИЛИ, выход которого подключен к входу триггера знака результата, выход четвертого элемента ИЛИ соединен с входом счетчика второго операнда, шина алгебраического сложения соединена с четвертыми аходаМи девятого и десятого элементов И, шина умножения соединена с вторыми входами двенадцатого и четырнадцатого элементов И, шина деления соединена с вторыми входами одиннадцатого и тринадцатого элементов И. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 392495, кл. G 06 F 7/39, 1971. 2.Авторское свидетельство СССР № 394785, кл. G 06 F 7/50, 1971. 3.Авторокое свидетельство СССР (No 368599, кл. G 06 F 7/38, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения | 1977 |

|

SU679978A1 |

| Устройство для сложения | 1980 |

|

SU920709A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Устройство для сравнения чисел | 1981 |

|

SU959066A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Реверсивный счетчик | 1977 |

|

SU738179A1 |

| Устройство для сложения | 1981 |

|

SU991415A1 |

| Система для трансляции с проблемноориентированного языка | 1976 |

|

SU674028A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для определения дисперсии | 1978 |

|

SU860080A1 |

Авторы

Даты

1979-08-30—Публикация

1977-04-27—Подача