Изобретение относится к вычислительной технике и может быть использовано в операционных схемах цифровых процессоров.

Известно устройство для последовательного сложения и вычитания чисел, содержащее одноразрядный сумматор-вычитатель, сдвиговые регистры первого и второго слагаемого, блок коррекции, элемент задержки, элемен ты И и ИЛИ, причем первый и второй входы сумматора-вычитателя соединены с выходами младших разрядов сдвиговых регистров соответственно первого и второго слагаемого, а выход сумматора-вычитателя подключен к входу старшего разряда сдвигового регистра первого слагаемого. Сдви.говый регистр второго слагаемого содержит дополнительный разряд, выход которого подключен к входу старшего разряда этого сдвигового регистра, а вход - к выходу блока коррекции, первый, второй и третий входы которого подключены к выходам трех старших разрядов сдвигового регистра первого слагаемого, четвертьш вход - к выходу первого элемента И, первый вход которого через элемент задержки подключен к выходу переноса одноразрядного сумматора-вычитателя, а второй вход - к шине разрешения переноса, пятый вход блока коррекции подключен к первому управляющему входу устройства, выход блока коррекции подключен также к первому входу элемента Щ1И, выход которого соединен с вторым и третьим старшими разрядами Сдвигового регистра второго слагаеМОго, второй вход элемента ИЛИ соединен с выходом второго элемента И, первый вход которого подключен к выходу первого элемента И, а второй вход - к второму управляющем входу устройства DI.

Данное устройство имеет недостаточное быстродействие, обусловленно тем, что получение результата сложения-вычитания выполняется за два цикла, причем за первый цикл вьшолнется сложение-вычитание двоичных чисел, а за второй цикл - коррекция полученного перед этим результата .

Наиболее близким к предлагаемому является устройство для алгебраического сложения чисел, содержащее два сдвиговых регистра, узел суммирования по модулю два и узел записи знака результата, причем входы разрдов первого сдвигового регистра соединены с входами первого операнда устройства, входы разрядов второго сдвигового регистра сординены с входами второго операнда устройства входы управления сдвигом первого и второго сдвиговых регистров, подключены к входу синхронизации устройства, выход первого сдвигового ргистра соединен с первыми входами первого, второго и третьего элементов И, на вторые входы которых поступают управляющие сигналы выдачи знака, прямого и обратного кодов первого операнда соответственно, выход первого элемента И является выходом знака первого операнда выход третьего элемента И через инвертор и выход второго элемента И соединены с входами первого элемента ИЛИ, выход которого соединен с первым входом узла суммирования по модулю два, выход второго сдвигового регистра соединен с первыми входами четвертого и пятого элементов И, на вторые входы которых поступают управляющие сигналы вьщачи знака и прямого кода второго операнда, выход четвертого элемента И является выходом знака второго операнда, а выход пятого элемента И соединен с вторым входом узла суммирования по модулю два, третий вход которого соединен с выходом второго элемента ИЛИ, на первый вход которого поступает сигнал переполнения, а второй вход через линию задержки соединен с -выходом сигнала переполнения узла су 1мирования п модулю два, информационный выход которого соединен с первым входом (Элемента ИЛИ узла записи знака результата, на второй вход которого поступает знак результата, а выход KOToijoro соединен с информаЦИОНН1ЛМ входом первого сдвигового регистра, первый вход шестого элемета И соединен с выходом сигнала переполнения узла сзжмирования по модулю два, на его второй вход поступает управляюшрй сигнал выдачи сигнала переполнения, авыход явялется выходом сигнала переполнения первого разряда результата .,

Недостатком известного устройства является необходимость корректи3

ровки результата при выполнении операции вычитания, что приводит к снижению быстродействия.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что устройство для алгебраического сложения чисел, содержапдее два сдвиговых регистра, узел cy fмиpoвания по модулю два и узел записи знака результата, содержащий элемент ИЛИ, причем входы разрядов первого сдвигового регистра соединены с входами первого операнда устройства, входы разрядов второго сдвигового регистра соединены с входами второго операнда устройства, входы управления сдвигом первого и второго сдвиговьк регистров подключены к входу синхронизахщи устройства, выходы первого и второго сдвиговых регистров подключены к соответствующим входам узла суммирования по модулю два, содержит сумматор, третий сдвиговый регистр,узел суммирования по модулю два содержит три элемента И, два элемента ИЛИ и эле.мент НЕ,а узел записи знака результата дополнительно содержит два элемента И, при этом входы разрядов сумматора подключены к входам первого операнда устройства, первый и второй входы первого элемента И узла суммирования по модулю два соединены соответственно с первым и вторым входами узла суммирования по модулю два, а выход подключен к входу элемента НЕ узла суммирования по модулю два, выход которого подключен к первым входам второго и третьго элементов И узла суммирования по модулю два, вторые входы которых соединены соответственно с первым и вторым входами первого элемента И узла суммирования по модулю два, а выходы подключены к входам первого элемента ИЛИ узла суммирования по модулю два, выход которого подключен к информационному входу третьего сдвигового регистра, входы второго элемента ШШ узла суммирования по модулю два соединены с выхдами первого и третьего элементов И узла суммирования по модулю два, а выход подключен к информационному входу сумматора, выходы знаковых разрядов первого и второго сдвиго-. вых регистров подключены к первым

61484

входам соответствующих элементов И узла записи знака, вторые входы которых соединены с выходами соответственно второго и третьего элементов И узла суммирования по модулю два, входы элемента ИЛИ узла записи знака подключены к выходам первого и второго элементов И узла записи знака, а выход подключен к входу

знакового разряда третьего сдвигового регистра, вход управления сдвигом которого соединен с входом синхронизации устройства, управляющий вход сумматора подключен к входу синхро-

низации устройства.

В известньтх устройствах, вьтолняющих алгебраическое сложение чисел, не используются дополнительный регистр для фиксации разности и узел

0 суммирования по модулю два с соответствующей структурой, которые содержит предлагаемое устройство. Это связано с тем, что в отличие от известных устройств, в которых

5 вычитание исходных величин выполняется на сумматоре, причем одно из слагаемых представляется в обратном коде, в предлагаемом устройстве вы читание вьтолняется одновременно

0 с суммированием с помощью узла суммирования по модулю два при параллельном сдвиге содержимого обоих регистров операндов, а результат фиксируется в регистре разности.

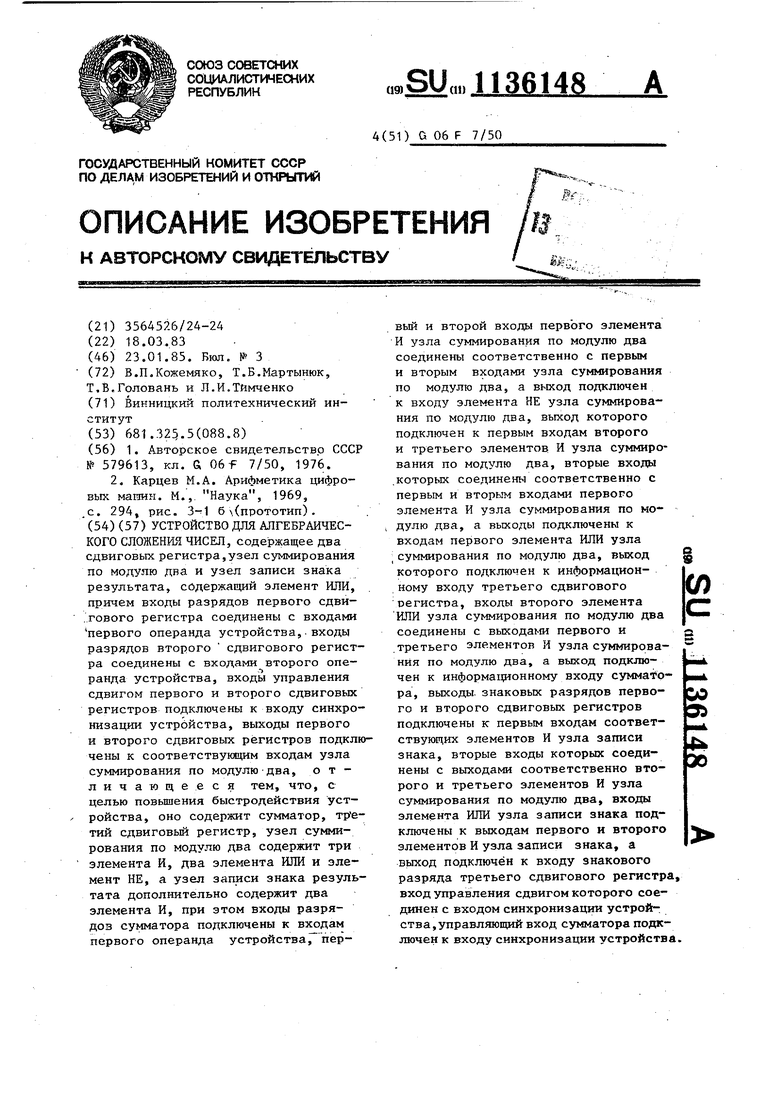

На чертеже представлена структурная схема предлагаемого устройства.

Устройство для алгебраического сложения чисел содержит два сдвиговых регистра 1 и 2 операндов А и В соответственно, сумматор 3, сдвиговый регистр 4 разности операндов, узел 5 суммирования по модулю два и узел 6 записи знака результата. Узел 5 суммирования по модулю два содержит три элемента И 7-9, элемент НЕ 10 и два элемента ИЛИ 11 и 12. Выходы сдвиговых регистров 1 и 2 соединены с входами 13 и 1А узла 5 суммирования по модулю два, выход 15 которого соединен с информационным входом сумматора 3, выход 16 - с информационным входом сдвигового регистра 4, а выходы 17 и 18 с соответствуюпщми входами узла 6. записи знака.

Входы элемента И 7 узла 5 суммирования по модулю два соединены с его входами 13 и 14, а выход - с

S

входом элемента НЕ 10, выход которого соединен с первыми входами элементов И 8 и 9, вторые входы которых подключены к соответствующим входам элемента И 7. Входы элемента ИЛИ 11 узла 5 суммирования по модулю два соединены с выходами элементов И 7 и 9, а его выход является выходом 15 узла 5 суммирования по модулю два. Входы элемента РШИ 12 узла 5 суммирования по модулю два соединены с выходами элементов И 8 и И 9, а выход является выходом 16 узла 5 суммирования по модулю два. Выходы элементов И 8 и 9 являются выходами 17 и 18 узла 5 суммирования по модулю два

Узел 6 записи знака содержит два элемента И 19 и 20 и элемент ИЛИ 21 а его входы 22 и 23 подключены к выходам знаковых разрядов сдвиговых регистров 1 и 2 соответствеино. Входы элемента И 19 узла 6 записи знака соединены с входам 22 узла 6 записи знака и выходом 17 узла 5 суммирования по модулю два, а входы элемента И 20 - с входом 23 узла 6 записи знака и выходом 18 узла 5 суммирования по модулю два. Выходы элементов И .19 и 20 соединены с входами элемента ИЛИ 21, выход которого является вькодом 24 узла 6 записи знака и coeдIiнeн с входом знакового разряда сдвигового регистра 4. Шина 25 является шиной записи первого операнда А и подключена к входам разрядов сдвигового регистра 1 и сумматора 3, шина 26 является шиной записи второго операнда В и подключена к входам разрядов сдвигового регистра 2, управляющая шина 27 соединена с входами управления сдвигом сдвиговых регистров 1 и 2, а управляющая шина 28 соединена с .входами управления сдвигом сумматора 3 и сдвигового регистра 4.

Устройство работает следуюпщм образом.

Во время первого такта работы устройства вьтолняется запись первого операнда А, поступающего по шине 25,в сдвиговый регистр 1 и сумматор 3. За второй такт записывается второй операнд В, поступающий по шине 26, в сдвиговый регистр 2. Запись операндов осуществляется в единичном нормальном коде. Затем вьтолняется обработка узлом

6

5 суммирования по модулю два информации, поступающей на его входы 13 и 14 в результате одновременного сдвига содержимого обоих регистров 1 и 2 до их полного обнуления. Узлом 5 суммирования по модулю два определяется общая часть обоих операндов, которая с еговыхода 15 поступает на информационньй вход сумматора 3, где суммируется с первым операндом, записанным ранее. Таким образом, на сумматоре 3 фиксируется сзпчма двух исходных чисел А и В, если вьтолняется соотношение А В, или удвоенное значение операнда А, если А В.

Разность операндов А и В с выхода 15 узла 5 суммирования по модулю два поступает на информационный вход сумматора 3 для формирования суммы исходных чисел А и В в случае, если А Bj ас выхода 16 узла 5 суммирования по модулю два разность записывается в сдвиговый регистр 4. Единичный сигнал на выходе 17 узла 5 суммирования по модулю два разрешает запись в знаковый разряд сдвигового ре.гистра 4 знака операнда А, поступающего на вход 22 узла 6 записи, знака, для случая, когда А Bj- а единичный сигнал, на выходе 18 узла 5 суммирования по модулю два - запись знака операнда В, поступающего на вход 23 узла 6 записи 5 знака, для случая,- когда А В.

Знак операции учитьшается при записи второго операнда, т.е. в случае операции сложения его знак остается без изменения, в случае операции вычитания - изменяется на

противоположный. Таким образом, в устройстве выполняются операции над операндами, знаки которых не влияют на выбор вьтолняемой операции,

поскольку за один цикл работы устройства формируются одновременно и сумма и разность исходных величин Знаки операндов учитьшаются при фиксации знаков результата, причем

знак суммы совпадает со знаком первого операнда, а знаку разности присваивается знак большего из операндов, что следует из таблицы.

в соответствии с данными таблицы можно определить нахождение результата следующим образом: если знаки операндов, записанные в знаковые

разряды регистров 1 и 2, совпадают, то результат находится в сумматоре 3, в противном случае результат следует считывать из регистра 4. Сдвиг информации в регистрах 1 и 2 вьтол- 5 ринется при поступлении сигналов управления сдвигом по. шине 27, сдвиг информации в сумматоре 3 и регистре 4 - при поступлении сигналов управления сдвигом по шине 28. 10

Рассмотрим пример алгебраического .сложения двух чисел А 9 и В 4. Исходные числа в регистрах 1 и 2 и сумматоре 3 представлены в следующем виде:15

3111111111 (А)

1111111111 (А)

2111100000 (В)

При одновременном сдвиге содержи 20 ого обоих регистров 1 и 2 на выоде элемента И 7 присутствует едияичный сигнал в течение 4С, где

С - время сдвига одной единицы в регистрах 1, 2 и 4 и сумматоре 3, 25 который при подаче через элемент ИЛИ 11 с выхода 15 узла 5 суммирования по модулю два на вход сумматора 3 приводит к: увеличению его соержимого, т.е. ранее записанного зо

числа А, на величину общей части операндов А и В, т.е. на число 4. В результате этого сложения в сумматоре 3 образуется сумма исходных чисел (А + В), а регистр 2 обнулен. 5

При дальнейшем сдвиге информации в регистре 1 единичный сигнал присутствует на выходе элемента И 8, а следовательно, на выходах 16 и 17 узла 5 суммирования по модулю два 40 в течение времени Зт;. Таким образом происходит запись разности (А-В) в сдвиговьм регистр 4 с выхода 16 узла 5 суммирования по модулю два, одновременно р этим осуществляется 45 запись знака числа А через элементы И 19 и ИЛИ 21 узла 6 записи знака в знаковый разряд сдвигового регистра 4, поскольку в данном случае выполняется соотношение А В и зна- 50 ку разности присваивается значение знака большего операнда А. Сдвиг информации в регистре 1 выполняется до полного его обнуления по сигналу управления сдвигом, поступающему 55 по шине 27.

При алгебраическом сложении двух чисел возможен случай, когда А В

т.е. когда исходные величины, например, следую1цие: А 4иВ 9.В этом случае общая часть обоих чисел, определенная узлом 5 суммирования по модулю два и поступающая с его выхода 15, при суммировании с находящимся в сумматоре 3 операндом А дает удвоенное значение общей части чисел А и В, т.е. величину 2А, равную 8. Разность операндов (А-В), равная 5, в виде единичного сигна.ла, существукмцего на входе элемента И 9 в течение времени 5Х, приводит к появлению такого же единичного сигнала такой же длительности на выходах 15, 16 и 18 узла 5 суммирования по модулю два. Таким образом, разность операндов (А - В) поступает на вход сумматора 3 и участвует в формировании суммы исходных величин, поскольку А + В 2А + + (А - В). С выхода 16 узла 5 суммирования по модулю два разность записывается в сдвиговый регистр 4, а также разрешается запись знака числа В через элементы И 20 и ШШ 21 узла 6 записи знака в знаковьй разряд сдвигового -регистра 4 по сигналу с выхода 18 узла 5 суммирования по модулю два. Сдвиг содержимого :регистра 2 вьшолняется до полного его обнуления по сигналу управления сдвигом, nocTynaic ;eMy по шине 27. Следовательно, сумма двух исходных чисел формируется в. сумматоре 3, разность - в сдвиговом регистре 4, причем знаку разности присваивается значение знака больиего операнда.

В предлагаемом устройстве для алгебраического сложения чисел предусмотрено одновременное получение суммы и разности исходных чисел, которые формируются узлом суммирования по модулю два во время параллельного сдвига информации, представленной в единичном нормальном коде в обоих сдвиговых регистрах операндов. Повьш1ение быстродействия предлагаемого устройства достигается за счет того, что в нем нет необходимости вьшолнения коррекции результата выг1итания двух чисел, которая необходима в известном устройстве. Это обусловлено тем, что в известном устройстве вь1читание выполняется путем поразрядного суммирования прямого кода одного операнда и обратного кода второго операнда.

+ +

+ +

+

Знак большего операнда

То же

Знак большего операнда

+ -f

Знак большего операнда

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для сложения и вычитания | 1984 |

|

SU1193664A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЙ | 1992 |

|

RU2042186C1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Арифметическое устройство | 1979 |

|

SU849206A2 |

УСТРОЙСТВО ДЛЯ АЛГЕБРАИЧЕСКОГО СЛОЖЕНИЯ ЧИСЕЛ, содержащее два сдвиговых регистра,узел суммирования по модулю дна и узел записи знака результата, содержащий элемент ИЛИ, причем входы разрядов первого сдви.гового регистра соединены с входами первого операнда устройства,.входы разрядов второго сдвигового регистра соединены с входами второго операнда устройства, входы управления сдвигом первого и второго сдвиговых регистров подключены к входу синхронизации устройства, выходы первого и второго сдвиговых регистров подключены к соответствующим входам узла суммирования по модулю-два, отличающееся тем, что, с целью повьшения быстродействия устройства, оно содержит сумматор, третий сдвиговьй регистр, узел суммирования по модулю два содержит три элемента И, два элемента ИЛИ и элемент НЕ, а узел записи знака результата дополнительно содержит два элемента И, при этом входы разрядов сумматора подключены к входам первого операнда устройства, первый и второй входы первого элемента И узла суммирования по модулю два соединены соответственно с первым и вторым входами узла суммирования по модулю два, а выход подключен к входу элемента НЕ узла суммирования по модулю два, выход которого подключен к первым входам второго и третьего элементов И узла суммирования по модулю два, вторые входы .которых соединены соответственно с первым и вторым входами первого элемента И узла суммирования по модулю два, а выходы подключены к входам первого элемента ИЛИ узла ;суммирования по модулю два, выход которого подключен к информацион(Л ному входу третьего сдвигового регистра, входы второго элемента ИЛИ узла суммирования по модулю два соединены с выходами первого и .третьего элементов И узла суммирования по модулю два, а выход подключен к информационному входу сумматосо эъ ра, выходы, знаковых разрядов первого и второго сдвиговых регистров подключены к первым входам соответствующих элементов И узла записи 4 знака, вторые входы которых соедиэо нены с выходами соответственно второго и третьего элементов И узла суммирования по модулю два, входы элемента ИЛИ узла записи знака подключены к выходам первого и второго элементов И узла записи знака, а вьгход подключён к входу знакового разряда третьего сдвигового регистра, вход управления сдвигом которого соединен с входом синхронизации устройства, управляющий вход сумматора подключен к входу синхронизации устройства.

t5

2S

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для последовательного сложения и вычитаний чисел | 1976 |

|

SU579613A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Арифметика цифровых машин | |||

| М., | |||

| Наука, 1969, .с | |||

| ДИФФЕРЕНЦИАЛЬНАЯ ТЕРМИОННАЯ ЛАМПА | 1920 |

|

SU294A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-01-23—Публикация

1983-03-18—Подача