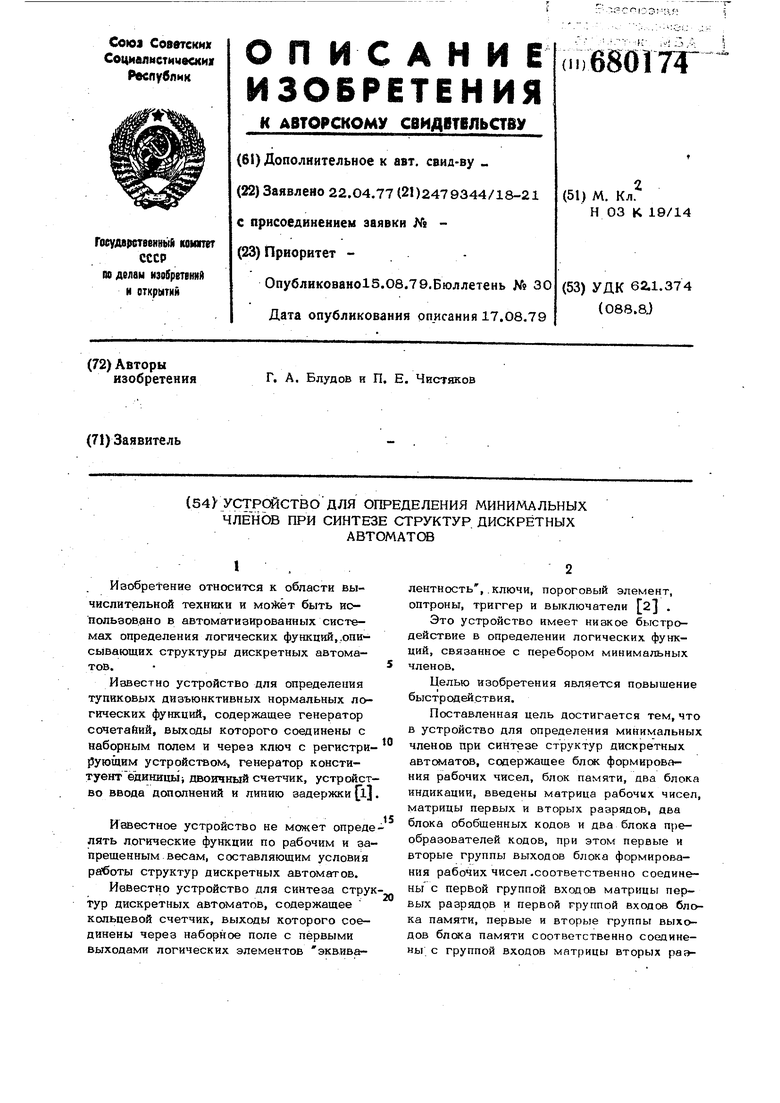

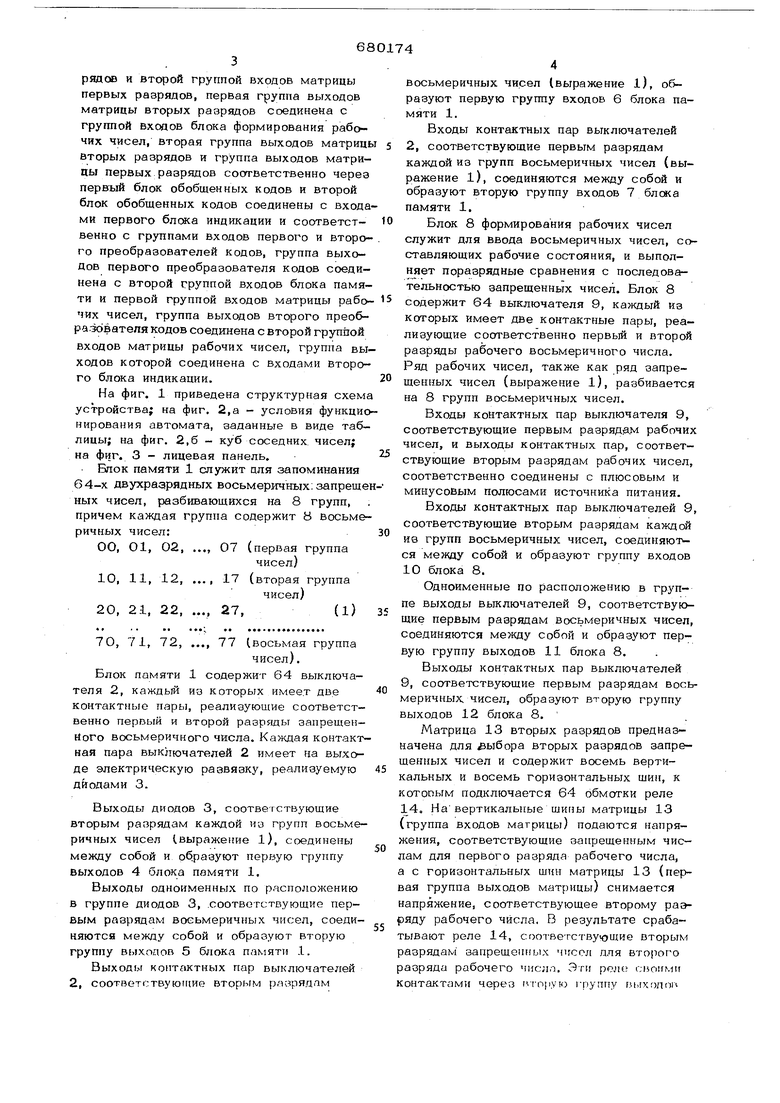

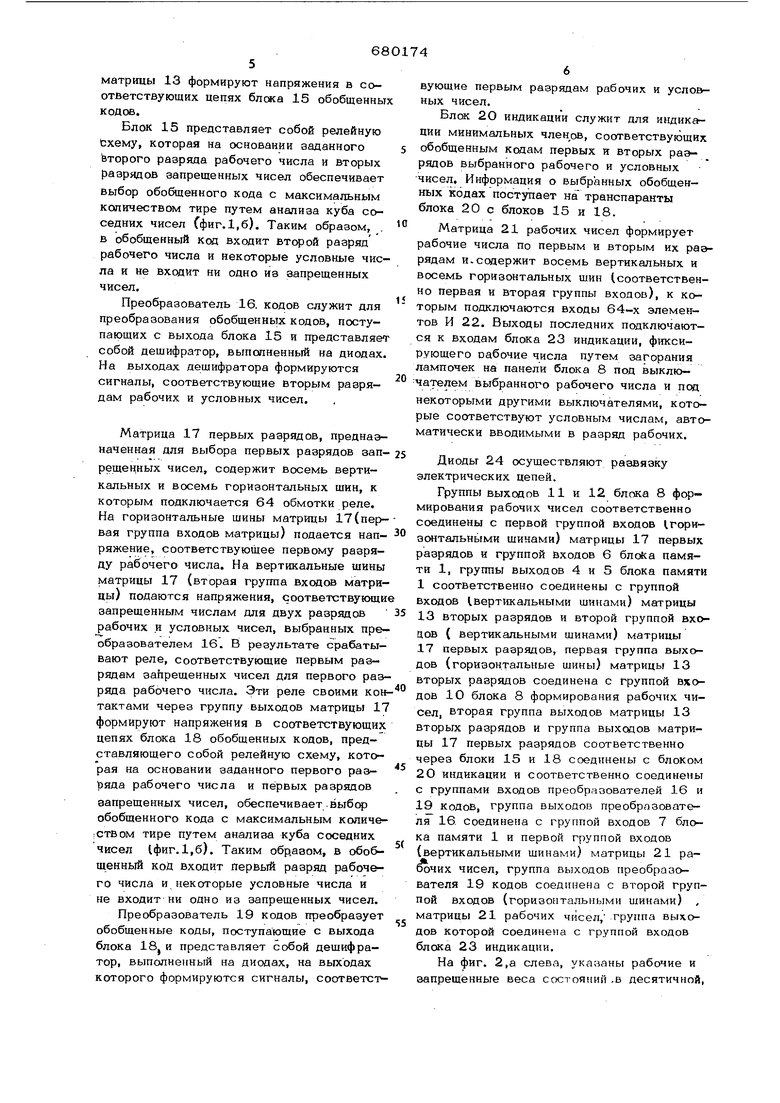

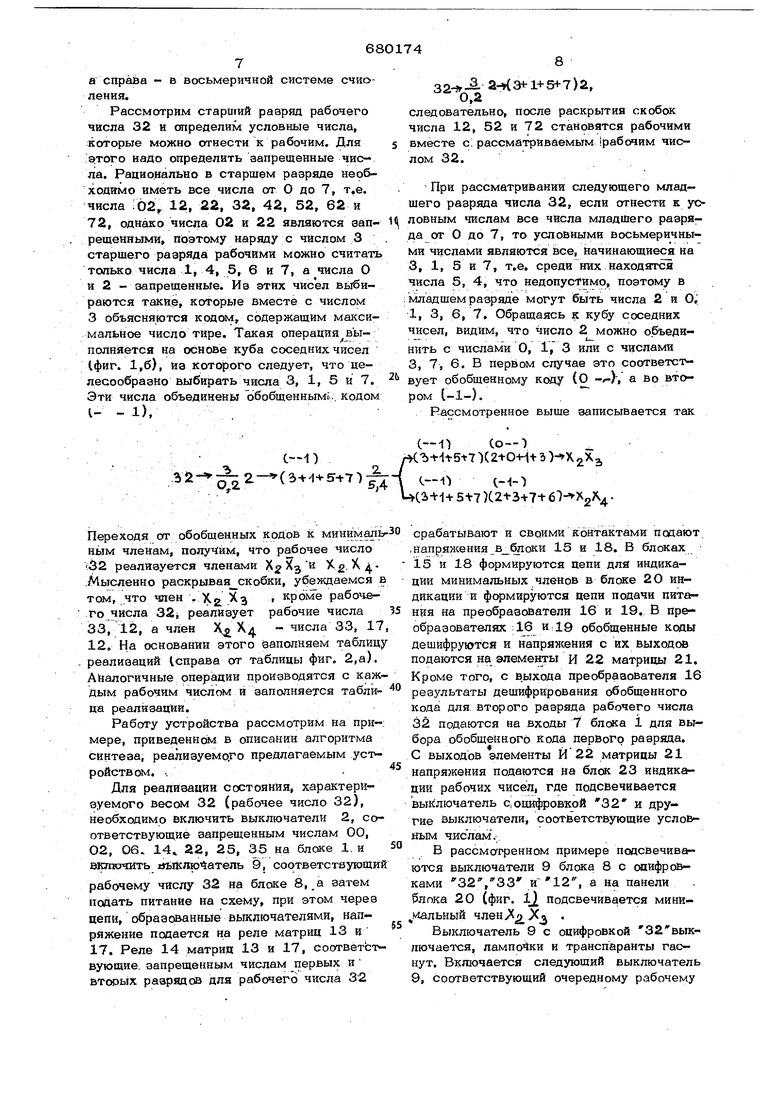

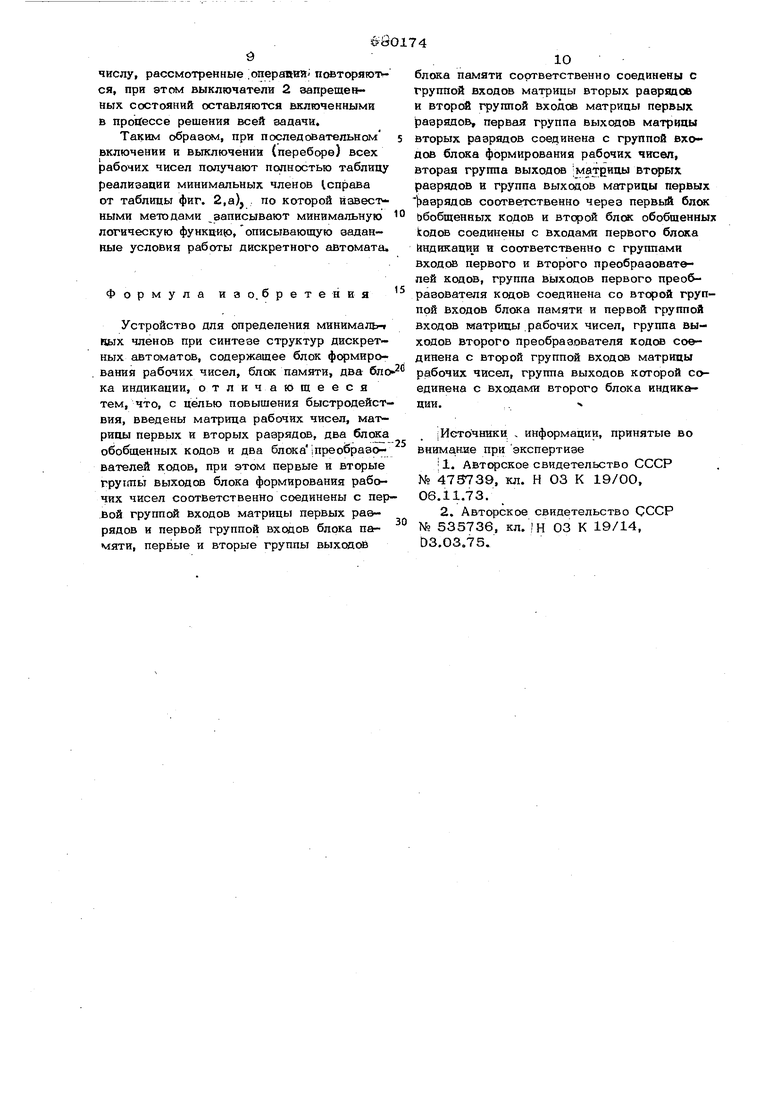

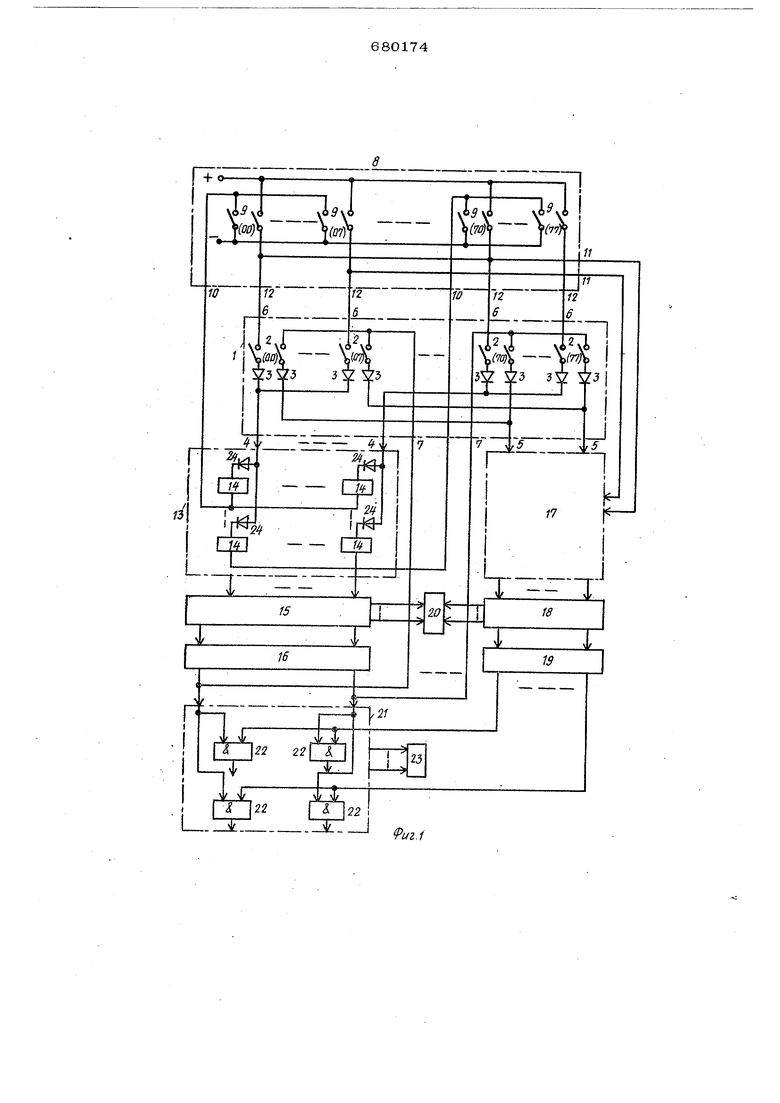

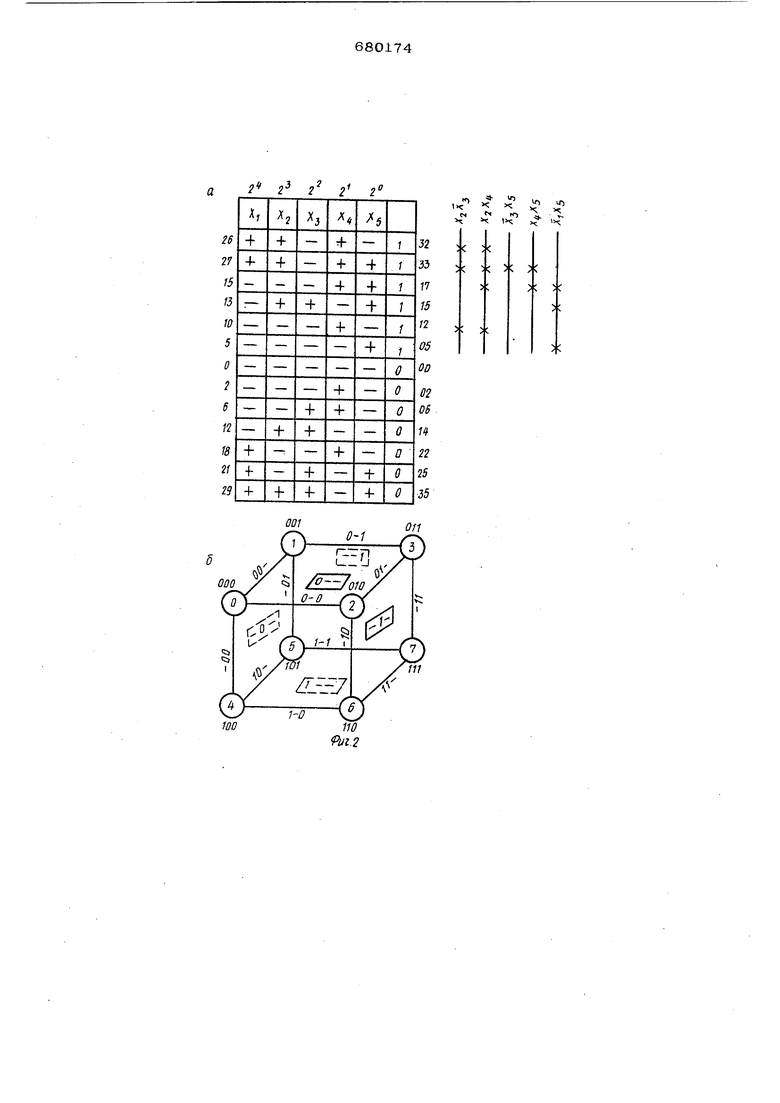

рядов и второй группой входов матрицы первых разрядов, первая группа выходов матрицы вторых разрядов соединена с группой входов блока формирования рабочих чисел, вторая группа выходов матриц вторых разрядов и группа выходов матрицы первых разрядов соответственно через первый блок обобщенных кодов и второй блок обобщенных кодов соединены с входа ми первого блсяса индикации и соответственно с группами входов первого и второ го преобразователей кодов, группа выходов первого преобразователя кодов соединена с второй группой входов блока памяти и первой группой входов матрицы рабо чих чисел, группа выходов второго преобра.зователя кодов соединена с второй группой входов матрицы рабочих чисел, группа вы ходов которой соединена с входами второго блока индикации. На фиг. 1 приведена структурная схем устройства; на фиг, 2,а - условия функцио нирования автомата, заданные в виде таблицы; на фиг. 2,6 - куб соседних чисел; на фиг. 3 - лицевая панель. Блок памяти 1 служит цля запоминания 64-х двухраарядных восьмеричных; запрет е ных чисел, разбивающихся на 8 групп, причем каждая группа содержит 8 восьме чисел: ОО, О1, 02, ..., 07 (первая группа 10, 11, 12, ..., 17 (вторая группа 20, 21, 22, ..., 27,(1) 70, 71, 72, ..., 77 (восьмая группа чисел). Блок памяти 1 содержит 64 выключателя 2, каждый иэ которых имеет две контактные пары, реализующие соответственно первый и Второй запрещенного восьмеричного числа. Каждая контакт ная пара выключателей 2 имеет на выходе электрическую развязку, реализуемую диодами 3. Выходы диодов 3, соответствующие вторым разрядам каждой иа групп восьмеричных чисел (выражение 1), соединены между собой и образуют первую группу выходов 4 блока памяти 1. Выходы одноименных по расположению в группе диодов 3, .соответствующие первым разрвдам восьмеричных чисел, соединяются между собой и образуют вторую группу в()1ходов 5 блока памяти 1. Выходы контактных пар выключателей 2, соответствующие вторым разрядам восьмеричных чисел (выражение 1), образуют первую группу входов 6 блока памяти 1. Входы контактных пар выключателей 2, соответствующие первым разрядам каждой из групп восьмеричных чисел (выражение 1), соединяются между собой и образуют вторую группу входов 7 блсжа памяти 1. Блок 8 формирования рабочих чисел служит для ввода восьмеричных чисел, составляющих рабочие состояния, и выполняет поразрядные сравнения с последовательностью запрещенных чисел. Блок 8 содержит 64 выключателя 9, каждый из которых имеет две контактные пары, реализующие соответственно первый и второй разряды рабочего восьмеричного числа. Ряд рабочих чисел, также как ряд запрещенных чисел (выражение 1), разбивается на 8 групп восьмеричных чисел. Входы контактных пар выключателя 9, соответствующие первым разрядам рабочих чисел, и выходы контактных пар, соответствующие вторым разрядам рабочих чисел, соответственно соединены с плюсовым и минусовым полюсами источника питания. Входы контактных пар выключателей 9, соответствующие вторым разрядам каждой ив групп Восьмеричных чисел, соединяются собой и образуют группу входов 10 блока 8. Одноименные по расположению в группе выходы выключателей 9, соответствующие первым разрядам Восьмеричных чисел, соединяются между собой и образуют первую группу выходов 11 блока 8. Выходы контактных пар выключателей 9, соответствующие первым разрядам восьмеричных, чисел, образуют вторую группу выходов 12 блока 8. Матрица 13 вторых разрядов предназначена для выбора вторых разрядов запрещенных чисел и содержит восемь вертикальных и восемь горизонтальных щин, к котопым подключается 64 обмотки реле 14. Навертикальные щигзы матрицы 13 (группа входов матрицы) подаются напряжения, соответствующие запрещенным числам для первого разряда рабочего числа, а с горизонтальных шин матрицы 13 (первая группа выходов матрицы) снимается напряжение, соответствующее второму раэряду рабочего числа, В результате срабатывают реле 14, соответствучэщие вторым разр5щам запрещенных чисел для второго разряда рабочего чнслл. Эти рело сиоими контактами через м-г-орую i-pynny fiыxr)пoг матрицы 13 формируют напряжения в соответствующих цепях блока 15 обобщенны кодов. БЛОК 15 представляет собой релейную Схему, которая на основании заданного ёторого разряда рабочего числа и вторых разрадов запрещенных чисел обеспечивает выбор обобщенного кода с максимальным количеством тире путем анализа куба соседних чисел Сфиг.1,б). Таким образом, в обобщенный код входит разряд рабочего числа и некоторые условные чис ла и не входит ни одно из запрещенных чисел. Преобразователь 16. кодов служит для преобразования обобщенных кодов, поступающих с выхода блока 15 и представляе собой дешифратор, выполненный на диодах На выходах дешифратора формируются сигналы, соответствующие вторым разрядам рабочих и условных чисел. Матрица 17 первых раэрадов, предназначенная для выбора первых разрядов зап рещен.ных чисел, содержит восемь вертикальных и восемь горизонтальных шин, к которым подключается 64 обмотки репе. На горизонтальные шины матрицы 17(пер вая группа входов матрицы) подается нап ряжение, соответствующее первому разряду рабочего числа. На вертикальные шины матрицы 17 (вторая группа входсв матрицы) подаются напряжения, соответствующи запрещенным числам для двух разрядов рабочих и условных чисел, выбранных преобразователем 16. В результате срабатывают реле, соответствующие первым разрядам запрещенных чисел для первого разрада рабочего числа. Эти реле своими KOH тактами через группу выходов матрицы 17 формируют напряжения в соответствующих цепях блока 18 обобщенных кодов, представляющего собой релейную схему, которая на основании заданного первого разряда рабочего числа и первых разрядов запрещенных чисел, обеспечивает-выбор обобщенного кода с максимальным количеiCTBOM тире путем анализа куба соседних чисел (фиг. 1,б). Таким образом, в обобщенный код входит первый разряд рабочего числа и некоторые условные числа и не входит ни одно из запрещенных чисел. Преобразователь 19 кодов преобразует обобщенные коды, поступающие с выхода блока 18j и представляет собой дещифратор, выполненный на диодах, на выходах которого формируются сигналы, соответствующие первым разрядам рабочих и условных чисел. Блок 2О индикации служит для ивдика- ции минимальных , соответствующих обобщенным кодам первых и вторых раэрадов выбранного рабочего и условных чисел. Информация о выбранных обобщенных кодах поступает на транспаранты блока 20 с блоков 15 и 18. Матрица 21 рабочих чисел формирует рабочие числа по первым и вторым их разрядам и.содержит восемь вертикальных и восемь горизонтальных шин (соответственно первая и вторая группы входов), к которым подключаются входы 64-х элементов И 22. Выходы последних подключаются к входам блока 23 индикации, фиксирующего сабочие числа путем загорания лампочек на панели блока 8 под выклю- чателем выбранного рабочего числа и под некоторыми другими выключателями, которые соответствуют условным числам, автоматически вводимыми в разряд рабочих. Диоды 24 осуществляют развязку электрических цепей. Группы выходов 11 и 12 блсжа 8 формирования рабочих чисел соответственно соединены с первой группой входов (.гориаонтальными шинами) матрицы 17 первых разрядов и группой входов 6 блока памяти 1, группы выходов 4 и 5 блока памяти 1 соответственно соединены с группой Входов (вертикальными шинами) матрицы 13 вторых разрядов и второй группой вхоцов ( вертикальными шинами) матрицы 17 первых разрядов, первая группа выходов (горизонтальные шины) матрицы 13 вторых разрядов соединена с группой вход в 10 блока 8 формирования рабочих чисел, вторая группа выходов матрицы 13 вторых разрядов и группа выходов матрицы 17 первых разрядов соответственно через блоки 15 и 18 соединены с блоком 2О индикации и соответственно соединены с группами входов преобразователей 16 и 19 кодов, группа выходов преобразователя 16. Соединена с группой входов 7 блока памяти 1 и первой группой входов (вертикальными шинами) матрицы 21 рабочих чисел, группа выходов преобразователя 19 кодов соединена с второй группой входов (горизонтальными шинами) , матрицы 21 рабочих чисел, группа выходов которой соединена с группой входов блока 23 индикации. На фиг. 2,а слева, укаваны рабочие и запрещенные веса состояний,в десятичной,

78

а справа - в восьмеричной системе счно-3 о./-г ц-Rf7Уй

ления.

Рассмотрим старший разряд рабочегоследовательно, после раскрытия скобок

числа 32 и определим условные числа,числа 12, 52 и 72 становятся рабочими

:которые можно отнести к рабочим. Для 5вместе с рассматриваемым рабочим чис:этого надо определить запрещенные час-лом 32. ла. Рационально в старшем разряде необходимо иметь все числа от О до 7, т.е.При рассматривании следующего младчисла Г02,, 12, 22, 32, 42, 52, 62 ишего разряда числа 32, если отнести к ус72, однако числа 02 и 22 являются зап- 1 ловным числам все числа младшего разрярещенными, поэтому наряду с числом 3 .Д.от О до 7, то условными восьмеричныстарше.го разряда рабочими можно считать и числами являются все, начинающиеся на

только числа 1, 4, 5, 6 и 7, а числа О 1, 5 и 7, т.е. среди них находятся

и 2 - запрещенные. Из этих чисел вьгби- Р/ что недопуст имо, поэтому в

раются такие, которые вместе с числом младшем разряде могут быть числа 2 и О,.

3 объясняются кодом, содержащим макси-1| 3, 6, 7. Обращаясь к кубу соседних

мальное число тире. Такая операция вы-чисел, видим, что число 2 можно объедиполняется на основе куба соседних чиселнить с числам и О, IV 3 или с числами

Чфиг. 1,б), из которого следует, что це-3, 7, 6. В первом случае это соответстлесообразно выбирать числа 3, 1, 5 и 7. ьвует обобщенному коду (О -К а во втоЭти числа объединены обобщеннымь.. кодомром 1-1-). I- - 1), Рассмотренное выше записывается так

)Mb-Vit5t7X2tO-Ht5),

-(.7)-/ .„,v ,.,-,

Переходя от обобщенных кодов к минималь-ЗОсрабатывают и своими контактами подают

ным членам, получим, что рабочее число,напряжения B 6jioKn 15 и 18. В блоках

32 реализуется членами и 18 формируются цепи для индика.Мысленно раскрывая скобки, убеждаемся вции минимальных членов в блоке 20 интом, что член Xg Хз кроме рабоче-дикации и ффмируются цепа подачи питаго.числа 32i реализует рабочие числа 35ния на преобразователи 16 и 19, В пре33, 12, а член Х Х, - числа 33, 17,образователях 16 И;19 обобщенные коды

12. На основавйн этого ваполняем таблицудешифруются И напряжения с их выходов

реализаций справа от таблицы фиг. 2,а).подаются на элемееты И 22 матрицы 21.

Диалогичные операции производятся с каж-Кроме того, с в.ыхода преобразователя 16

дым рабочим числом и заполняется табли- результаты дешифрирования обобщенного

ца реализации.кода для. второго разряда рабочего числа

Работу устройства рассмотрим на при-:32 подаются на входы 7 блдеа 1 для вымере, приведеннс в описании алгоритмабора обобщенного кода первого разряда,

синтеза, реализуемого предлагаемым уст-С выходов элементы И22 матрицы 21

ройством. ...напряжения подаются на блок 23 инднкаДля реализации состояния, характери-ции рабочих чисел, где подсвечивается

зуемого весом 32 (рабочее число 32),выключатель оцифровкой 32 и друнеобходимр включить выключатели 2, со-р выключатели, соответствующие условответствующие запрещенным числам 00, числам .

О2, Об. 14 22, 25, 35 на блоке 1. и ° В рассмотренном примере подсвечивавкпгочить ш гклю атель 9, соответствующийются выключатели 9 блока 8 с отифроврабочему числу 32 на блоке 8,.а затемками 32,33 , а на панели подать питание на схему, при этом через пка 20 (фиг. 1 подсвечивается миницепи, образованные выключателями, над- иальный член.- ряжение подается на реле матриц 13 нВыключатель 9 с оцифровкой З2вык17. Реле 14 матриц 13 и 17, соответЬт-лючается, лампоЧки и транспаранты гасвующие. запрещенным числам первых инут. Включается следующий выключатель BToobix разрядов для рабочего числа 329, соответствующий очередному рабочему

680174

(-1)Со - -)

U(3-H+5t7)C2+3+7-e6)2 4числу, рассмотренные операция; повторягот ся, при 8тс)М выключатели 2 аапрещеиных состояний оставляются включенными в процессе решения всей задачи. Таким образсм, при последовательном включении и выключении (переборе) всех рабочих чисел получают полностью таблицу реализации минимальных членов справа от таблицы фиг. 2,а), . по которой йзвест ными методами записывают минимальную логическую функди(р, описывающую заданные условия работы дискретного автомата. Формула изо. бретення Устройство для определения минималь- ных членов при синтезе структур дискретных автоматов, содержащее блок формирования рабочих чисел, блсж памяти, два бло ка индикации, отличающееся тем, что, с целью повышения быстродействия, введены матрица рабочих чисел, матрицы первых и вторых разрядов, два блсжа обобщенных кодов и два блока шреобразователей кодов, при этом первые и вторые грутшы Выходов блока формирования рабочих чисел соответственно соединены с пер вой группой входов матрицы первых разрядов и первой группой входов блока патмяти, первые и вторые группы выходе® блока памяти соответственно соединены с группой входов матрицы вторых разрядов и второй группой входе матрицы первых разрядов, первая группа выходов матрицы вторых разрядов соединена с группой входов блока формирования рабочих чисел, вторая группа выходов матрицы вторых разрядов и группа выходов матрицы первых разрядов соответственно через первый блок Ьбобщенных кодов и второй блок обобщенных одов соединены с входами первого блока индикации н соответственно с группами входов первого и второго преобразоват&лей кодов, группа выходов первого преобразователя кодов соединена со второй группой входов блока памяти и первой группой входов матрицы .рабочих чисел, группа выходов второго преобразователя код№ соединена с группой входов матрицы рабочих чисел, группа выходов которой соединена с Входами второго блока индикации.. :Источники . информации, принятые во внимание при экспертизе i 1. Авторское свидетельство СССР № 475739, кл. Н 03 К 19/00, 06.11.73. 2. Авторское свидетельство СССР № 535736, кл. IH 03 К 19/14, D3.03.75.

R;

J JчЬи

p 91

12 6

Iff

,JJ

1 6 0

j -

7- 7

I з2з

U-.

-. fy

и I

/4

fULI

/5

7

ц I

-t

11

12

12

6

Л

i

Я9 У77Л I

35Z 23 3V

,5

,5

} .

M

r-

/7

I

zd

,

20

7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения таблицы реализации минимальных членов при синтезе структуры дискретных автоматов | 1980 |

|

SU869046A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ МИНИМИЗАЦИИ СТРУКТУР ЛОГИЧЕСКИХ СХЕМ | 1972 |

|

SU428387A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ПРОСТРАНСТВЕННОЙ ИЗБИРАТЕЛЬНОСТИ АНТЕНН | 1992 |

|

RU2082986C1 |

| Пульт учащегося для устройства обучения языкам | 1985 |

|

SU1354235A1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| Устройство защиты и автоматики распределительной подстанции | 1988 |

|

SU1584023A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

Zl

22 l

3L.

I

II о

LS

22

23

j

.f

2 2

/

011

РаВочие чис/ia

5 8 9 g

9 б

®

®

® Р ®

UZ.3

Запрещенные числа

8869

10 20 30

00

JS88

ifO506070

§988

0 11213)

9re8

- /Si6f71

88a

02122232

2 52 62

12

59 re

Ob/3 53J3

89 §

.JJ

55 5J

iJ4

9 &S

(

.55

«8 f

555 65fS

98 9

06IB zsJe

r Г 5I

656 6676

0711 2737

9998

HI57 6777

Авторы

Даты

1979-08-15—Публикация

1977-04-22—Подача