(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1974 |

|

SU547763A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь целых двоично- десятичных чисел в двоичные | 1978 |

|

SU750478A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей в специализированных вычислительных машинах.

Известен преобразователь двоично-десятичных чисел в двоичные, содержащий регистр числа, информационную шину, блок управления, управляюш,ую шину, переключатель эквивалентов, распределитель импульсов, запоминаюш,ее устройство, формирователь двоичного эквивалента тетрады, регистр сдвига и двоичный сумматор 1.

Недостаток указанного преобразователя состоит в ограниченных функциональных возможностях, связанных с невозможностью обработки чисел в форме с плавающей запятой.

Наиболее близким к предлагаемому по технической сущности и схемному построению является преобразователь двоично-десятичного кода в двоичный код, содержащий регистр тетрады, блок управления, распределитель импульсов, регистр адреса, первь1Й блок памяти, блок умножения, двоичный сумматор, регистр сдвига, причем первый выход блока управления соединен с входом распределителя импульсов, первый выход которого соединен с тактовым входом регистра адреса, управляющий вход которого подключен ко второму выходу блока управления, второй выход распределителя импульсов соединен с управляющим входом первого блока памяти, адресный вход которого подключен к первому выходу регистра адреса, выход регистра тетрады соединен с первым входом блока умножения, выход которого подключен к первому входу двоичо ного сумматора, выход двоичного сумматора соединен с входом регистра сдвига, выход старшего разряда которого соединен с вторым входом двоичного сумматора, первая группа выходов регистра сдвига является группой выходов мантиссы преобразователя 2.

Процесс преобразования в этом устройстве заключается в суммировании двоичных эквивалентов десятичных тетрад, причем J двоичные эквиваленты хранятся в блоке памяти и считываются из него последовательным кодом. Однако и это устройство имеет недостаточно широкие функциональные возможности, так как не может оперировать

с числами, представленными в формате с плавающей запятой.

Цель изобретения - расширение функциональных возможностей, заключающееся в обеспечении возможности преобразования чисел в форме с плавающей запятой.

Для достижения поставленной цели в преобразователь двоично-десятичного кода в двоичный код, содержащий регистр тетрады, блок управления, вход которого является входом признака десятичной мантиссы преобразователя, распределитель импульсов, регистр адреса, первый блок памяти, блок умножения, двоичный сумматор, регистр сдвига, причем первый выход блока управления соединен с входом распределителя импульсов, первый выход которого соединен с тактовым входом регистра адреса, управляющий вход которого подключен ко второму выходу блока управления, второй выход распределителя импульсов соединен с управляющим входом первого блока памяти, адресный вход которого подключен к первому выходу регистра адреса, выход регистра тетрады соединен с первым входом блока умножения, выход которого подключен к первому входу двоичного сумматора, выход двоичного сумматора соединен с входом регистра сдвига, выход старшего разряда которого соединен с вторым входом двоичного сумматора, первая группа выходов регистра сдвига является группой выходов мантиссы преобразователя, дополнительно введены второй блок памяти, регистр двоичного порядка, элемент И, первый и второй коммутаторы, дополнительный регистр, элемент ИЛИ, группа элементов ИЛИ, вход блока управления подключен к первому входу элемента И и .к управляющим входам первого и второго коммутаторов, второй выход распределителя импульсов соединен с тактовым входом первого коммутатора, третий выход распределителя импульсов соединен с управляющим входом второго блока памяти, с вторым входом элемента И и тактовым входом второго коммутатора, второй выход регистра адреса подключен к адресному входу второго блока памяти, выход первого блока памяти и первый выход второго блока памяти через элемент ИЛИ соединены со вторым входом блока умножения, второй выход второго блока памяти соединен со входом регистра двоичного порядка, выходы которого являются выходами порядка преобразователя, выход старшего разряда регистра сдвига подключен к третьему входу элемента И, выход которого соединен с управляющим входом дополнительного регистра, вторая группа выходов регистра сдвига подключена к группе входов первого коммутатора, выходы которого соединены с информационными входами дополнительного регистра, выход которого соединен с информационным входом второго коммутатора, выход второго коммутатора через группу

элементов ИЛИ, вторые входы которых подключены к информационным входам преобразователя, соединен со входом регистра тетрады.

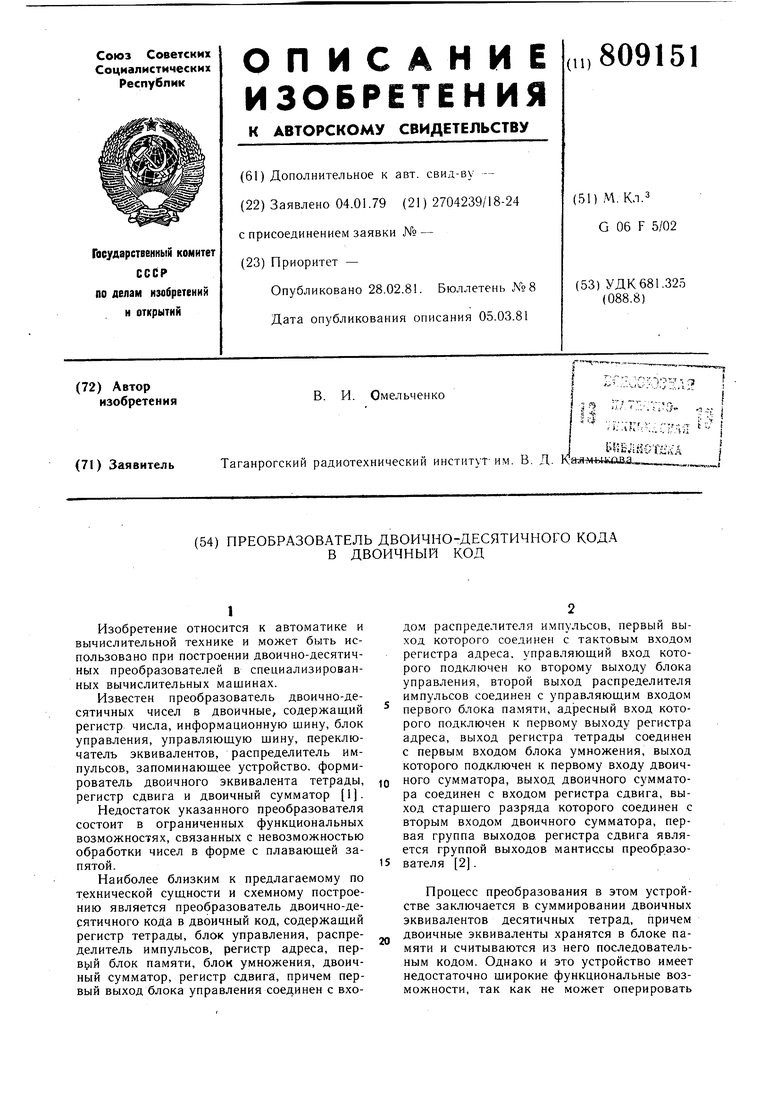

На фиг. 1 представлена структурная схема предлагаемого преобразователя.

Преобразователь содержит вход 1 пуска преобразователя, блок 2 управления, вход 3 знака десятичного порядка, вход 4 величины десятичного порядка, вход 5 признака десятичной мантиссы, элемент И 6, первый коммутатор 7, второй коммутатор 8, распределитель 9 импульсов, регистр 10 адреса, блоки 11 и 12 Памяти, элемент ИЛИ 13, регистр 14 двоичного порядка, регистр 15 тетрады, блок 16 умножения, двоичный сумматор 17, регистр 18 сдвига, дополнительный регистр 19, группу элементов ИЛИ 20, информационный вход 21 преобразователя, первые и вторые группы выходов 22 и 23.

Любое число двоично-десятичной системы счисления в формате с плавающей запятой

1 4-;o-|77;r.f(}можно представить в двоичной системе счисления в виде. .

4(|ТГ-ГУ5-/(е-2.

0 где Т - тетрада двоично-десятичного чис- ,

ла;

i - текущий номер десятичного разряда;

j - конечный номер десятичного разрядом;

5Р - десятичный порядок;

ч-двоичная константа; 10 -двоичный эквивалент младшего

разряда i-той тетрады; 1 -т,- двоичный порядок; -,, м. -десятичная мантисса.

Из этого вь ражения следует, что процесс преобразования заключается в преобразовании мантиссы двоично-десятичного числа, умножении полученного результата на двоичную константу и присвоении произведению необходимого двоичного порядка.

Предлагаемый преобразователь работает следующим образом.

По входу 5 признака десятичной мантиссы поступает соответствующий сигнал, который управляет первым режимом работы преобразователя. В регистр 15 тетрады последовательно одна за одной по информационному входу 21 через группу элементов ИЛИ 20 поступают тетрады преобразуемого двоично-десятичного числа.

Одновременно с каждой двоично-десятичной тетрадой в блок 2 управления по входу 1 пуска поступает управляющий синхроимпульс, обеспечивающий старт-стопный -режим работы устройства. Блок 2 управления вырабатывает сигнал пуска распределителя 9 и сигнал, управляющий изменением состояния регистра 10 адреса. Сигнал, с выхода регистра 10 адреса возбуждает требуемую ячейку первого блока 11 памяти, разряды которой опрашиваются распределенными импульсами, начиная с младшего разряда. Двоичный эквивалент младшего разряда старшей тетрады поступает с выхода первого блока 11 памяти на первый вход блока 16 умножения, на второй вход которого одновременно поступают четыре разряда тетрады. С выхода блока 16 умножения на первый вход двоичного сумматора 17 через элемент ИЛИ 13 поступает двоичный эквивалент старшей тетрады, суммируясь в данном цикле с нулевым содержимым регистра 18 сдвига.

Описанный процесс чтения необходимых ячеек первого блока 11 памяти, образования двоичных эквивалентов тетрады и суммирования его с содержимым регистра 18 сдвига повторяется J-1 раз. Отличие состоит лишь в том, что в последующих циклах содержимое регистра 18 сдвига не равно нулю. После преобразования мантиссы десятичного числа содержимое регистра 18 сдвига (множитель) параллельным кодом через первый коммутатор 7 записывается на дополнительный регистр 19 с последующей перезаписью младших четырех разрядов на регистр 15 тетрады. Затем поступают знак и величина деся -ичного порядка по шинам знака 3 и величины 4 десятичного порядка. Блок 2 управления вырабатывает сигналы пуска распределителя 9 и установки адреса на регистре 10 адреса. Сигнал с выхода регистра 10 адреса возбуждает необходимую ячейку второго блока 12 памяти, разряды которой опрашиваются распределенными импульсами, начиная с младшего разряда. Двоичная константа (множимое), считанная со второго блока 12 памяти, поступает на второй вход элемента ИЛИ 13, а затем на первый вход блока 16 умножения, на второй вход которого поступают четыре разряда множителя с регистра 15 тетрады. Полученное частичное произведение от умножения на четыре разряда множителя поступает на вход двоичного сумматора 17, с выхода которого четыре младших разряда записываются на дополнительный регистр 19, а оставшиеся разряды - на регистр 18 сдвига. Затем производится сдвиг содержимого дополнительного регистра 19 на четыре разряда с перезаписью следующих четырех разрядов множителя на регистр 15 тетрады.

Описанный процесс чтения необходимых ячеек второго блока 12 памяти, считывания двоичных констант и умножения их на четыре разряда множителя повторяется п/4 раза. Отличие состоит лишь в том, что в последующих циклах содержимое регистра 18 сдвига не равно нулю. При этом следует отметить, что двоичный порядок считывается параллельным кодом с той же ячейки второго блока 12 памяти на регистр 14 двоичного порядка. Результат преобразования снимается с выходов регистров 18 и 14 в виде двоичной мантиссы и двоичного порядка посредством первых и вторых групп выходов 22 и 23 преобразователя.

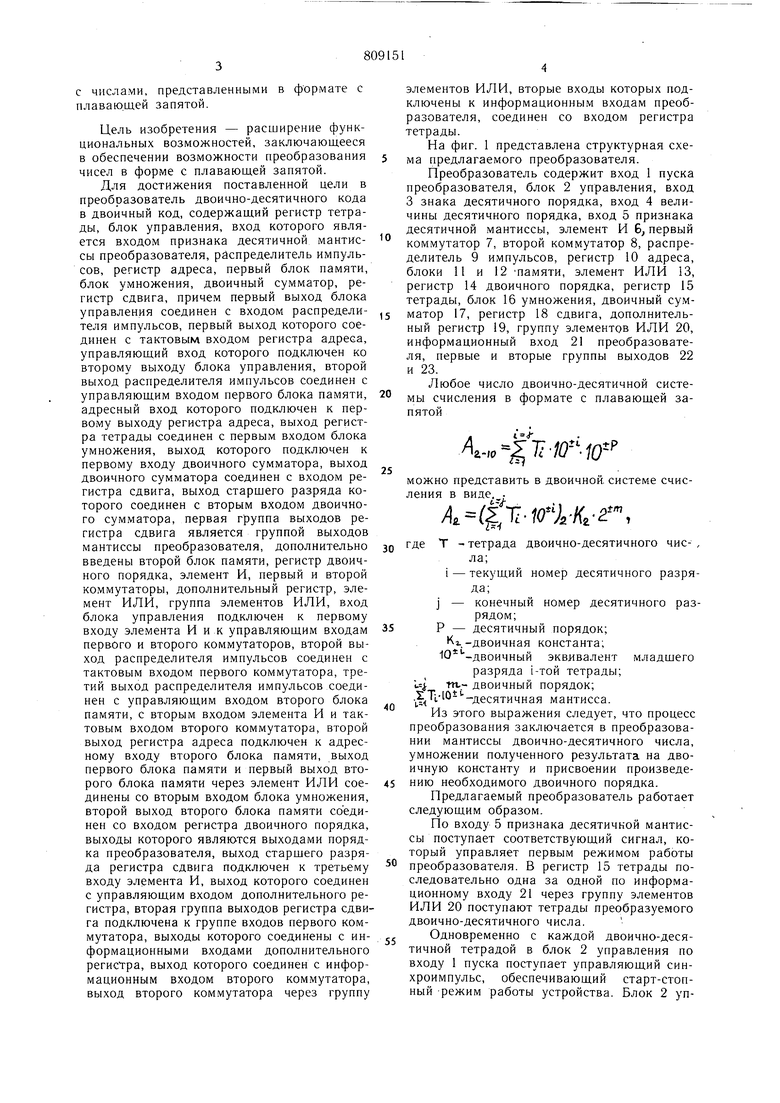

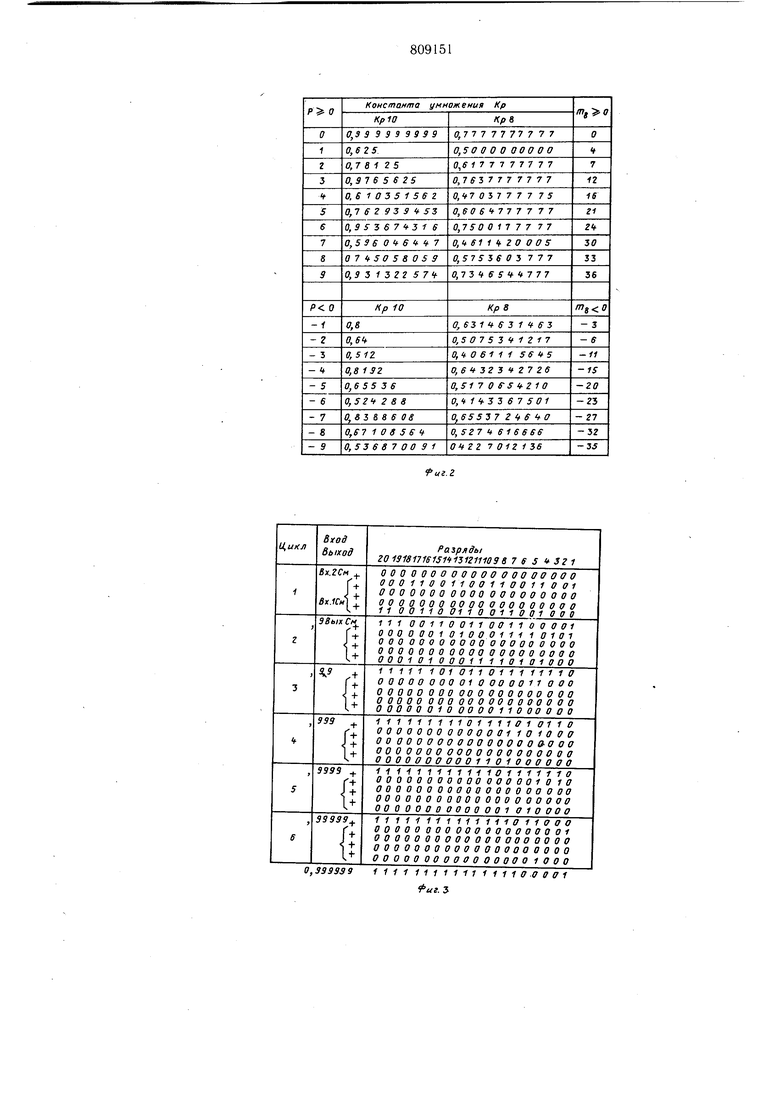

Константы умножения Кг и двоичные порядки гп представлены в таблице на фиг. 2. Таблица 2 состоит из трех столбцов. В первом столбце указывается десятичный порядок Р 10 с соответствующим знаком.

Во втором столбце представлена константа умножения в десятичном коде в восьмеричном коде. В третьем столбце помещен двоичный порядок гп в восьмеричной

5 системе счисления.

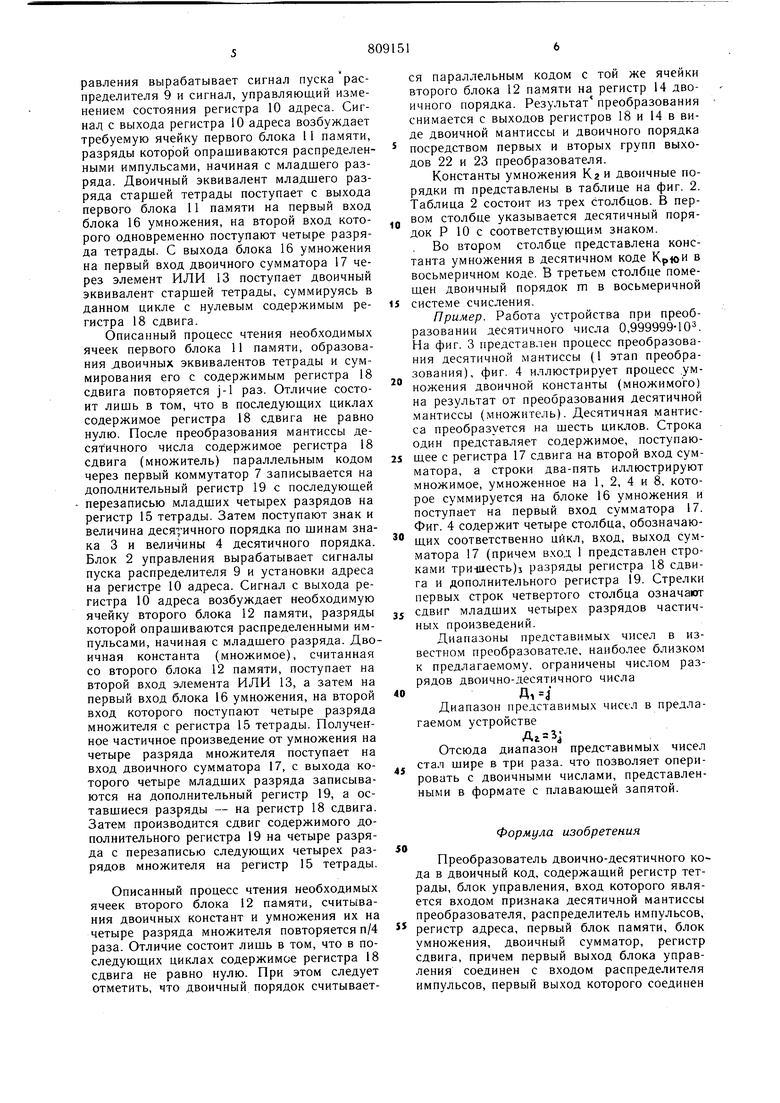

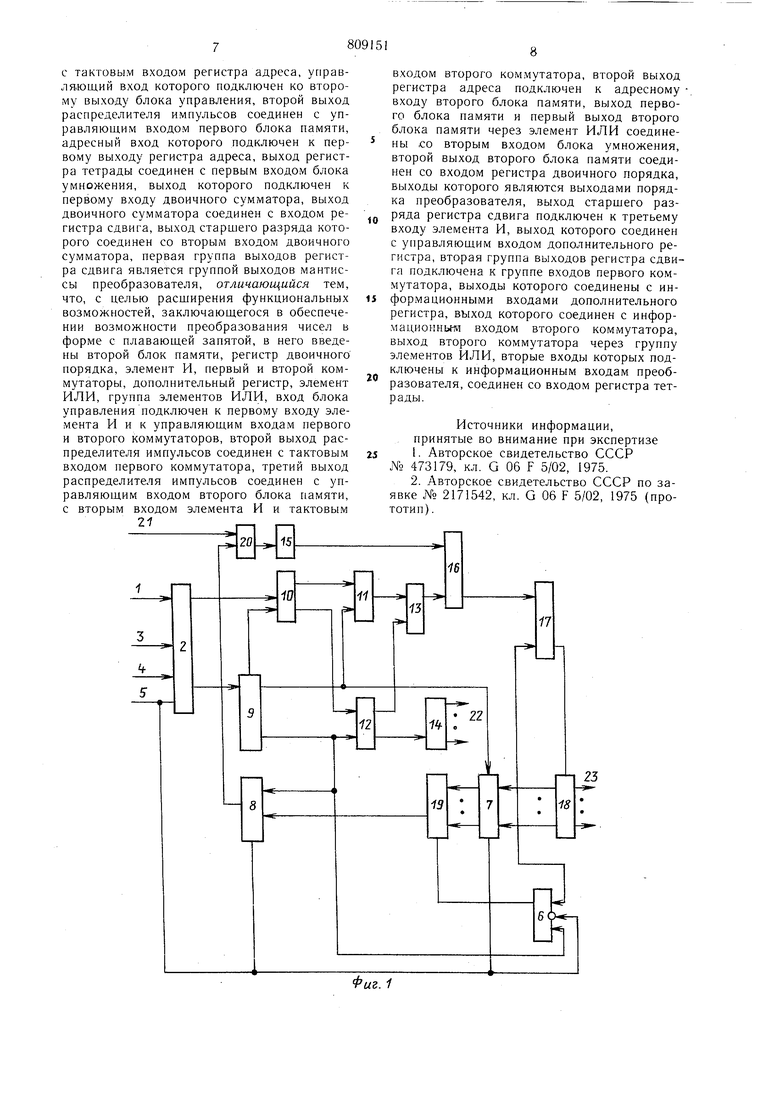

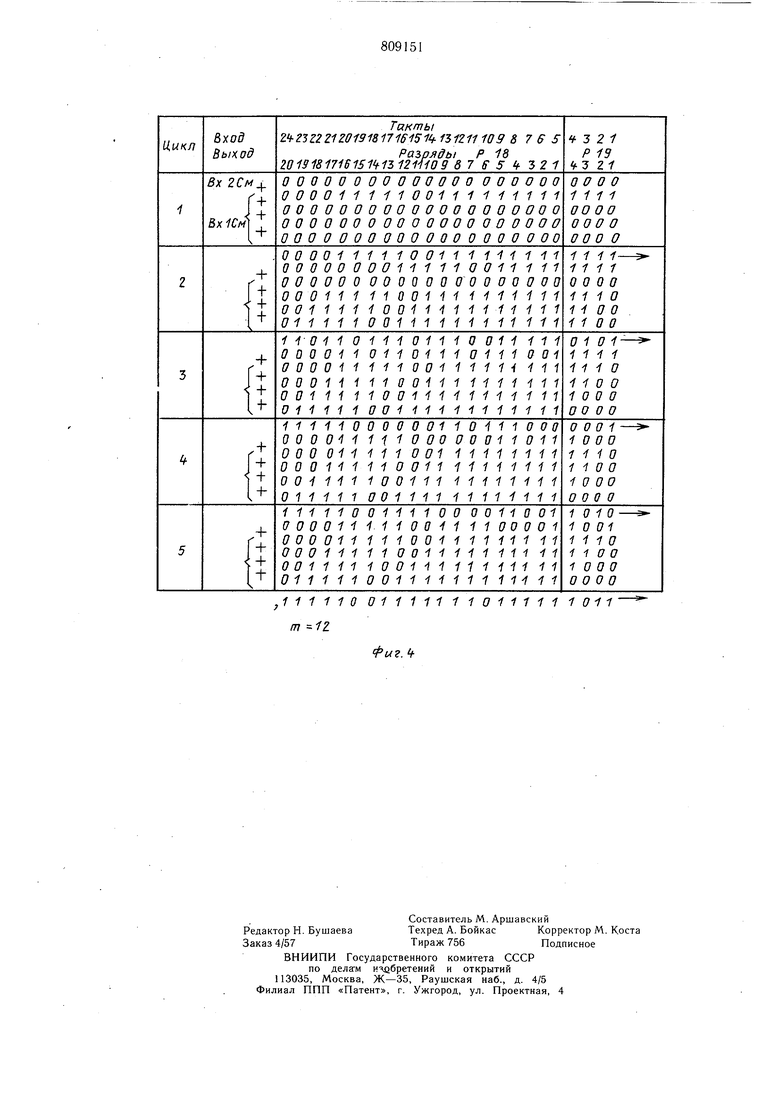

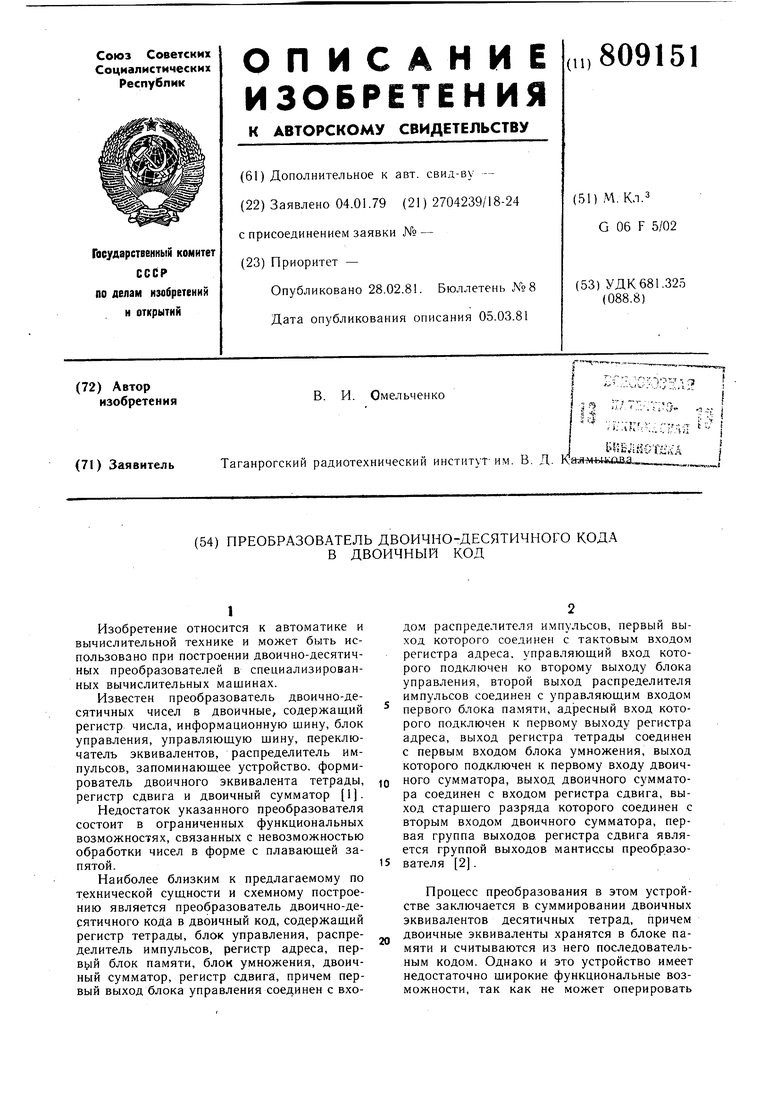

Пример. Работа устройства при преобразовании десятичного числа 0,99999910. На фиг. 3 представлен процесс преобразования десятичной мантиссы (I этап преобразования), фиг. 4 иллюстрирует процесс .ум0ножения двоичной константы (множимого) на результат от преобразования десятичной .мантиссы (множитель). Десятичная мантисса преобразуется на шесть циклов. Строка один представляет содержимое, поступающее с регистра 17 сдвига на второй вход сумматора, а строки два-пять иллюстрируют множимое, умноженное на 1, 2, 4 и 8, которое суммируется на блоке 16 умножения и поступает на первый вход сумматора 17. Фиг. 4 содержит четыре столбца, обозначаю0щих соответственно цикл, вход, выход сумматора 17 (причем ВХО.Я 1 представлен строками три-шесть)5 разряды регистра 18 сдвига и дополнительного регистра 19. Стрелки первых строк четвертого столбца означают

5 сдвиг младших четырех разрядов частичных произведений.

Диапазоны представимых чисел в известном преобразователе, наиболее близком к предлагаемому, ограничены числом разрядов двоично-десятичного числа

Д, i

Диапазон представимых чисел в предлагаемом устройстве

Aa 5j

Отсюда диапазон представимых чисел стал шире в три раза, что позволяет оперировать с двоичными числами, представленными в формате с плавающей запятой.

Формула изобретения

Преобразователь двоично-десятичного кода в двоичный код, содержащий регистр тетрады, блок управления, вход которого является входом признака десятичной мантиссы преобразователя, распределитель импульсов, регистр адреса, первый блок памяти, блок умножения, двоичный сумматор, регистр сдвига, причем первый выход блока управления соединен с входом распределителя импульсов, первый выход которого соединен с тактовым входом регистра адреса, управляющий вход которого подключен ко второму выходу блока управления, второй выход распределителя импульсов соединен с управляюндим входом первого блока памяти, адресный вход которого подключен к первому выходу регистра адреса, выход регистра тетрады соединен с первым входом блока умножения, выход которого подключен к первому входу двоичного сумматора, выход двоичного сумматора соединен с входом регистра сдвига, выход старшего разряда которого соединен со вторым входом двоичного сумматора, первая группа выходов регистра сдвига является группой выходов мантиссы преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей, заключающегося в обеспечении возможности преобразования чисел в форме с плавающей занятой, в него введены второй блок памяти, регистр двоичного порядка, элемент И, первый и второй коммутаторы, дополнительный регистр, элемент ИЛИ, группа элементов ИЛИ, вход блока управления подключен к первому входу элемента И и к управляющим входам первого и второго коммутаторов, второй выход распределителя импульсов соединен с тактовым входом первого коммутатора, третий выход распределителя импульсов соединен с управляющим входом второго блока памяти, с вторым входом элемента И и тактовым 21

15

20

10

Jf 5

13

17

22

П

18

13 ВХОДОМ второго коммутатора, второй выход регистра адреса подключен к адресному входу второго блока памяти, выход первого блока памяти и первый выход второго блока памяти через элемент ИЛИ соединены ,со вторым входом блока умножения, второй выход второго блока памяти соединен со входом регистра двоичного порядка, выходы которого являются выходами порядка преобразователя, выход старшего разряда регистра сдвига подключен к третьему входу элемента И, выход которого соединен с управляющим входом дополнительного регистра, вторая группа выходов регистра сдвига подключена к группе входов первого коммутатора, выходы которого соединены с информационными входами дополнительного регистра, выход которого соединен с информациокньия входом второго коммутатора, выход второго коммутатора через группу элементов ИЛИ, вторые входы которых подключены к информационным входам преобразователя, соединен со входом регистра тетрады. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 473179, кл. G 06 F 5/02, 1975. 2.Авторское свидетельство СССР по заявке № 2171542, кл. G 06 F 5/02, 1975 (прототип).

,111110 011111 11011111 1011 /77 /2

Фиг.if

Авторы

Даты

1981-02-28—Публикация

1979-01-04—Подача