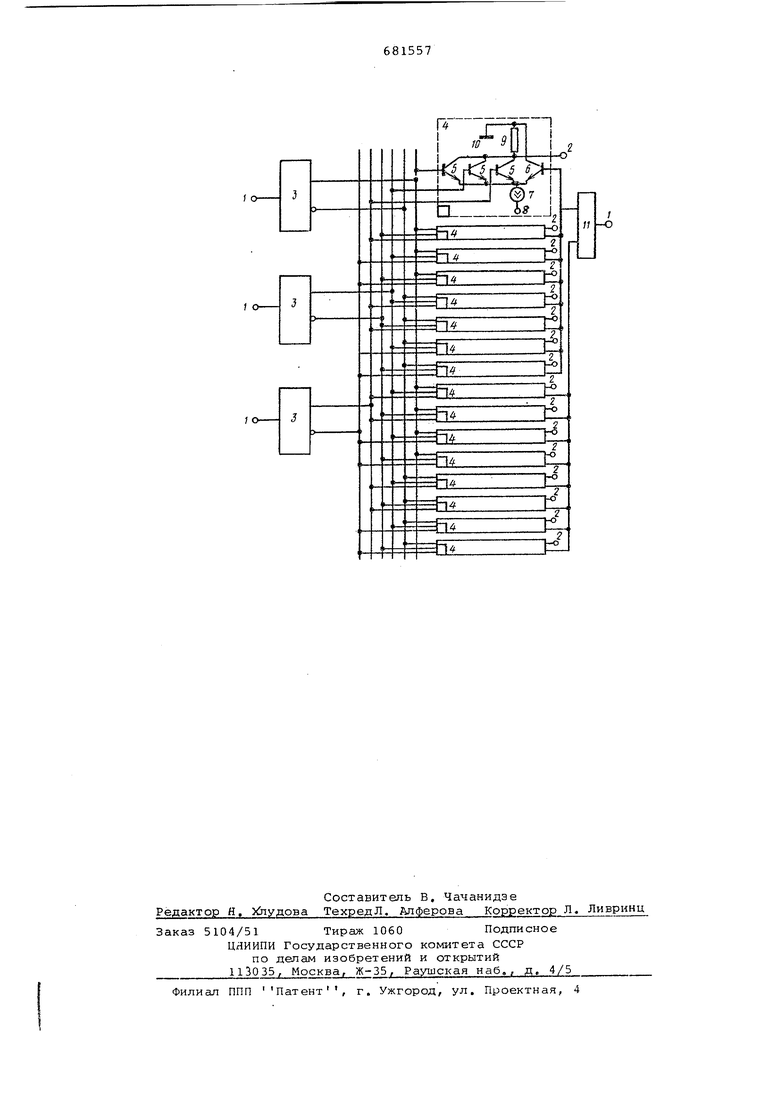

Изобретение относится к автомати ке и вычислительной технике. Известны дешифраторы, содержащие входные каскаду, имеющие по К входо и 2 выходов, и оконечные каскады, каждый из которых содержит переключательные и дополнительный транзист ры, эмиттеры которых объединенной че рез генератор тока подключены к г-мнусовой шине питания, а коллекторы переключательных транзисторов через резистор соединены с земляной шиной и коллектором дополнительного транзистора 1 . К недостаткам такого устройства относится низкое быстродействие. Лаибопее близким к предлагаемому является дешифратор, содержащий Р входных шин и М-2 выходных шин, а также N входных каскадов, имеющих по к входов, соединенных с входными шинами, и 2 выходов, М оконечных кас кадов, каждый из которых содержит N переключательных и дополнительный транзисторы, причем в каждом оконеч ном каскаде эмиттеры переключательных и дополнительного транзисторов объединены и через генератор тока по ключены к минусовой шине источника питания, а коллекторы переключательных транзисторов объединены и непосредственно соединены с соответствующей выходной шиной, а через резистор подключены к коллектору дополнительного транзистора и земляной шине, базы переютючательных транзисторов кшкдого оконечного каскадаПодключены к выходам соответствующих входных каскадов 2. К недостаткам этого,устройства относится низкое быстродействие. Цепью изобретения является повышение быстродействия дешифратора. Это достигается за счет того, что в дешифратор, содержащий Р входных шин и М-2 выходных шин, а также N входных каскадов, .имеющих по К входов, соединенных с входными шинами, и 2 выходов, М оконечных каскадов, каждый из которых содержит N переключательных и допо-пнительный транзнсторы причем в каждом оконечном каскаде эмиттеры переключ-ательных и дополнительного транзисторов объединены и через генератор тока подключены к минусовой шине источника Ш-1ТШ.ШЯ, а ко;шекторы переключательных транзисторов объединены и непосредственно соединены с соответствующей выходной шиной , а через реяистор подключены к коллектору дополнительного транзистора и земляной шине, базы переключательных транзисторов каждого оконечного каскада подключены к выходам соответствующих входных каскадов, введен дополнитель ный входной каскад с (P-KN)1 входами, подключенными к входным шинам, Р -k N и 2выходами, | аждый из которых соединен с базаМи дополнительных транзисторов М/2 оконечных каскадов. Ла чертеже представлена функциональная схема дешифратора. Она содержит входные шины 1, выходные шины 2, входные каскады 3, входы которых соединены с входными шинами 1, оконечные каскады 4, каждый из которых содержит переключа тельные 5 и дополнительный б транзисторы, эмиттеры которых объединены и через генератор 7 тока подключ ны к минусовой шине 8 источника пит ния, резистор 9, включенный между объединенными коллекторами переключательных транзисторов 5 и коллекто ром дополнительного транзистора б, который также подключен к зелотяной шине 10; дополнительный входной кас кад 11, входы которого соединены с входными шинами 1, а каждый из его выходов подключен к базам дополнительных транзисторов б соответствую щих оконечных каскадов 4, Базы пере ключательных транзисторов 5 ка кдого оконечного каскада 4 подключены к выходам соответствующих входных кас кадов 3, а точка объединения коллек торов переключательных транзисторов 5 и резистора 9 соединен с соответ ствующей выходной шиной 2, Функционирование дешифратора осу ществляется следующим образом. При подаче любой комбинации входных сиг налов по входным шинам 1 только в одном из всех оконечных каскадов 4 в каждой группе, образованных выходами дополнительного входного каска да 11, на базах всех переключательных транзисторов 5 прикладывбиотся 74 нулевые логические уровни. При зтом единичный логический уровень подается на базу дополнительного транзистора б только одного оконечного каскада 4, В силу соотношения напряжений логических уровней единичный логический уровень оказывается на выходе только одного оконечного каскада 4, в котором ток от генератора 7 тока переключает дополнительный транзистор б. Формула изобретения Дешифратор, содержащий Р входных шин и М-2 выходных шин, а также N входных каскадов,имеющих по К входов, соединенных с входными шинами, и 2 выходов, М оконечных каскадов, каждый из которых содержит N переключательных и дополнительный транзисторы, причем в каждом оконечном каскаде эмиттеры переключательных и дополнительного транзисторов объединены и через генератор тока подключены к минусовой шине источника питания, а коллекторы переключательных транзисторов объединены и непосредственно соединены с соответствующей выходной шиной, а через резистор подключены к коллектору дополнительного транзистора и земляной шине, базы переключательных транзисторов каждого оконечного каскада подключены к выходам соответствующих входных каскадов, отличающийся тем, что, с целью повышения быстродействия, в него введен дополнительный входной каскад с (P-KN) 1 входами, подключенными к входным шинам, и 2 выходами, каждый из которых соединен с базами дополнительных транзисторов М/2 , оконечных каскадов. Источники информации, принятые во внимание при экспертизе 1,Патент Франции № 2144308, кл, G 06 F 9/00, 10.06.74, 2,Патент США № 3624620, кп. 340-173, 15,05,75.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор запоминаюшего устройства | 1979 |

|

SU871330A1 |

| Усилитель | 1982 |

|

SU1084955A1 |

| Интегральная логическая схема | 1979 |

|

SU860314A1 |

| Устройство для преобразования входного двоичного сигнала в телеграфный сигнал | 1983 |

|

SU1125765A1 |

| Усилитель мощности | 1983 |

|

SU1123092A1 |

| Стабилизированный источник питания | 1986 |

|

SU1334128A2 |

| Следящий многоустойчивый компаратор напряжений | 1974 |

|

SU660226A1 |

| Цифровая полупроводниковая интегральная схема с тремя состояниями на выходе | 1980 |

|

SU900454A1 |

| Стабилизатор переключательного типа | 1981 |

|

SU945854A1 |

| Операционный усилитель | 1989 |

|

SU1721614A1 |

Авторы

Даты

1979-08-25—Публикация

1977-01-06—Подача