(54) ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1986 |

|

SU1383507A1 |

| Дешифратор | 1986 |

|

SU1336251A1 |

| Мультиплексор | 1986 |

|

SU1378048A1 |

| Формирователь сигнала выборки шины матрицы накопителя | 1981 |

|

SU1027824A1 |

| Логический элемент | 1985 |

|

SU1285589A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| Формирователь сигнала для выборки элементов матрицы | 1982 |

|

SU1045364A1 |

| Триггерный логический элемент И/И-НЕ | 2022 |

|

RU2789166C1 |

| Логический переключающийэлЕМЕНТ | 1979 |

|

SU849489A1 |

| Устройство емкостной гальванической развязки | 1986 |

|

SU1370767A1 |

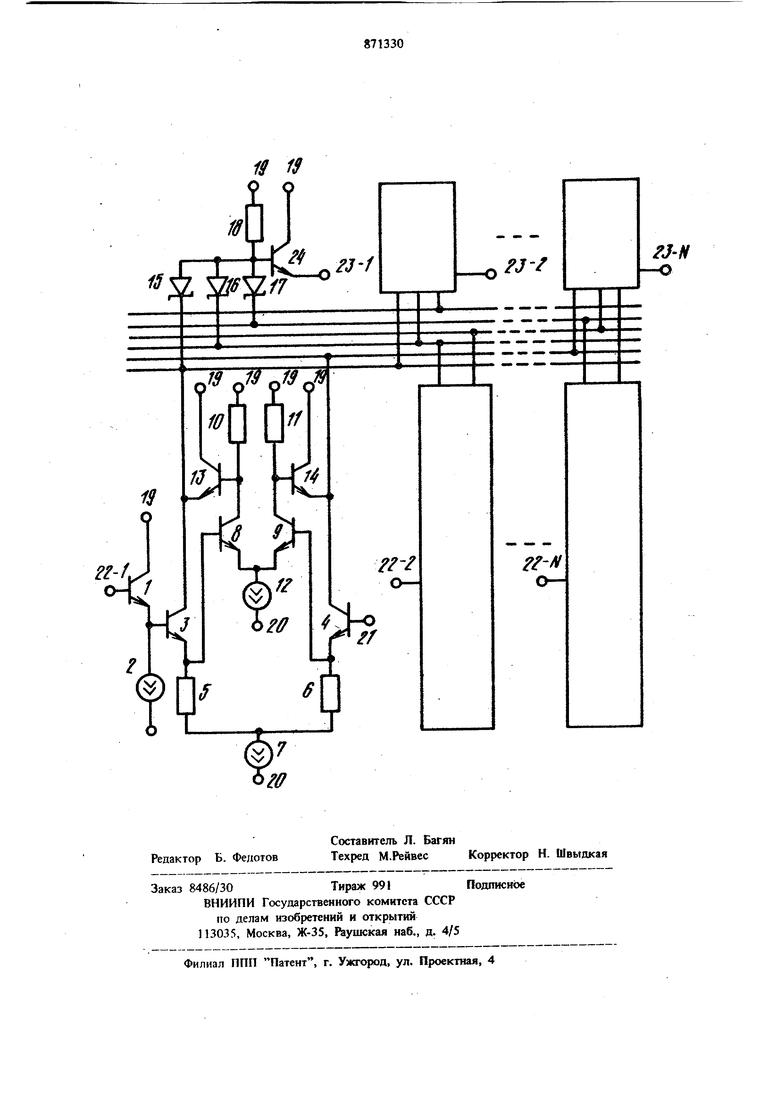

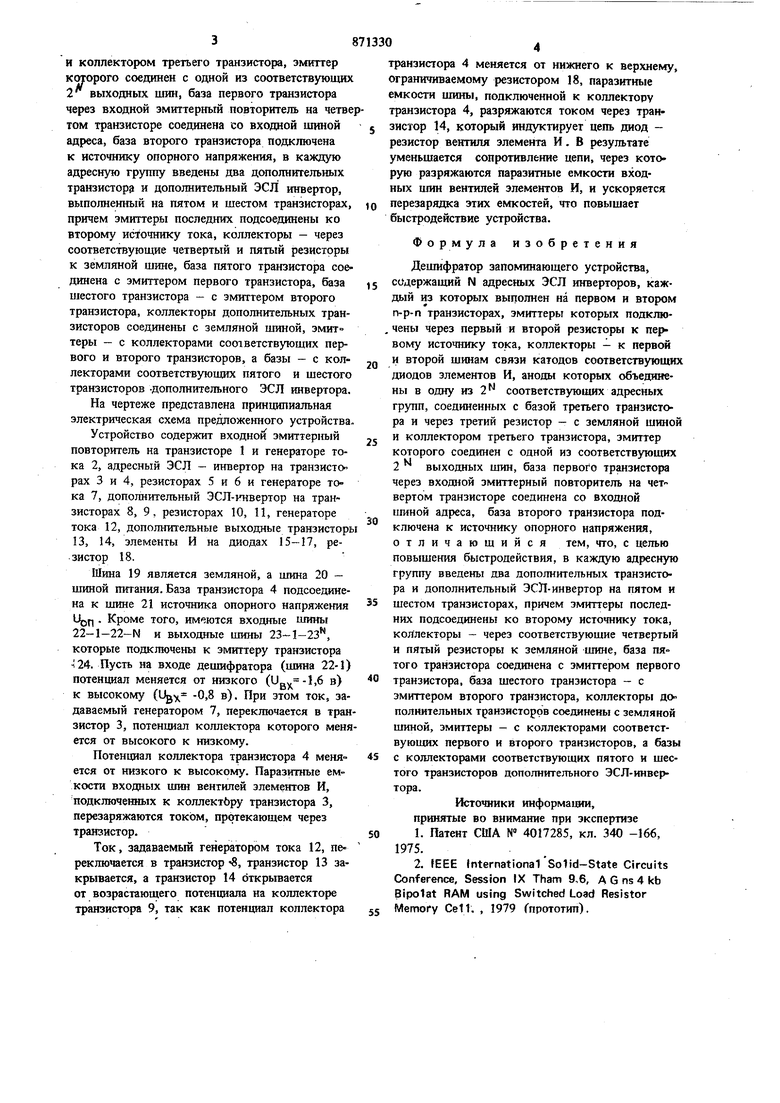

Изобретение относится к вычисгагтельной тех нике, в частности к дшгафраторам, и может быть использовано в определенных зааомтаавших устройствах шифровых вычислительных машин, в частности, в гаггегральном испош1ении {Ьвестж дешифратор ЗУ, содержащий N входщых адресных ЭОЛ инверторов и 2 элементе И на диодах Шотткн, анода которых подключены к нагрузочным резисторам, а катоды - к соответствуюиот выходам 1. Однако быстродействие этото устройства относительно невысоко. Наиболее близок к предлагаемому дешифратор, запснъшнающего устройства, содержащий N адресных ЭСЛ ииверторсш, каждый из которых выполнен на первом k атор(л п-р-п транзисторах, эмиттеры которых подключены через первый и второй резисторы к первенцу источнику тока, коллектсфы - к первой и второй связи катодов соответствующих диодов элементов И, аноды которых с ъещшшы в одну из 2 соответствующих ащтесных групп, соеднненных с базой третьего транзистора и через третий резистор - с земляной шиной и коллектором третьего транзистора, эмиттер которого соедашен с одной из соответствующих 2 выходных шин, база первого транзистора через входной эмиттерный повторитель на четвертом транзисторе соединена со второй шиной адреса, база второго транзистора подключена к опорного напряжения 2. Одаако и у этот-о устройства быстродействие невысоко, так как паразитные емкости входных шин элементов И перезаряжаются током, протекающим через вентили элементов И. Целью изобретения является повышение быстродействия. Дш1 этого в дешифраторе эапомт1ающето ус1ройства, содержащем N адресных ЭСЛ ffitBepTopoB, каждый из которых выполнен на первом и втором п-р-п транзисторах, эмиттеры которых подключены через первый и второй резисторы к первому источнику тока, коллекторы - к первой и второй шинам связи катодов соответствующих диодов элементов И, аноды которых, объединены в одну из 2 соответствующих адресных групп, соединенных с базЫ третьего транзистора и через третий резистор - с земляной шиной И коллектором третьего транзистора, эмиттер которого соединен с одной из соответствующих 2 выходных шин, база первого транзистора через входной эмиттерный повторитель на четве том транзисторе соединена со входной шиной адреса, база второго транзистора подключена к источнику опорного напряжения, в каждую адресную группу введены два дополнительных транзистора и дополнительный ЭСЛ инвертор, выполненный на пятом и шестом транзисторах, причем змиттеры последних подсоединены ко второму Hcio4HHKy тока, коллекторы - через соответствующие четвертый и пятый резисторы к земляной шине, база пятого транзистора соединена с эмиттером первого транзистора, база шестого транзистора - с эмиттером второго транзистора, коллекторы дополнительных транзисторов соединены с земляной шиной, эмит теры - с коллекторалта соответствующих первого и второго транзисторов, а базы - с коллекторами соответствующих пятого и шестого транзисторов -дополнительного ЭСЛ инвертора. На чертеже представлена принципиальная электрическая схема предложенного устройства Устройство содержит входной эмиттерный повторитель на транзисторе 1 и генераторе тока 2, адресный ЭСЛ - инвертор на транзистО pax 3 и 4, резисторах 5 и 6 и генераторе тока 7, дополнительный ЭСЛ-инвертор на транзисторах 8, 9, резисторах 10, 11, генераторе тока 12, дополнительные выходные транзисторы 13, 14, элементы И на диодах 15-17, резистор 18. Шина 19 является земляной, а щина 20 - шиной питания. База транзистора 4 подсоединена к шине 21 источника опорного напряже шя JQ , Кроме того, имеются входные шины 22-1-22-N и выходные шины 23-1-23, которые подключены к эмиттеру транзистора i24. Пусть на входе дешифратора (шина 22-1) потенциал меняется от низкого (,6 в) к высокому (Ugx -0,8 в). При этом ток, задаваемый генератором 7, переключается в тран зистор 3, потенциал коллектора которого меня ется от высокого к низкому. Потенциал коллектора транзистора 4 меняется от низкого к высокому. Паразитные емкости входных шин вентилей элементов И, подключенных к коллектЬру транзистора 3, перезаряжаются током, протекающем через транзистор. Ток, задаваемый генератором тока 12, переключается в транзистор -8, транзистор 13 закрывается, а транзистор 14 открывается от возрастающего потенциала на коллекторе транзистора 9, так как потенциал коллектора ранзистора 4 меняется от нижнего к верхнему, граничиваемому резистором 18, паразитные мкости шины, подключенной к коллектору ранзистора 4, разряжаются током через транистор 14, который индуктирует цепь диод езистор вентиля элемента И. В результате меньшается сопротивление цепи, через котоую разряжаются паразитные емкости входых шин вентилей элементов И, и ускоряется перезарядка этих емкостей, что повышает быстродействие устройства. Формула изобретения Дешифратор запоминающего устройства, содержащий N адресных ЭСЛ инверторов, каждый из которых выполнен на первом и втором п-р-п транзисторах, эмиттеры которых подключены через первый и второй резисторы к пе{ вому источнику тока, коллекторы - к первой и второй шинам связи катодов соответствующих диодов элементов И, аноды которых объединены в одну из 2 соответствующих адресных групп, соединенных с базой третьего транзистора и через третий резистор - с земляной шиной и коллектором третьего транзистора, эмиттер которого соединен с одной из соответствующих 2 выходных шин, база первого транзистора через входной эмиттерный повторитель на чет вертом транзисторе соединена со входной шиной адреса, база второго транзистора подключена к источнику опорного напряжения, отличающийся тем, что, с целью повышения быстродействия, в каждую адресную группу введены два дополнительных транзистора и дополнительный ЭСЛ-инвертор на пятом и шестом транзисторах, причем эмиттеры последних подсоединены ко второму источнику тока, коллекторы - через соответствующие четвертый и пятый резисторы к земляной шине, база пятого транзистора соединена с эмиттером первого транзистора, база шестого транзистора - с эмиттером второго транзистора, коллекторы до полнительных транзисторов соединены с эемляной шиной, эмиттеры - с коллекторами соответствующих первого и второго транзисторов, а базы с коллекторами соответствующих пятого и шестого транзисторов дополнителънси-о ЭСЛ-инвертора. Источники информации, принятые во внимание при экспертизе 1.Патент США N 4017285, кл. 340 -166, 1975. 2.fEEE InternationalSolid-State Circuits Conference, Session IX Them 9,6, A G ns 4 kb Bipolat RAM using Switched Load Resistor Memory Cell. , 1979 (прототип).

Авторы

Даты

1981-10-07—Публикация

1979-10-01—Подача