(54) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1980 |

|

SU1099317A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| АППРОКСИМАТОР МОНОТОННЫХ ФУНКЦИЙ | 1991 |

|

RU2023296C1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1088008A1 |

| ПРЕОБРАЗОВАТЕЛЬ КУСОЧНО-ЛИНЕЙНЫХ ФУНКЦИЙ | 1970 |

|

SU275548A1 |

| Вичислительное устройство | 1979 |

|

SU783804A1 |

| АППРОКСИМАТОР МОНОТОННЫХ ФУНКЦИЙ | 1991 |

|

RU2023297C1 |

| Кусочно-линейный функциональный преобразователь | 1977 |

|

SU658566A1 |

| АППРОКСИМАТОР МОНОТОННЫХ ФУНКЦИЙ | 1991 |

|

RU2018947C1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

Изобретение относится к вычислительйой технике и,может быть использовано в автоматике, телемеханике и информационно-измерительной технике. Известен функциональный прео азователь tlji содержащий два блока памяти, генератор импульсов, дополнительный генератор импульсов, два генератора ступен чатого напряжения, блок выделения време ного интервала, матрицу совпадений и мно гозвенный потенциальный элемент. Недостатками преобразователя являютс сложность и вследствие этого недостато ная надежность, недостаточное быстродействие, а также то, что участки воспроизводимой кусочно-линейной функции могут быть только положительными углами наклона. Наиболее близким технической сущности к изобретению является .функциональный преобразователь ,2., содержащий регистр, группа выходов которого через дешифратор соединена с группой входов управляемого делителя частоты, блок ан лиза кода на нуль, выход которого соединен с первым входом триггера, второй вход которого соединен со входом пуск преобразователя, а выход - с первым входом элемента И, второй вход которого соединен с выходом генератора импуль сов, а выход - с входом управляемого делителя частоты, блоки перезаписи, причем группа входов первого блока перезаписи является группой входов прео азователя, а группа выходов соединена с грутгасЛ входе регистра. Недостатками этого преобразователя, являются недостаточное быстродействие, то, что участки воспроизводимой кусочно-линейной функции могут быть только с положительными углами наклона и то, что функция представляется в виде временного интервала, что сужает область применения. Целью изобретения является повыше ие быстродействия и расширение функ ииональных возможностей за счет получения функции с отрицательными углами наклона. Поставленная цель достигается тем, что в предложенный преобразователь введены реверсивный счетчик,блок формирования начального кода, вычитающий блок вычитающий счетчик Первый и второй выходы управляемого делителя частоты соедине.ны соответственно с входами сложение и вычитание реверсивного счетчика, группа входов которого соединена с группой выходов второго блока перезаписи, а группа выходов является группой выходов преобразователя. Первая и вторая группы выходов и группа входов блока формирования начального кода соединены соответственно с группой входов второго, блока перезаписи, первой группой входов вычитающего блока и группой выходов дешифратора, группа входов которого соединена со второй группой входов вычитающего блока, группа выходов которого соединена с группой входов третье его блока перезаписи, группа выходов которого соединена с группой входов вычитающего счетчика, группа выходов кото« рого соединена с группой входов блока анализа кода на нуль. Третий и четвер тый выходы управляемого делителя частоты соединены соответственно с управляющими входами второго и третьего блока перезаписи и входом вычитающего счетчика.

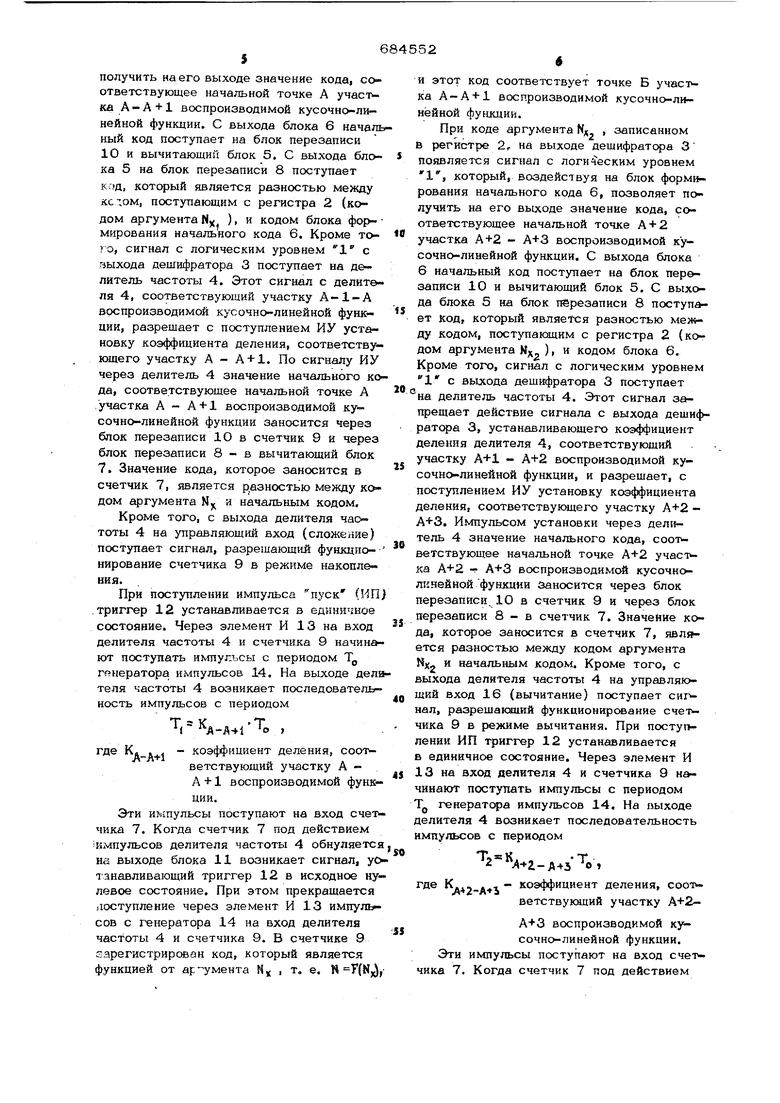

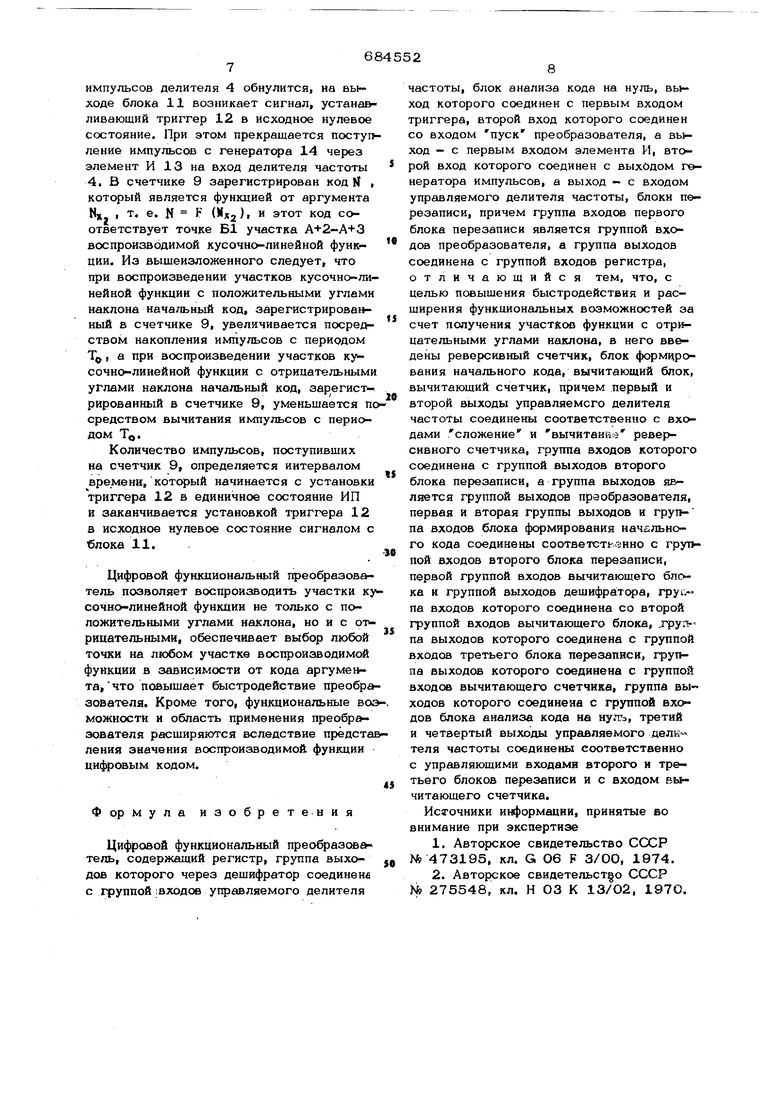

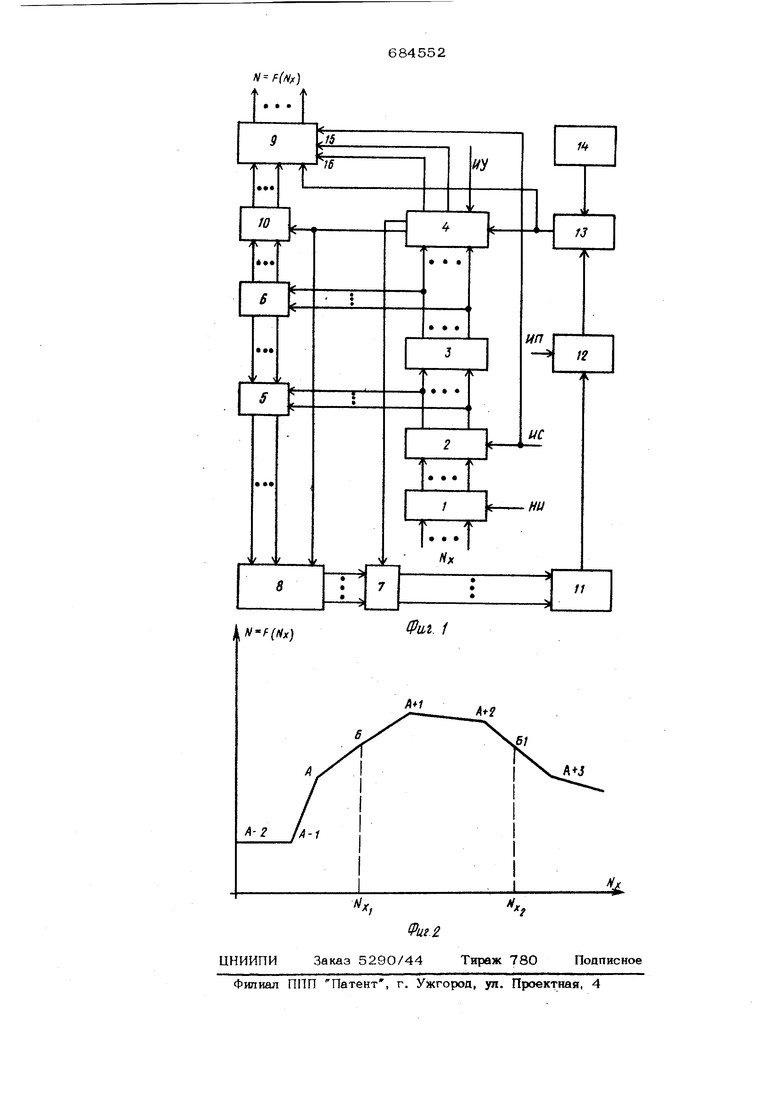

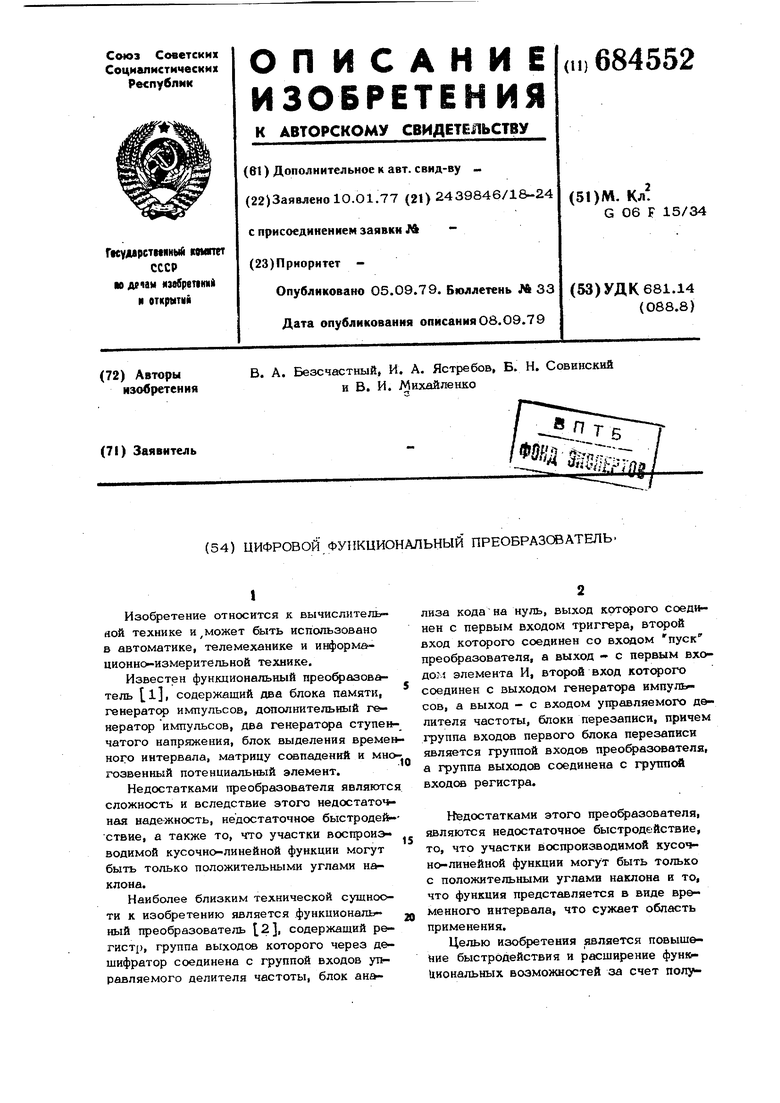

На фиг. 1 дана структурная схема функционального преобразователя; на фиг. 2 - пример воспроизводимой кусочно-линейной функции.

Цифровой функциональный преобразователь содержит первый блок перезаписи 1, регистр 2, дешифратор 3, управляемый делитель частоты 4, вычитающий блок 5, блок формирования начального кода 6, вычитающий счетчик 7, третий блок перезаписи 8, реверсивный счетчик 9, второй блок перезаписи 10, блок анализа кодов на нуль 11, триггер 12, элемент И 13 и генератор импульсов 14,

Реверсивный счетчик 9 имеет вход 15 сложения и вход 16 вычитания. Выходы делителя частоты 4 соединены $д с счетчиком 9, блоками перезаписи 10 и 8 и счетчиком 7. Первые выходы блока формирования начального кода 6 через блок перезаписи10 соединены со счетчиком 9, вторые выходы через вь|читающий sj блок 5, блок перезаписи 8 и вычитающий счетчик 7 - с блоком 11, а выходы - с выходами дешифратора 3, входы которого

интервалом времени, который определяется переходными процессами в регистре 2, на блок 1 поступает начальный импу.тьс (НИ, который записывает в регистр 1 код аргумента Ny .С регистра 2 код аргумента поступает на вычитающий блок 5 и дещифратор 3.

Дешифратор 3 представляет собой ндбор логически; ; устройств, которые определяют заданный коэффициент деления д&лителя частоты 4 а зависимости от кода аргумента Ц , соответствующего опреде ленному участку воспроизводимой кзсочно-линейной функции. Эти логические усг ройства выдают сигнал, например, в ииде логической 1 при коде, равном или определенного значения кода та, а при коде, меньшем, чем это значе ние кода аргумента - сигнал с логичео кйм уровнем О.

С выхода дешифратора 3 сигналы, например, в виде логического уровня поступают на делитель частоты 4, который представляет собой двоичный счетчик с запоминающими; и логическими элемекнтами, для установки заданного коэффици- анта деления с поступлением импульса установки (ИУ) и блок формирования начального кода 6, который, в свою очеред1, выдает значение начального коде, соот ветствующее определенному заданному участку воспроизводимой кусочно-линейной функции. Значение начальвого кода с соединены с вычитающим блоком 5 и регистром 2. Входы регистра 2 подключены к блоку перезаписи 1 и счетчику 9, один из входов которого соединен со входом делителя частоты 4 и элементом И 13, первый вход которого соединен с генератором импульсов 14, а второй через триггер 12 - с блоком 11, Входным узлом преобразователя является регистр 2, на который через блок перезаписи 1 записывается код аргуме таМ. . Цикл преобразования начинается с приходом импульса исходного состояния (ИС), который устанавливает регистр 2 и счесчик 9 в исходное нулевое состояние. С блока 6 поступает на счетчик импульсов 9 и блок 5.о Допустим, что в регистр 2 записан код аргументаNV. , срответствукяций участ ку А-А + 1 воспроизводимой кусочно-лн ней ной функции. Тогда иа выходе дешифратора 3 появляется сигнал с логическим уровнем I, котфый, воздействуя на блок формирования начального кода 6, позволяет получить наего выходе значение кода| соответствующее начальной точке А участ ка А - А +1 воспроизводимой кусочно-линейной функции. С выхода блока 6 началь ный код поступает на блок перезаписи 10 и вычитающий блок 5. С выхода блока 5 на блок перезаписи 8 поступает код, который 5шляется разностью между KCZOM, поступающим с регистра 2 (кодом аргумента Nj ), и кодом блока фор- мирования начального кода 6. Кроме того, сигнал с логическим уровнем 1 с выхода дешифратора 3 поступает на д&литель частоты 4. Этот сигнал с делителя 4, соответствующий участку А-1 -А воспроизводимой кусочно-линейной функции, разрешает с поступлением ИУ установку коэффициента деления, соответству ющего участку А - А + 1. По сигналу ИУ через делитель 4 значение начального ко да, соответствующее начальной точке А /участка А - А + 1 воспроизводимой кусочно-линейной функции заносится через блок перезаписи 1О в счетчик 9 и через блок перезаписи 8 - в вычитающий блок 7. Значение кода, которое заносится в счетчик 7, является разностью между кодом аргумента N и начальным кодом. Кроме того, с выхода делителя частоты 4 на управляющий вход (сложение) поступает сигнал, разрешающий фушсционирование счетчика 9 в режиме накопления. При поступлении импульса пуск (ИП .триггер 12 устанавливается в единичное состояние. Через элемент И 13 на вход делителя частоты 4 и счетчика 9 начинают поступать и тулъсы с периодом Т гянератора импульсов 14, На выходе дели теля частоты 4 возникает последовательность импульсов с периодом 1/ X ( А-А-И о - коэффициент деления, соответствующий участку А А+1 воспроизводимой функции. Зти импульсы поступают на вход счет чика 7. Когда счетчик 7 под действием импульсов делителя частоты 4 обнуляется на выходе блока 11 возникает сигнал, уо танавливающий триггер 12 в исходное нулевое состояние. При этом прекращается лоступление через элемент И 13 импульсов с генератора 14 на вход делителя частоты 4 и счетчика 9. В счетчике 9 зарегистрирован код, который является функцией от аргумента Н т, е. Н F(K и этот код соответствует точке Б участ ка А-А + 1 воспроизводимой кусочно-линейной функции. При коде аргумента N;, , записанном в регистре 2, на выходе дешифратора 3 появляется сигнал с логиГеским уровнем , который, воздействуя на блок формирования начального кода 6, позволяет получить на его выходе значение кода, соответствующее начальной точке А + 2 участка А+2 - А+3 воспроизводимой кусочно-линейной функции. С выхода блока 6 начальный код поступает на блок перезаписи 10 и вычитающий блок 5. С выхода блока 5 на блок перезаписи 8 поступает Код, который является разностью между кодом, поступакщим с регистра 2 (кодом аргумента N. ), и кодом блока 6. Кроме того, сигнал с логическим уровнем 1 с выхода дешифратора 3 поступает на делитель частоты 4. Этот сигнал запрещает действие сигнала с выхода дешифратора 3, устанавливающего коэффициент деления делителя 4, соответствующий участку А+1 - А+2 воспроизводимой кусочно-линейной функции, и разрешает, с поступлением ИУ установку коэффициента деления, соответствующего участку А+2 А+3. Импульсом установки через делитель 4 значение начального кода, соот ветствующее начальной точке А+2 участ ка А+2 А+3 воспроизводимой кусочнолинейнойфункции Заносится через блок перезаписи, 10 в счетчик 9 и через блок перезаписи 8 - в счетчик 7. Значение кода, которое заносится в счетчик 7, является разностью между кодом аргумента NX- и начальным кодом. Кроме того, с выхода делителя частоты 4 на управляющий вход 16 (вычитание) поступает сигнал, разрешаюший функционирование счетчика 9 в режиме вычитания. При постугнлении ИП триггер 12 устанавливается в единичное состояние. Через элемент И 13 на вход делителя 4 и счетчика 9 начинают поступать импульсы с периодом Т генератс а импульсов 14. На выходе делителя 4 возникает последовательность импульсов с периодом 2««л- 2-мз 0 где Кд.., - коэффициент деления, соот ветствующий участку А+2- А+3 воспроизводимой кусочно-линейной функции. Эти импульсы поступают на вход счерчика 7. Когда счетчик 7 под действием импульсов делителя 4 обнулится, на выходе блока 11 возникает сигнал, устанав ливающий триггер 12 в исходное нулевое состояние. При этом прекращается посту№ ление импульсов с reHepaTqpa 14 через элемент И 13 на вход делителя частоты 4. В счетчике 9 зарегистрирован код | , который является функцией от аргумента HX , т. е. N F (М)(2)г и этот код соответствует точке Б1 участка А+2-А+3 воспроизводимой кусочно-линейной функции. Из выщеизложенного следует, что при воспроизведении участков кусочно-линейной функции с положительными углами наклона начальный код, зарегистрирова ный в счетчике 9, увеличивается посредством накопления импульсов с периодом Т, а при воспроизведении участков ку сочно-линейной функции с отрицательными углами наклона начальный код, зарегистрированный в счетчике 9, уменьшается по средством вычитания импульсов с периодом TO. Количество импульсов, поступивших на счетчик 9, определяется интервалом времени, который начинается с установки триггера 12 в единичное состояние ИП и заканчивается установкой триггера 12 а исходное нулевое состояние сигналом с блока 11. Цифровой функциональный преофазов тель позволяет воспроизводить участки ку сочно-линейной функции не только с положительными углами наклона, но и с от рицательными, обеспечивает выбор любой точки на любом участке воспроизводимой функции в зависимости от кода аргумента, что повышает &1стродействие преобра зователя. Кроме того, функциональные воэ можности и область применения преобр зователя расширяются вследствие предста ления значения воспроизводимой функции цифровым кодом. Формула изобретения Цифровой функциональный преобразователь, содержащий регистр, группа выходов которого через дешифратор соединена с группой;входов управляемого делителя частоты, блок анализа кода на нуль, выход которого соединен с первым входом триггера, второй вход которого соединен со входом пуск преобразователя, а вь ход - с первым входом элемента И, второй вход которого соединен с выходом генератора импульсов, а выход - с входом управляемого делителя частоты, блоки перезаписи, причем группа входов первого блока перезаписи является группой входов преобразователя, а группа выходов соединена с группой входов регистра, отличающийся тем, что, с целью повышения быстродействия и расширения функциональных возможностей за счет получения участков функции с отрицательными углами наклона, в него введены реверсивный счетчик, блок формирования начального кода, вычитающий блок, вычитающий счетчик, причем первый и второй выходы управляемого делителя частоты соединены соответственно с входами сложение и вычитание реверсивного счетчика, группа входов которого соединена с группой выходов второго блока перезаписи, а группа выходов является группой выходов преобразователя, первая и вторая группы выходов и группа входов блока формирования начйльного кода соединены соответстьэнно с группой входов второго блока перезаписи, первой группой входов вычитающего блока к группой выходов дeшифpaтqpa, груг па входов которого соединена со второй группой входов вычитающего блока, .груп-па выходов которого соединена с группой входов третьего блока перезаписи, грутьпа выходов которого соединена с группой входов вычитающего счетчика, группа выходов которого соединена с группой входов блока анализа кода на , третий и четвертый выходы управляемого делк теля частоты соединены соответственно с управляющими входами второго и третьего блоков перезаписи и с входом вычитающего счетчика. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 473195, кл. G 06 F 3/00, 1974. 2.Авторское свидетельство СССР N9 275548, кл. Н 03 К 13/О2, 197О.

(,)

1-1

()

A- 2 /A-1

Фиг. 1

Авторы

Даты

1979-09-05—Публикация

1977-01-10—Подача