1

Изобретение относится к радиотехнике и может использоваться в информационно-измерительных системах различного назначения.

Известен цифровой умножитель частоты, содержащий последовательно соединенные формирователь импульсов, блок управления, аеръыя вентиль, первый делитель частоты, выход которого подключен к второму входу блока управления, первый регистр памяти, первую схему переноса, второй делитель частоты и элемент И, к выходу которого, являющегося выходом цифрового умножителя частоты, поД1О1ючен через элемент ИЛИ дфугой вход первой схеМЬ1 переноса, последовательно включенные между выходом первого и другим входом второго делителя частоты второй регистр памяти, дру1Х1Й вход которого соединен с входом второго и выходом первого вентилей, втЬрая схема переноса, другой вход которой соединен с вьиодом элемента И, параллельнь1и сумматор, друго вход которого соединен с вЬ1х;одом третьей схемы переноса, триггер задержки и третий вентиль, а также генератор импуйьсов эталонной частоты, ъыход которого с вторыми

входами триггера задержки, первого и третьего вентилей, при этом выход блока управления соединен с входом третьей схемы переноса, с вторыми входами второго вентиля И элемента ИЛИ и с третьим входом т} етьего вентиля 1. Однако данный умножитель нМеет -невысокую точность умножения.

Цель изобретения - повышение точности умноукеапя.

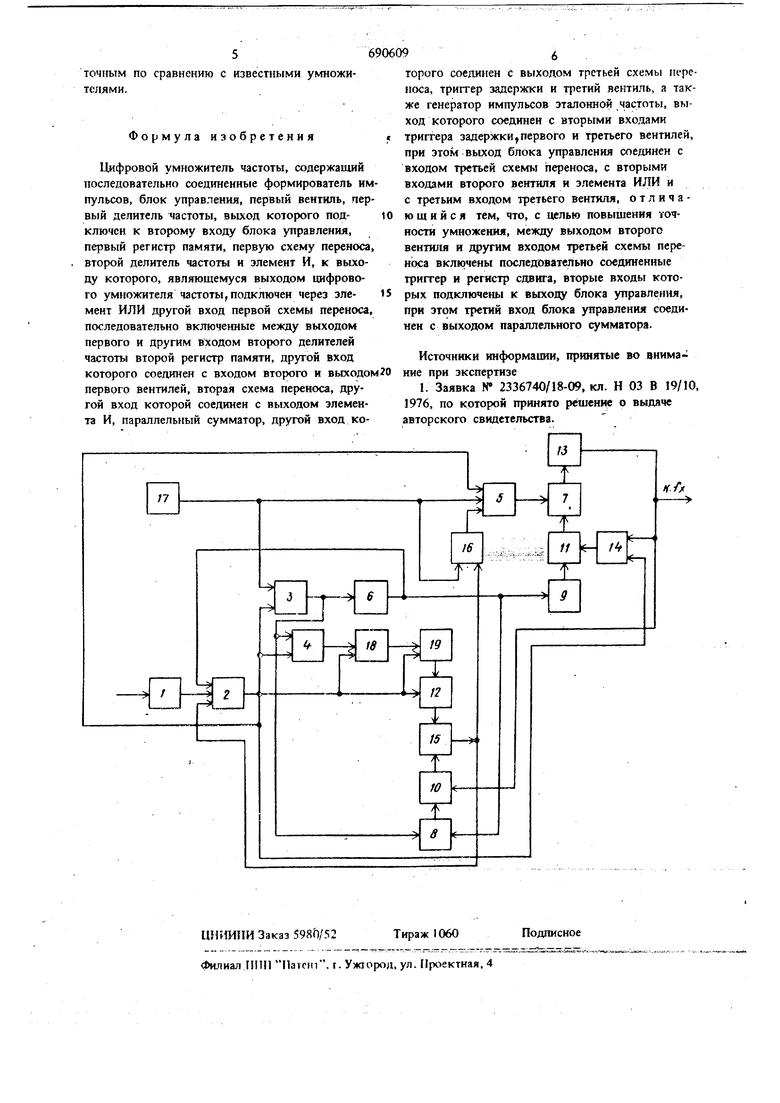

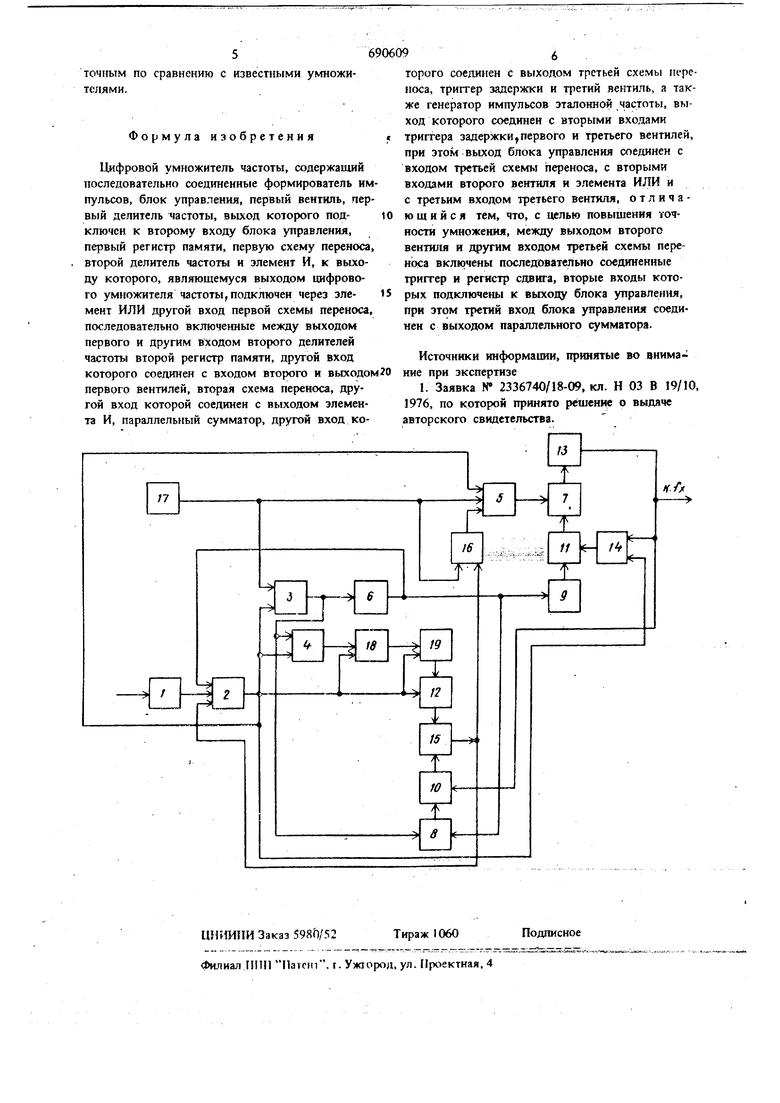

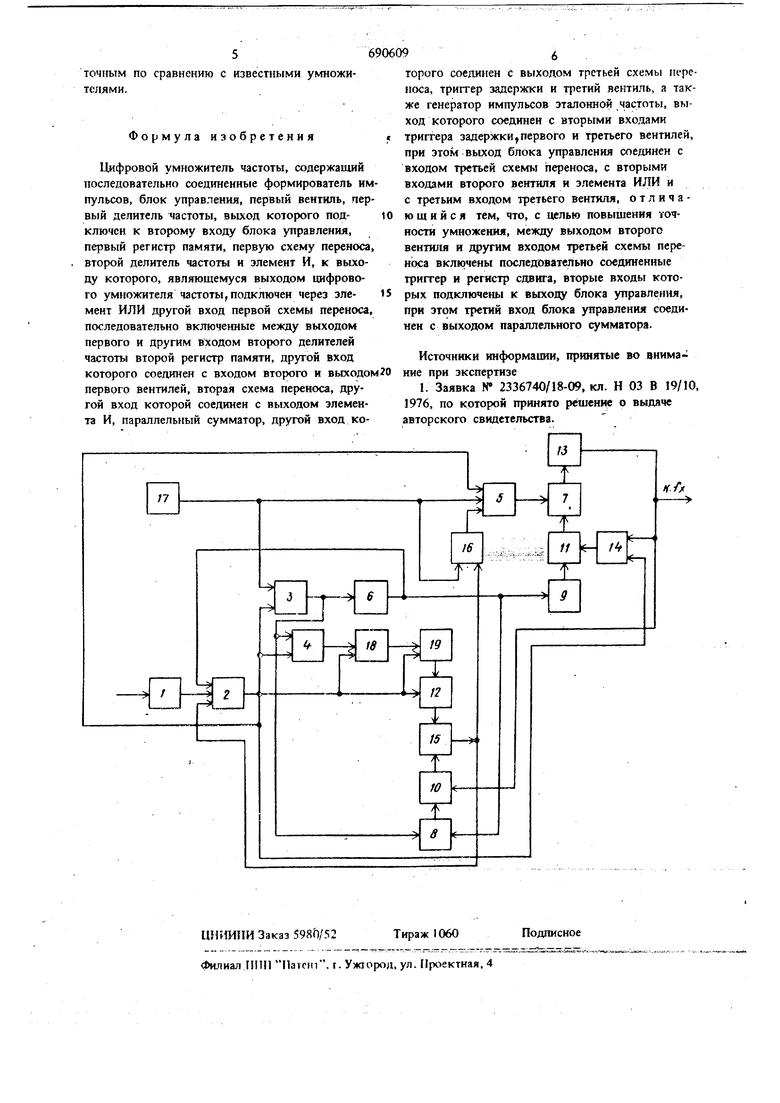

Для этого в цифровом умножнтеле частоты, содержащем последсяателыю соеданенные формирователь Импульсов, блок управления, первый вентиль, первый депитель частоты, выход которого подключен к второму входу блока управления, первый регастр памяти, п%1рбую схему переноси, вторсж делитель частоты и элемент И, к выходу которого, являющемуся вьйсодОм цифрового умножителя частоты,подключен через элемеет ИЛИ другой вход первой схемы переноса, последовательно включенные между выходом первого и другим входом второго делителей частоты второй регистр памяти, другой вход которого соединен с входом второго и выходом первого вентилей, вторая схе3ма переноса, другой вход котороГ соединен с выходом элемента И, плраллслькый сумматор, другой вход когорсго соегшнен с выходом третьей схемы переноса, триггер задержки и третий вентиль, а также генератор импульсов эталонно частоты, выход которого соединен с вторыми входами триггера задержки, первого и третьего вентилей, при этом выход блока управлейия соединен с входом третьей схемы переноса, с вторыми входами второго вентиля и элемента ИЛИ и с третьим входом третьего вентиля, между выходом второго вентиля и Гфугйм входом третьей схемы переноса включе ны последовательно соединенные триггер и регистр сдвига, вторые входы которых подключены к выходу блока управления, при этом тр тий вход блока управления соединен с выходом параллельного сумматора. На чертеже изображена структурная электрическая схема предложенного умножителя. Цифровой умножитель частоты содержит фор мирователь 1 импульсов, блок управления 2, вентили 3, 4, 5, делители 6, 7 частоты, регистры 8, 9 памяти, схемы переноса 10, П, 12, эл мент И 13, элемент ИЛИ 14, параллельный сумматор 15, триггер 16 задержки, генератор 17 иМ пульсов эталонной частоты, триггер 18 и регистр 19 сдвига.: Умножитель работает следующим образом. В исходном состоянии регистры 8,9, 19, дё яители 6, 7, а также триггеры 16 и 18 нахй;у1тся в нулевом состоянии. Все вентили 3, 4, 5 закрыть. Коэффициент деления дёлитейя 6 устанавливаем равным К. При нажатИк кнопки находящейся в блоке уп1эавления 2, пощотавтй вается к работе формирователь 1. При переходеумножаемого сигнала; имеющего частоту f, через нулевое значение, блок упрай ления 2 вырабатывает ситал Vu , что привоД1ГГ к открытию вентилей 3 и 4. ИмпуЛьсЫ с частотой fо начинают noctynaTb в дели1-елЬ 6 и регистры 8 и 19. При поступлении перВ01Ч выходного импульса из делителя 6 на вход блока управления 2, последний вырабатывает сигнал VK;, по которому вентиль 4 закрывается. Таким образом, в регистре 19 зафиксирова .у.... если К - четное число или по число если К - нечетное чисЛо. Следующим импульсом Vt блока управления 2 содержимое регистра 19 переносите в параллельный сумматор 15. За время первого периода Т -.- импульсы с частотой fo поступаTi Г : ют вггферывно как в делитель 6, так и в регистр 8, но с каждым выходным импульсом делителя 6 показания регистра 8 сбрасываются в нуль. В итоге к кош первого периода в нем будет зафиксировано число Лп, накоплен9нос за промежуток времени от моментн последнего Hhixofwoio HMrrvJibca делителя 6 до копна первого периода Tj То же самое число Дп будет зафиксировано и в делителе 6. В регистр 9 поступают выходные импульсы делителя 7 и к концу первого периода в нем будет зафиксировано число По окончании периода Т|; блок управления 2 вырабатывает сигнал Vj, который закрывает . вентиль 3, открывает вентиль 5 и переносит показания регистра 9 в делитель 7, а показания регистра 8 в параллельный сумматор 15. Если ( An) для четного К, или ( - Дл) для нечетного К, записанное в параллельном сумматоре 15 больше нуля, то на его выходе импульса не будет. После второго выходного импульса элемента И 13 операция ввода g в делитель 7 и Дп в параллельный сумматор 15 повторяется. Если число (- - Дп) О, то на выходе параллельного сумматора 15 импульса опять не будет. По Мере увеличения числа выходных импульсОв элемента И 13 МОжет оказаться, что при некотором числе i вейимина (- - 1Дп) станет меньше Нули, что Ирийёдет k появлению импульса на вхОде параллельного сумматора 15, который поступит в блок управления 2. С выхОда последнего на регистр 19 поступает импульс УГП, koTopbiH осуществит сдвиг его показаний и Стордйу старшего разряда (влево) к перепишет информацию с триггера 18 в младший разряд регистра 19. Таким образом, в регистре 19 будет записан код числа К. Следующий импульс УП блока управле1шя 2 перепишет показания регистра 19 в параллельный сумматор 15 и, следовательно, в нем будет записано положительное число (), если К - четное число и ( - 1Дп), если К - нечетное число. Одновременно выходной импульс параллельного сумматора 15 через триггер 16 закрь11вает на некото{К е время вентиль 5, ввиду чего очередной импульс с частотой fo через этот вентиль 5 не пройдет, а осуществит переброс тр„ггера 16 в исходаое состояние, который в Свою очередь вновь откроет вентиль 5. В результате этой операции будет осуществлена коррекция положения выходного импульса умножителя, при этом погрешность не будет превышать TO/2. Предложенный цифровой умножитель частоты имеет максимальную абсолютную сюгрешность смещения То/2,то есть является более

TOMifbiM по сравнению с

известными умножителя ми.

Формула изобретения

Цифровой умножитель частоты, содержащий последовательно соединенные формирователь импульсов, блок управления, первый вентиль, первый делитель частоты, выход которого подключей к второму входу блока управления, первый регистр памяти, первую схему переноса, второй делитель частоты и элемент И, к выходу которого, являющемуся выходом цифрового умножителя частоты, подключен через злемент ИЛИ другой вход первой схемы переноса, последовательно включенные между выходом первого и другим входом второго делителей частоты второй регистр памяти, другой вход которого соединен с входом второго и вьсходом первого вентилей, вторая схема переноса, другой вход которой соединен с выходом элемента И, параллельный сумматор, другой вход которого соединен с выходом третьей схемы гк-реноса, триггер задержки и Т11етий вентиль, а также генератор импульсов эталонной частоты, выход которого соединен с вторыми входами триггера задержки,первого и третьего вентилей, при этом выход блока управления соединен с входом третьей схемы переноса, с вторыми входами второго вентиля и элемента ИЛИ и с третьим входом третьего вентиля, отличающийся тем, что, с целью повышения точности умножения, между выходом второго вентиля и другим входом третьей схемы переноса включены последовательно соединенные триггер и регистр сдвига, вторые входы которых подключены к выходу блока управления, при этом третий вход блока управления соединен с выходом параллельного сумматора.

Источники информации, принятые во внимание при экспертизе

1. Заявка N 2336740/18-09, кл. Н 03 В 19/10, 1976, по которой принято решени о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1980 |

|

SU930575A2 |

| Цифровой умножитель частоты | 1977 |

|

SU734867A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Цифровой умножитель частоты | 1984 |

|

SU1192106A1 |

| Цифровой умножитель частоты | 1976 |

|

SU663068A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU970632A1 |

| Многоканальный цифровой коррелометр | 1985 |

|

SU1262523A1 |

| Устройство диагностирования скважинных штанговых насосов | 1984 |

|

SU1224444A1 |

| Цифровое устройство для управления скоростью двигателя | 1984 |

|

SU1218367A1 |

Авторы

Даты

1979-10-05—Публикация

1977-08-15—Подача