(5) ЦИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1977 |

|

SU734867A1 |

| Цифровой умножитель частоты | 1977 |

|

SU690609A1 |

| Цифровой умножитель частоты | 1984 |

|

SU1192106A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Цифровой умножитель частоты | 1976 |

|

SU663068A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| Цифровое устройство для управления скоростью двигателя | 1984 |

|

SU1218367A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Фазометр | 1991 |

|

SU1817037A1 |

I

Изобретение относится к радиотехнике и может использоваться для умножения частоты сигналов в измерительных системах различного назначения.

По основному авт. ев .№ известен цифровой умножитель частоты., содержащий последовательно соединенные формирователь входного сигнала, блок управления, первый вентиль, первый делитель частоты, элемент И, выход которого является выходом цифрового умножителя частоты, элемент ИЛИ и первую схему переноса, выход .которой прдключен к другому входу первого делителя частоты, а другой вход - к выходу первого регистра памяти, входом подключенного к другому входу блока управления, а также последовательно соединенные кварцевый генератор, первый формирователь импульсов, второй вентиль, второй делитель частоты, выход которого подключен ко входу первого регистра

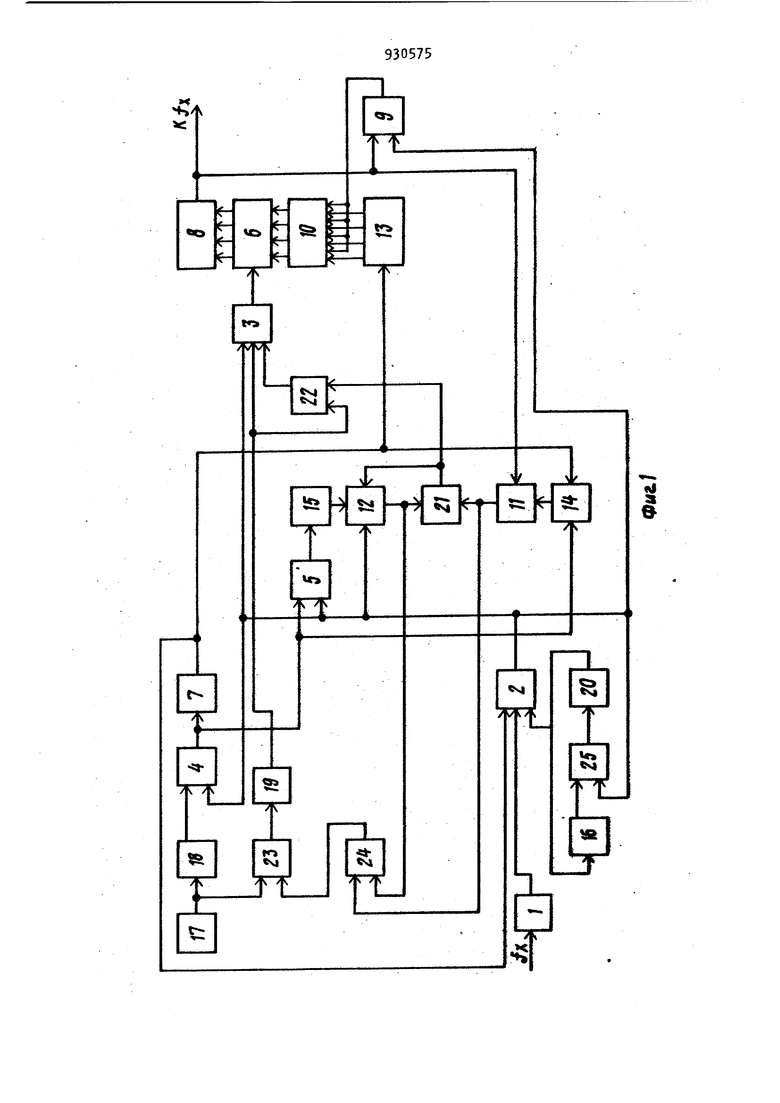

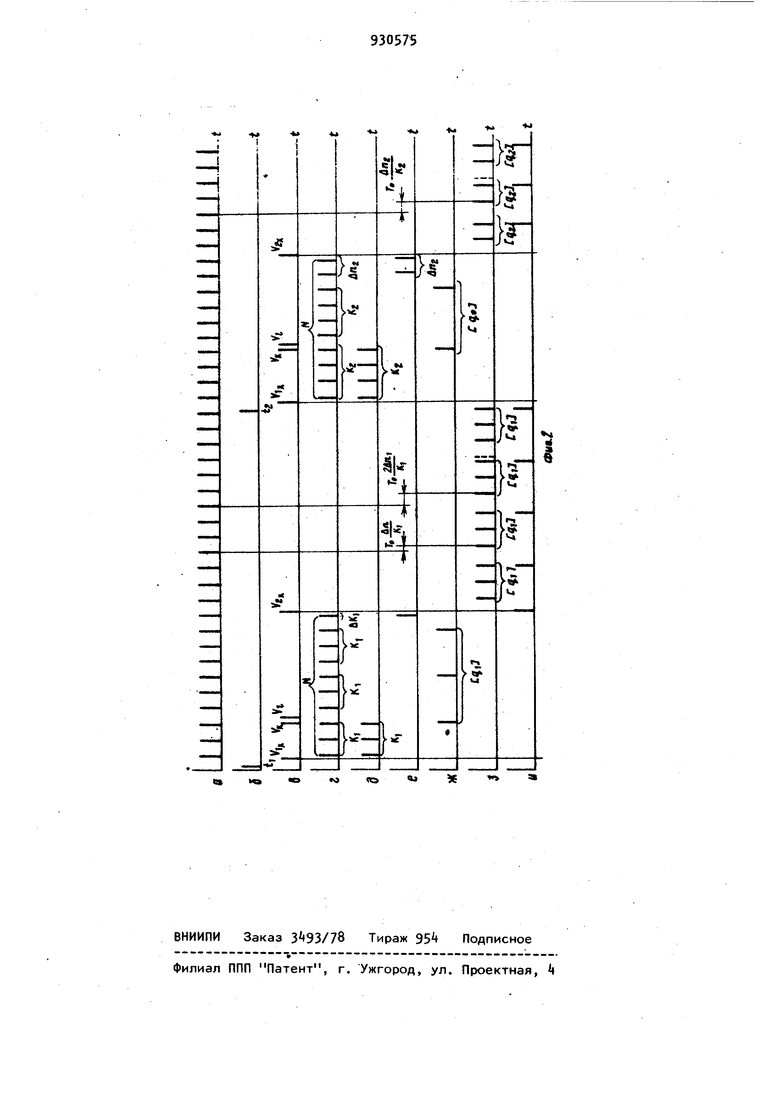

памяти, второй регистр памяти, другим входом подключенный к выходу второго вентиля и к первому входу третьего вентиля, вторая схема переноса , к другому входу которой подключен выход элемента И, сумматор и триггер задержки, выход и другой вход которого .подключены соответственно к другому и третьему входу первого вентиля, при этом выход блока управления подключен к другим входам элемента ИЛИ и второго вентиля, к второму входу третьего вентиля и через третью схему переноса - к другому входу сумматора, выходом подсоединенного к другому входу третьей схемы переноса, к третьему входу которой через третий регистр памяти подключен выход третьего вентиля, при этом между выходом кварцевого генератора и другим входом триггера задержки вк/лочены последовательно соединенные управляемый фазовращатель и второй формирователь импульсов, а выходы второй и третьей схем переноса подключены к соответствующим входам цифрового устройства деления, выход которого подсоединен к другому входу управляемого фазовращателя j. Однако в блоке управления известного умножителя при каждом изменении его выходной частоты необходимо нажи мать кнопку Пуск, что исключает возможность управления выходной частотой умножителя по заданной програм ме и ограничивает скорость изменения коэффициента умножения. Цель изобретения - увеличение скорости изменения коэффициента умножения.. Для этой цели в цифровой умножитель частоты введены последовательно соединенные четвертый регистр па мяти, блок сравнения кодов и третий формирователь импульсов, выход которого подключен к входу четвертого регистра памяти и третьему входу блока управления, при этом другой вход блока сравнения кодов соединен с выходом блока управления. На фиг. 1 представлена структурн электрическая схема предложенного цифрового умножения частоты; на фиг временные диаграммы его работы. Цифровой умножитель частоты содержит формирователь 1 входного сиг нала, блок 2 управления, первый, второй и третий вентили . первый и второй делители частоты 6 и 7 элемент И 8, элемент ИЛИ 9, первую, вторую и третью схемы переноса 1012, первый второй, третий и четвертый регистры памяти , кварцевы генератор 17 первый, второй и третий формирователи 18-20 импульсов, сумматор 21, триггер задержки 22, управляемый фазовращатель 23, цифро вое устройство деления 24, блок 25 сравнения кодов. Цифровой умножитель частоты рабо тает следующим образом. В исходном состоянии триггеры вс регистров памяти 13-16. делителя ча тоты 6 и 7, а также триггер задержки 22 находятся в нулевом состоянии На выходе блока сравнения кодов 25 высокий уровень потенциала, все вен ТИЛИ закрыты. Переключателями или с помощью цифрового кода, поступающег извне, .устанавливается коэффициент деления частоты исходного сигнала (фиг. 2а) делителем частоты 7 (коэффициент умножения умножителя) равным K.. При этом, ввиду того, что коды на входе блока сравнения кодов 25 стали различными, на его выходе установится низкий уровень потенциала, что в свою очередь, приводит к появлению импульса на выходе формирователя 20 импульсов (момент времени 1,(фиг. 26), который, во-первых, перепишет в регистр значение кода К и, как следствие, на выходе блока сравнения кодов 25 вновь установится высокий потенциал и, во-вторых, подготовит блок 2 управления к приему импульса от формирователя 1 входного сигнала. При переходе умножаемого сигнала, имеющего частоту fy, через нулевое значение, блок 2 управления вырабатывает сигнал V (фиг. 2в), что приводит к открытию вентилей и SИмпульсы с частотой f (фиг. 2а) начинают поступать в делитель частоты 7 и регистры Т и 15 (фиг. 2г и фиг. 2д). При поступлении первого выходного импульса с делителя частоты 7 (фиг. 2ж) на вход блока 2 управления, последний вырабатывает сигнал 1 (фиг. 2в) , по которому вентиль 5 закрывается. Таким образом, в регистре памяти 15 зафиксировано число К (фиг. 2д). Следующим импульсом VE блока 2 управления (фиг. 2в) содержимое регистра памяти 15 через схему переноса 12 поступает в сумматор 21 и цифровое устройство деления 2k. За время периода Т l/fy импульсы с частотой fj, поступают непрерывно как в делитель частоты 7. так и в регистр памяти 14, но с каждым выходным импульсом делителя, частоты 7 показания регистра памяти 14 сбрасываются в нуль. В итоге, к концу периода Ту в нем будет зафиксировано число Ап/ (фиг. 2е), накопленное за промежуток времени от момента последнего выходного импульса делителя частоты 7 до конца периода Ту. То же самое число дп будет зафиксировано и в делителе частоты 7. В регистр J )Г I t fj 1Чх /1 поступают выходные импульсы делителя частоты 7 (фиг. 2ж) и к концу периода T) в нем будет зафиксировано число v. По окончании периода Т. блок 2 уг1равления вырабатывает сигнал V2x 5 (фиг. 2в), (Который закроет вентиль , откроет вентиль 3, через элемент ИЛИ 9 и схему переноса 10 перенесет показания регистра памяти 13 в дели тель частоты 6. С этого момента нач нается процесс деления импульсов, поступающих на вход делителя частот 6 на q. (умножение частоты f)( на ICj .Первый выходной импульс элемента И (фиг. 2и) переносит число q из регистра памяти 13 в делитель частоты 6 и показания регистра памяти И через схему переноса 11 в сумматор 21 и сумматор цифрового устройства деления 2. В сумматоре 21 производится операция (), причем, если эта величина больше нуля, то на его выходе импульса не будет. Одновременно в цифровом устройстве деления Z осуществляется деление ftn.j на К . Код отношения поступает на управляемый фазовращатель 23 что приводит к изменению ф зы синусоиды на его выходе на величину ЗбО°дп /1. После преобразова ния в формирователе 19 импульсы, поступающие через вентиль 3 на вход делителя частоты 6, будут смещены |на величину (фиг. 2а и фиг. 2з). Второй выходной импульс умножителя производит операцию делитель частоты 6и &п в сумматор 21 и сумматор цифрового устройства деления 2, после чего в сумматоре 21 записывается число ( ), а в цифровом устройстве деления 2 осуществляется операция деления 2йп на К . Если число (K -2uin ) больше нуля - на выходе сумматора 21 импульса не будет, а управляемый фазовращатель 23 смести фазу синусоидного сигнала, поступаю щего на его вход с кварцевого генератора 17, на величину и, следовательно, импульсы, поступающие на вход делителя частоты 6, будут задержаны на Т (фиг. 2а и фиг. 2з) По мере увеличения числа выходных импульсов умножителя может оказаться что при некотором числе i величина (Kxj-iun) стайет равной или меньше нуля (на примере , и, следовательно, 3), что приведет к появлению импульса на выходе сумматора 21, который перенесет из регистра памяти 15 число К в сумматор 21 и, следовательно, в нем запишется положительное число (), а также 75 е сумматоре цифрового устройства деления 2k будет произведена операция (). На управляемый фазовращатель 23 подается код числа ()/К, что приводит к задержке импульсов, поступающих на делитель частоты 6 через вентиль 3 на величину TO (iin -К-,)/К . Одновременно выходной импульс сумматора 21 через триггер задержки 22 закрывает вентиль 3. По этой причине очередной импульс (обозначен пунктиром на фиг. 2з) через вентиль 3 не пройдет, а осуществляет переброс в исходное состояние триггера 22 задержки, который в свою очередь вновь откроет вентиль 3. Коррекция последующих импульсов происходит аналогично. В результате частота на выходе умножителя равна показанной на фиг. 2 и. При изменении величина коэффициента умножения (например, с К на Кл) цифровые коды, подаваемые на входы блока сравнения кодов 25, станут различными, и на его выходе |устано8ится низкий уровень потенциала, вследствие чего на выходе формирователя 20 появляется импульс (момент времени t2 на фиг. 26), после чего повторяются процессы, описанные выше, и на выходе умножителя установится новая частота, равная Таким образом, в предложенном цифровом умножителе частоты значительно увеличивается скорость изменения коэффициента умножения, MJO практически обеспечивает автоматизацию процесса-умножения выходной частоты умножителя посредством изменений коэффициента умножения и позволяет использовать его в системах, э которых требуется регулировка выходной частоты цифровым кодом по определяемой программе, а также в автоматизированных системах измерения и контроля. Формула изобретения Цифровой умножитель шастоты по авт. св. W , отличающийся тем, что, с целью уве личения скорости, изменения коэффициента умножения, в него введены последовательно соединенные четвертый регистр памяти,, блок сравнения кодов и третий формирователь импульсов, выход которого подключен

: 7

к ВХОДУ четвертого регистра памяти и третьему входу блока управления, при этом другой вход блока сравнения кодов соединен с выходом блока управления.

8

.Источники информации, принятые во внимание при экспертизе

o o j

tt м

a

Авторы

Даты

1982-05-23—Публикация

1980-10-27—Подача