Изобретение относится к электросвязи и может быть использовано в информационно-измерительных системах различного назначения.

- Известен цифровой умножитель частоты, содержащий последовательно соединенные формирователь входного сигнала, управляющий б.пок, первый вентиль и первый делитель частоты, а также последовательно соединенные генератор импульсов эталонной частоты, второй вентиль, второй делитель частоты, элемент И, элемент ИЛИ и первый блок для переноса, выход которого подключен к другому входу второго делителя частоты, а другой вход - к выходу нервого регистра памяти, входом подсоединенного к первому входу второго регистра па,мят,и, выход которого подключен к входу второго блока д.ля е еноса, а второй вход - к выходу первого вентиля, другим входом подсоединенного к генератора импульсов эталонной частоты и входу триггера задержки, выход которого подключен к другому входу второго вентиля, подсоединенного управляющим входом к выходу управляющего блока, другому входу элемента ИЛИ и первому входу третьего вентиля 1.

Однако данньт умножитель не обеспечивает необходимой точности умножения во всем диапазоне частот.

Целью изобретения является повьннение верхней границы умножаемых частот при обеспечении высокой точности умрюжения во всем дианазоне частот.

Для этого в цифровом умножителе частоты, содержащем последовательно соединенные формирователь входного сигнала, управляющий блок, первый вентиль и первый делитель частоты, а также носледовательно соединенные генератор импульсов эталонной частоты, второй вентиль, второй делитель частоты,элемент И, элемент ИЛИ и первый блок для переноса, выход которого подключен к другому входу второго делителя частоты, а другой вход - к выходу первого регистра памяти, входом подсоединенного к первому входу второго регистра памяти, выход которого подключен к входу второго блока для переноса, а второй вход - к выходу вентиля, другим входом подсоединенного к выходу генератора

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1977 |

|

SU734867A1 |

| Цифровой умножитель частоты | 1980 |

|

SU930575A2 |

| Цифровой умножитель частоты | 1977 |

|

SU690609A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Цифровой умножитель частоты | 1984 |

|

SU1192106A1 |

| Умножитель частоты импульсов | 1978 |

|

SU780175A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Умножитель частоты следования импульсов | 1976 |

|

SU570064A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ЖИДКОСТИ | 1991 |

|

RU2012848C1 |

arj.. lijii

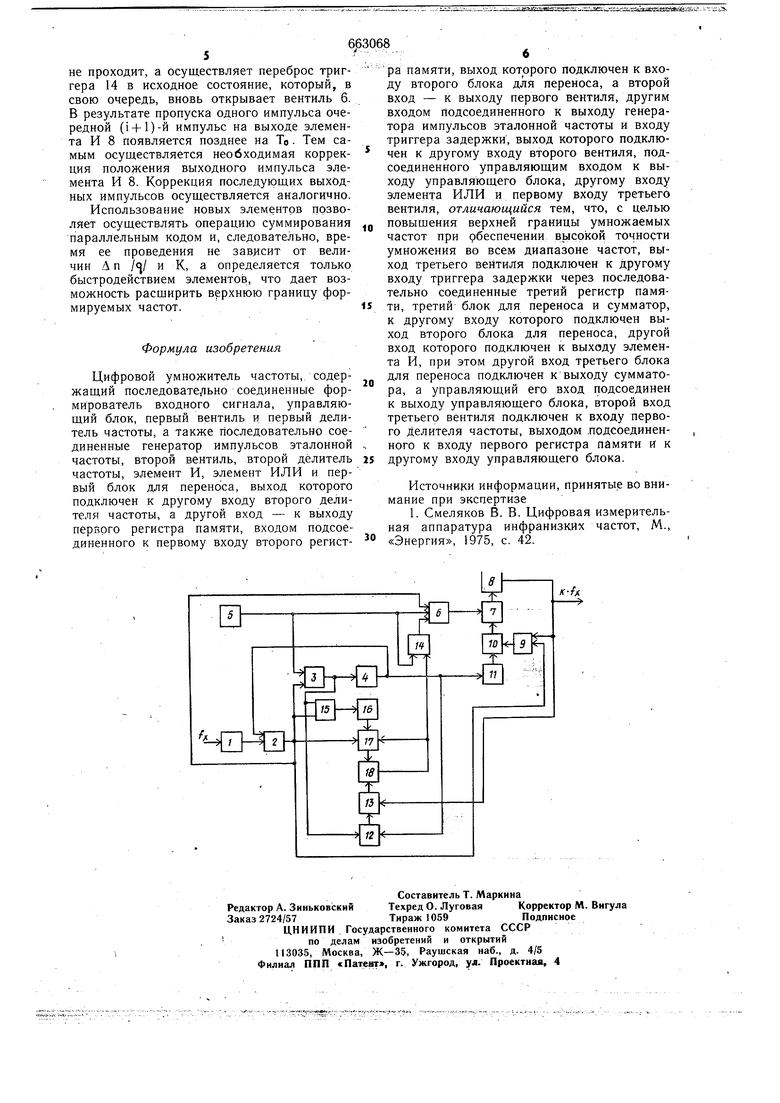

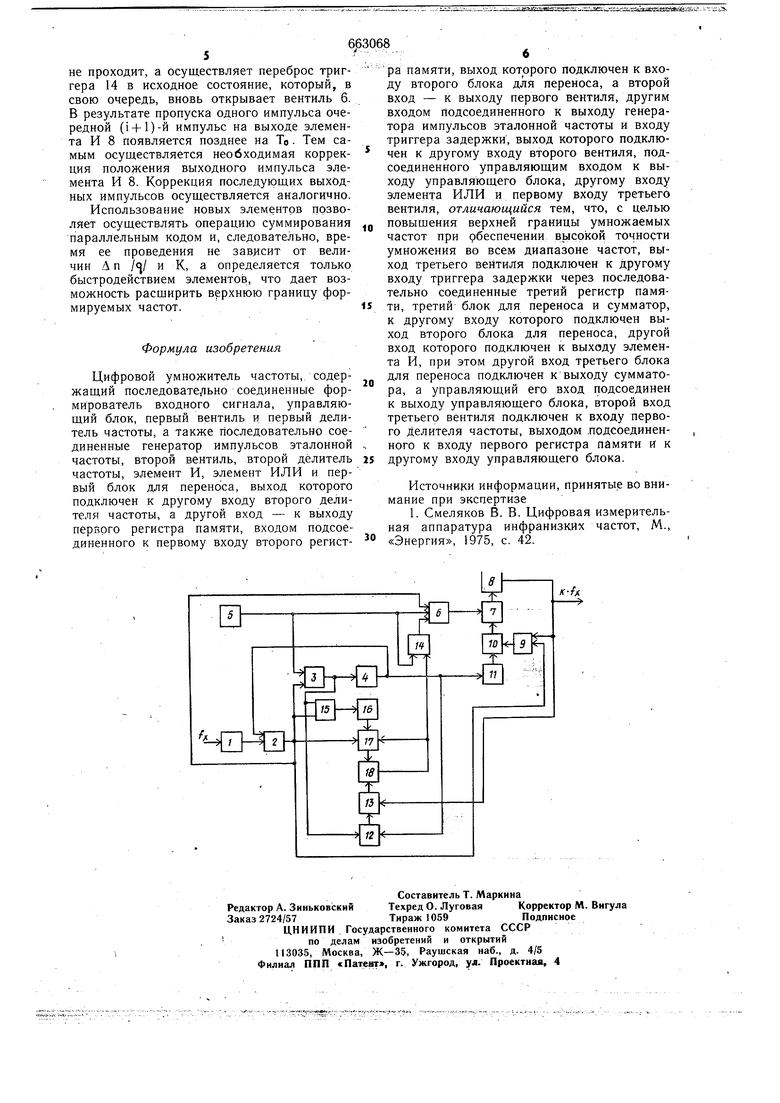

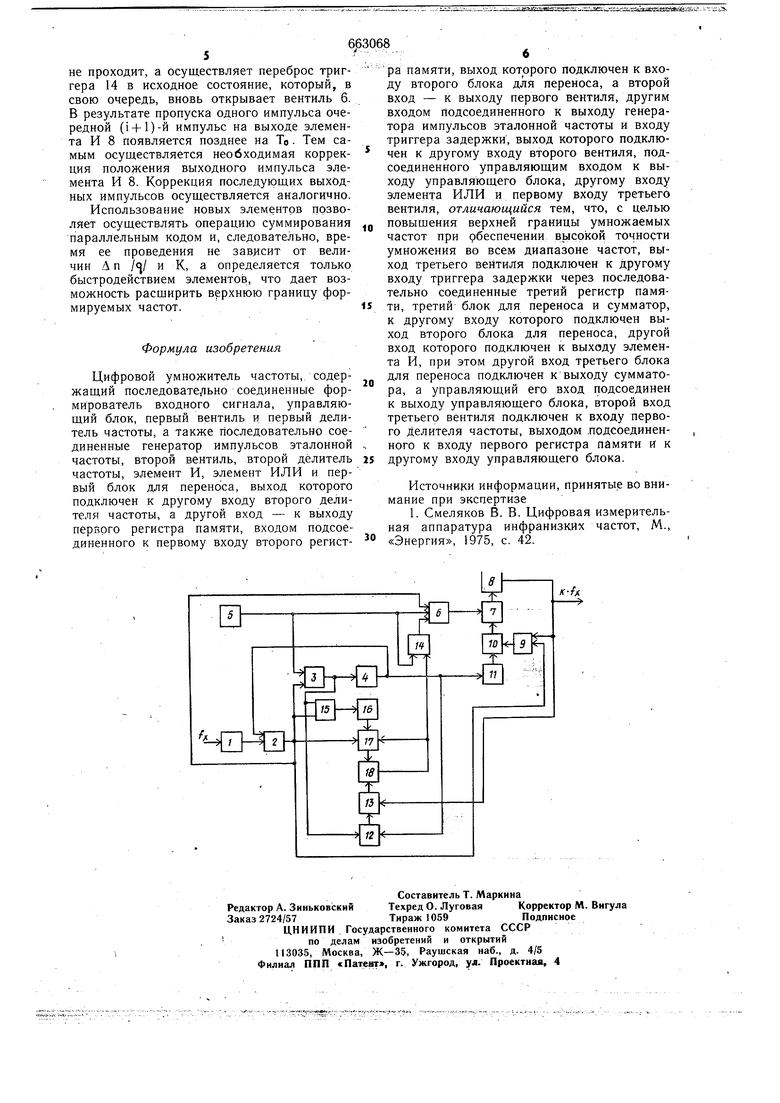

.K;«:r. 1ШпуЛьсовТтаЖннои ч&йстьГ: гера задержки, выход которого подключен к другому входу второго вентиля, подсоединённого управляющим входом к выходу управляющего блока, другому входу элемента ИЛИ и первому входу третьего вентиля, выход третьего вентиля подключен к другому входу триггера, задержки через последовательно соединенные третий регистр памяти, третий блок для переноса и сумматор, к другому входу которого подключен выход второго блока для переноса, другои вход которого подключен к выходу элемента И, при этом другой вход третьего блока для переноса подключен к выходу сумматора, а управляющий его вход подсоединен выходу управляющего блока, второй вход третьего вентиля подключен к входу первого делителя частоты, выходом подсоединенного к входу первого регистра памяти и к другому входу управляющего блока.- . На чертеже приведена структурная электрическая схема устройства. Цифровой умножитель частоты содержит последовательно соединенные формирователь 1 входного сигнала, управляющий блок 2, первый вентиль 3 и первый делитель 4 частоты, а также последовательно соединенные генератор 5 импульсов эталонной частоты, второй, вентиль 6, второй делитель 7 частоты, элемент И 8, элемент ИЛИ 9 и первый блок 10 для переноса, выход которого подключен к другому входу второго делителя 7 частоты, а другой вход - к выходу первого регистра 11 памяти, входом подсоединенного к первому входу второго регистра 12 памяти, выход которого подключен к входу первого блока 13 для переноса, а второй вход - к выходу первого вентиля 3, другим входом подсоединенного к выходу генератора 5 импульсов эталонной частоты и входу триггера 14 задержки, выход которого подключен к другому входу второго вентиля 6, подсоединенного управляющим входом к выходу блока 2, Другому входу элемента ИЛИ 9 и первому входу третьего вентиля 15, выход третьего вентиля 15 подключен к другому входу триггера задержки 14 через последовательно соединенные третий регистр 16 памяти, третий блок 17, предназначенный для переноса, и сумматор .18, к другому входу которого подключен выход второго блока 13, другой вход которой подключен к выходу элемента И 8, при этом другой вход третье го блока 17 для переноса подключен к выходу сумматора 18, а управляющий его вход ПОДСОединен к выходу блока 2, второй вход третьего вентиля 15 подключен к входу первого делителя 4 частоты, выходом подсоединенного к входу первого регистра 11 памяти и к другому входу блока 2. Устройство работает следующим образом. Ё исходном состоянии регистры 11, 12 и 16 и делители 4 и 7, а также триггер 14 находятся в нулевом состоянии. Все вентили 3, 6 и 15 закрыты. Коэффициент деления делителя 4 устанавливают равным К. Нажимают кнопку «Пуск, находящуюся в управляющем блоке 2. При этом подготавливается к работе формирователь 1.При переходе умножаемого сигнала, имеющего частоту fx, через нулевое значение, блок 2 вырабатывае сигнал Vijr , что приводит к открытию вентилей 3 и 15. Импульсы с частотой fo начинают поступать в делитель 4, регистры 12 и 16. При поступлении первого выходного импульса с делителя 4 на вход управляющего блока 2 последний вырабатывает сигнал VK, по которому вентиль 15 закрывается. Таким образом в регистре 16 фиксируется число К-Следующим импульсом Ve содержи иое регистра 16 переносится в сумматор 18. За время первого периода TU -} импульсы с частотой fo поступают непрерывно как в делитель 4, так и в регистр 12, но с каждым выходным импульсом делителя 4 показания регистра 12 сбрасываются в нуль. В итоге к KOfiny пер-вого периода в .нем фиксируется число Лп, накопленное за промежуток времени от момента последнего выходного импульса делителя 4 до конца первого периода Tiy. То же самое число Ап фиксируется ив делителе 4. В регистр 11 выходные импульсы делителя 4, и к концу первого периода в нем фиксируется число„., „ т- По окончании периода Т, блок 2 вырабатывает сигнал Vzx, который закрывает вентиль 3, открывает вентиль 6 и переносит показания регистра II в делитель 7. С этого момента начинается процесс делеПИЯ последующих периодов на частоте fx на К частей (умножение частоты fx на К). Первый выходной импульс элемента И 8 переносит показания регистра 11 в делитель 7 и показания регистра 12 в сумматор 18. Если (К-А п) в сумматоре 18 больше нуля, то на его выходе импульс не появляется. После второго выходного импульса элемента И 8 операция ввода/с /в делитель 7, А п в сумматор 18 повторяется. Если число К- , на выходе сумматора 18 импульс опять не появится. По мере увеличения числа выходных Импульсов элемента И 8 может оказаться, что при некотором числе i (К 5, п 2 и, следовательно, i 3) величина (К-iAn) становится меньше нуля, что приводит к появлению импульса на выходе сумматора 18, которыйпереносит из регистра 16 число К и, следовательно, в сумматоре 18 заменяется полр.жительнре число ( п), а также через триггер 14 на некоторое время закроется вентиль 6. Очевидно, что очередной импульс с частотой fo через этот вентиль

Авторы

Даты

1979-05-15—Публикация

1976-03-23—Подача