Изобретение относится к вычислительной технике, предназначено ,цля оперативного определения корреляционных функций случайных процессов в реальном масштабе времени и может быть использовано в автоматике, биологии, медицине и других областях науки и техники.

Цель изобретения - повьшгение быстродействия.

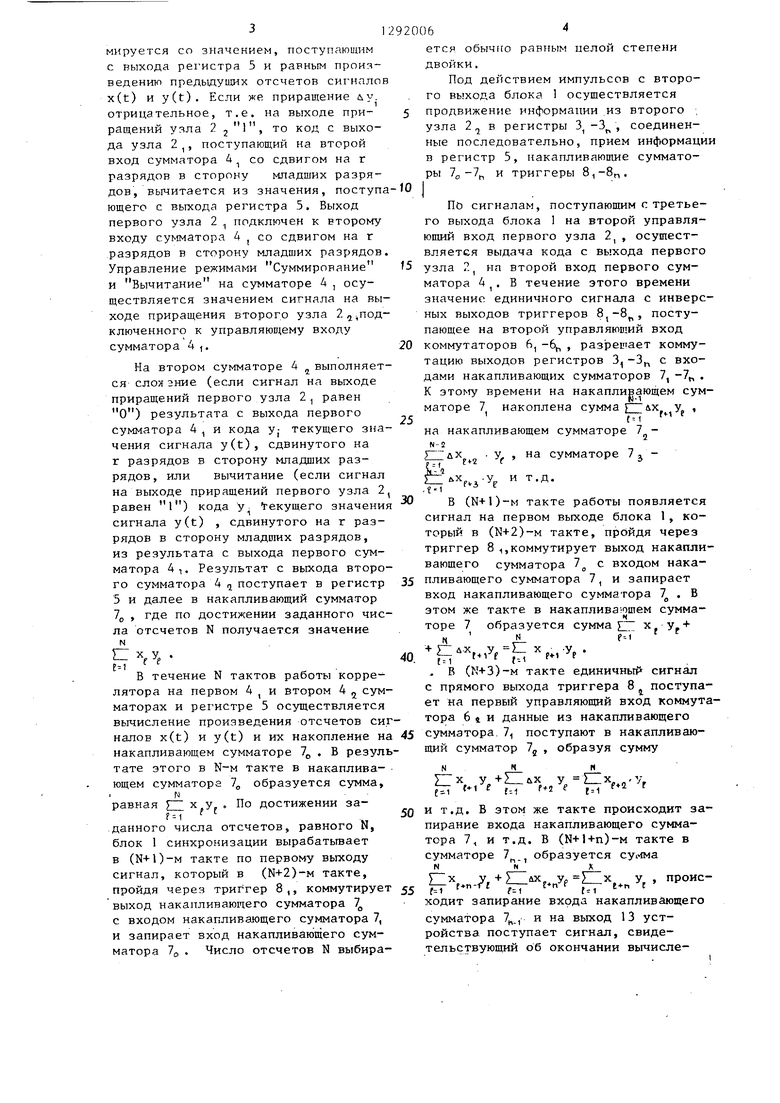

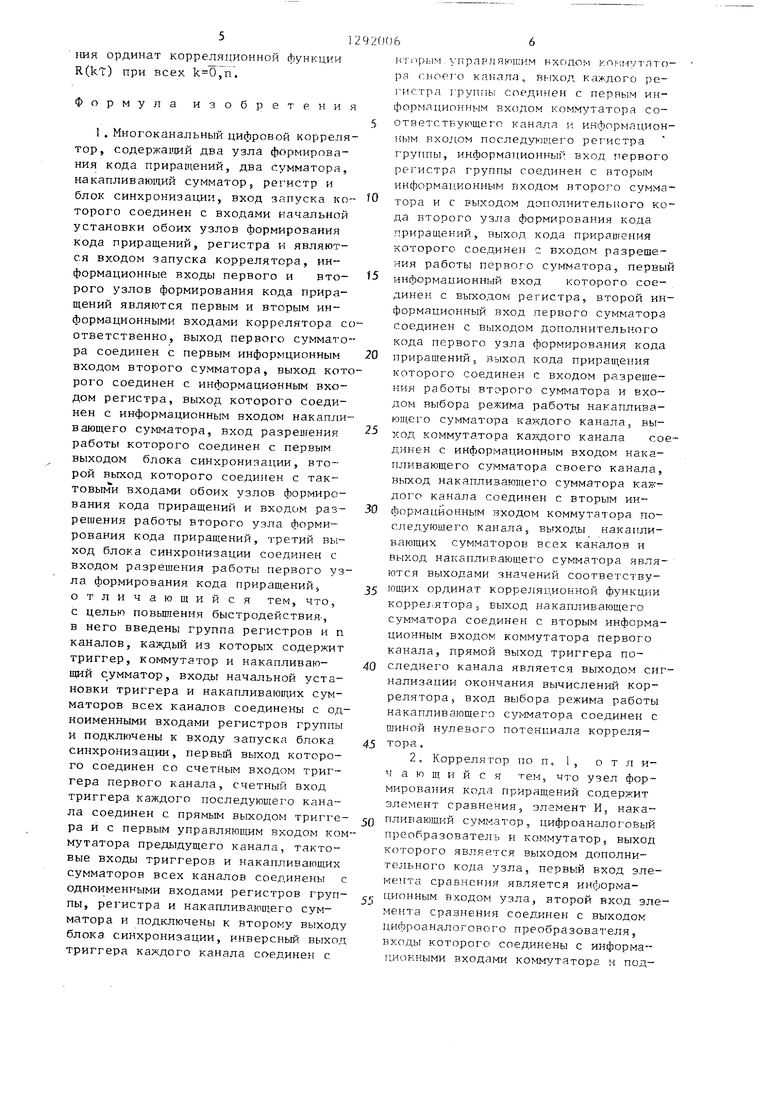

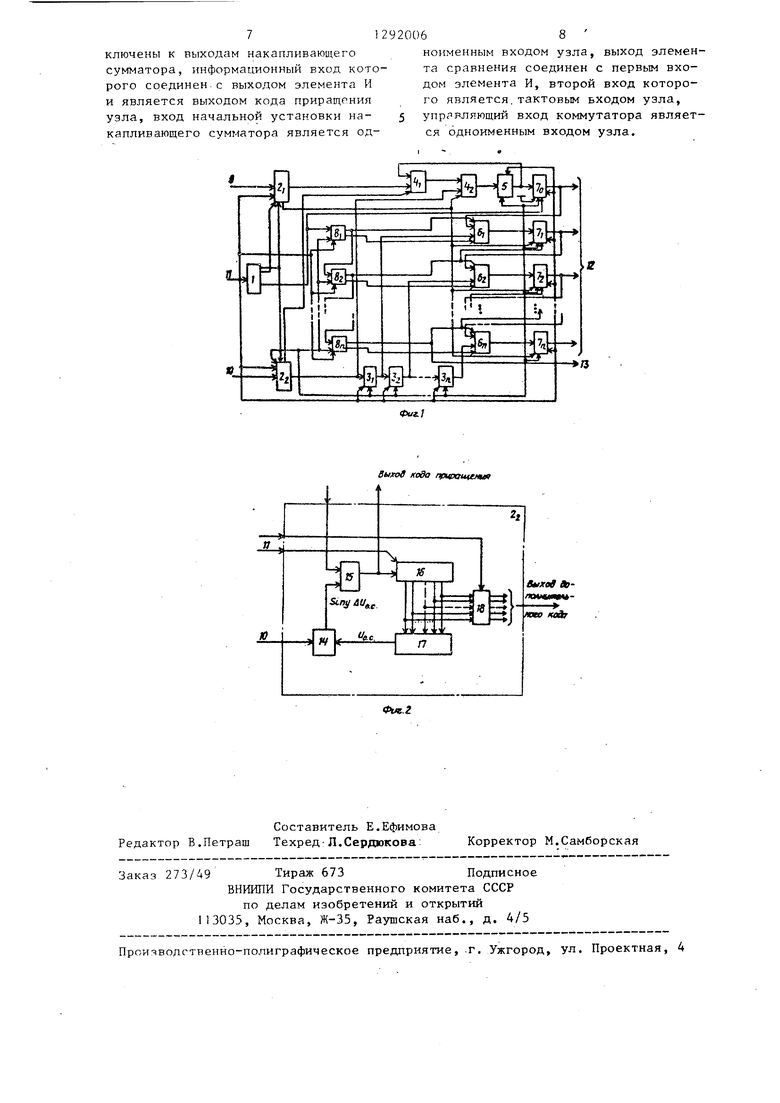

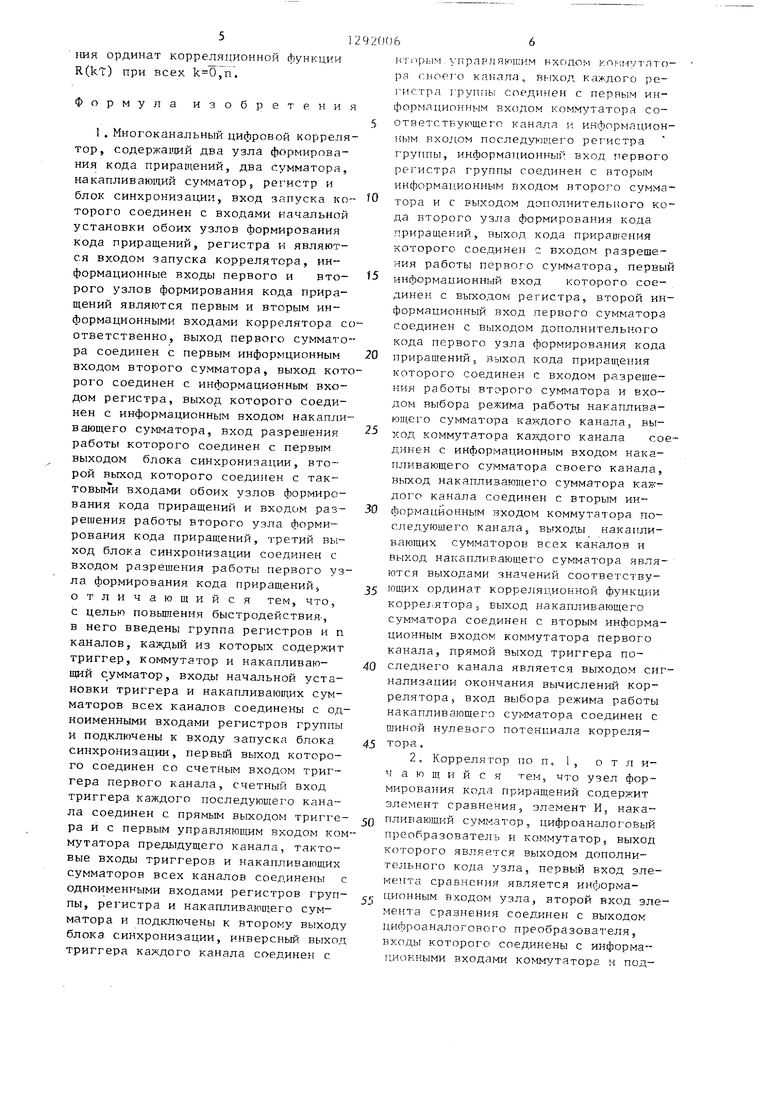

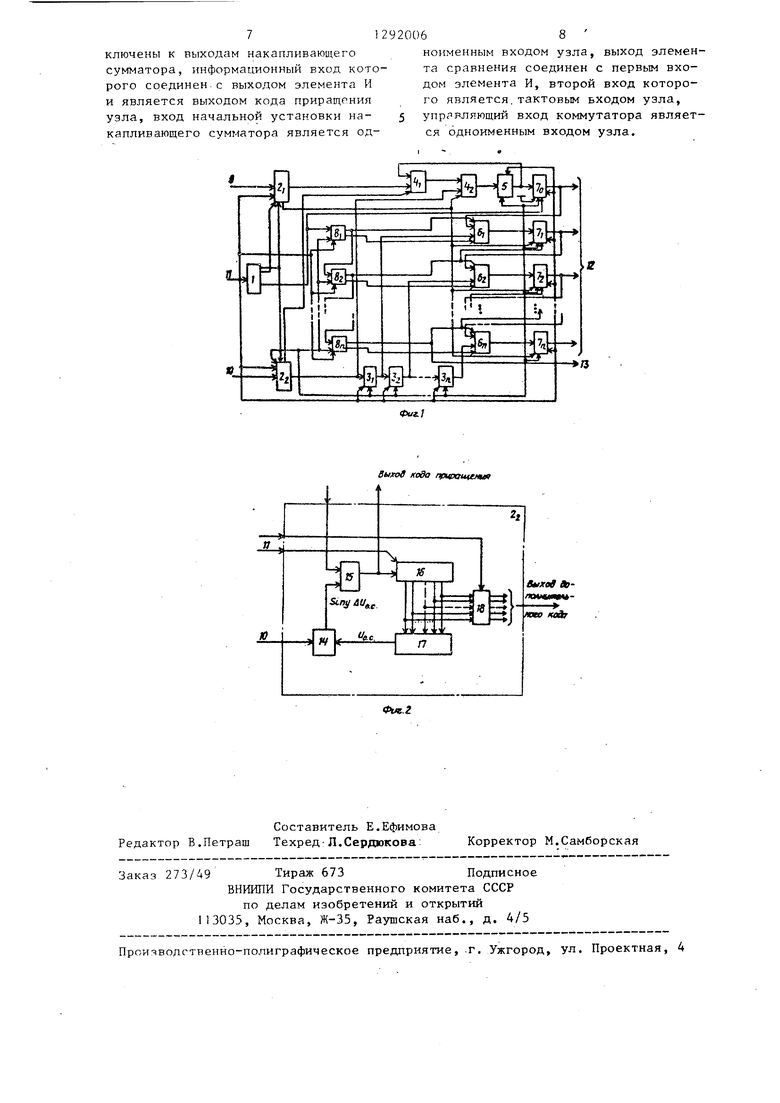

На фиг. 1 представлена структурная схема коррелятора; на фиг. 2 структурная схема узла формировани кода приращений.

Коррелятор (фиг, ) содержит бл i синхронизации, два узла , и 2 , формирования кода приращений, группу регистров 3, -3| , первый 4 , и второй 4,2 сумматоры, регистр 5,коммутаторы fi, -6 , накапливающий сум- матор 7, , накапливающие сумматоры 7,-7 , триггеры , первый 9 и второй 10 информационные входы,вхо И запуска, выходы 12 значений ординат корреляционной функпии, выхо 13 сигнализации окончания вычислений.

Узел формирования кода приращений (фиг. 2) содержит элемент 14 сравнения, элемент И 15, накаплива ющий сумматор 16, цифроаналоговый преобразователь 17, коммутатор 18.

Алгоритм работы коррелятора следующий .

вычисление i-ro произведения z, отсчетов X j и у. при вычислении корреляционной функции R(kT) при осуществляется согласно выражению

Zi х,, У,,+4У,- х,.,+у, лх, 2(.,+4У;- х,.,+у.-ах,.

Вычисление ординат корреляционной функции R(kt) при ,n ствляется по следующей схеме:

R(0)x, у, ,,+......+

+,., у,./, У.;

R(r)R(0)C3xp,,yf П:х.у. +

.

.%Л

R(2t)R(t)&,y, +

R(nT)R(n-i)t.ii:.

NN

с:йх,„у, iivy,.

Так как приращения сигналов x(t) и y(t) соответственно равны АХ и

лу, , где

лх, (x-x,-) 1 2 ; л у, Csipn(y-yj ) 1 2 ;

то значения произведений лх . у. и 4У. X . можно записать

йхд sipn(x-X| ) 2 у- ; ау. x- (y-y, ) 2 X, .

Знак произведений л х. у. и л у. х ., равный

sip;n(x-x, )©(sip,n у,) sipn(y-y. )®(siRn Xj),

определяется следуюргим образом.

Если знак приращения л.к- или ду положительный (что соответствует о на выходе приращений узлов 2 и 2), то знак произведения дх-у; или лу х равен знаку у, или х,-.Если же знак прирашения лх или ду отрицательный (что соответствует 1 на выходе приращений узлов 2 и 2), то знак произведения или лУ х, равен знаку,, противоположному у. или X ,

В корреляторе, если знак приращения дХ| или лу положительный, то значение 2 у. или 2 х прибавляется к содержимому соответствующего накапливающего сумматора 7 , а если знак приращения дх- или йу, отрицательный - вычитается из него.

Коррелятор работает следуюпшм образом

По сигналу, поступающему на вход 1 ., осуп1ествляется запуск блока 1 синхрониза1Н1и и установка в исходное состояние первого 2 и второго 2j узлов формирования кода приращений регистров 3,-3, регистра 5, сумматоров , и триггеров 8,-8 . С одного выхода узлов 2, и 2 снимается текущее значение сигналов x(t) и y(t) в дополнительном коде, с другого выхода этих же узлов - приращения сигнала в виде 1 и О (1 соответствует отрицательному приращению, а О - положительному).

Если значение приращения &у положительное, т.е. на выходе приращений узла 2j О, то код с выхода узла 2,, поступаюо;ий на второй вход сумматора 4, со сдвигом на г (г - разрядность узл(1В 2, и 2) разрядов в сторону младпшх разрядов, суммнруется со значением, поступающим с выхода регистра 5 и равньм произведению предыдущих отсчетов сигнало x(t) и y(t). Если же приращение &у. отрицательное, ращений узла 2

да узла 2 ,, поступающий на второй вход сумматора 4 со сдвигом на г

1 т.е. на выходе при2 1, то код с выхоразрядов в сторону младших разрядов, вычитается из значения, поступа ющего с выхода регистра 5. Выход первого узла 2 подключен к второму входу сумматора А со сдвигом на г разрядов в сторону младших разрядов. Управление режимами Суммирование и Вычитание на сумматоре 4 , осуществляется значением сигнала на выходе приращения второго узла . ,- ключенного к управляющему входу сумматора 4 ,.

На втором сумматоре 4 выполняется слоя 2ние (если сигнал на выходе приращений первого узла

По сигналам, поступающим с третьего выхода блока 1 на второй управляющий вход первого узла 2,, осуществляется выдача кода с выхода первого узла 2| на второй вход первого сумматора 4 ,. В течение этого времени значение единичного сигнала с инверсных выходов триггеров ,, поступающее на второй управляющий вход коммутаторов 6, -6, , разрешает коммутацию выходов регистров 3,-3 с входами накапливающих сумматоров

7, -7 .

равен

К этому времени на накапливающем сум71 Д Тнакоплена сумма АХ у ,

сумматора 4 , и кода у,- текущего зна- „а накапливающем сумматоре 7 N-2

О) результата с выхода первого

25

чения сигнала y(t), сдвинутого на г разрядов в сторону младших раз- -- рядов, или вычитание (если сигнал на выходе приращений первого узла 2, .-i равен I) кода у гекущего значения сигнала y(t) , сдвинутого на г разрядов в сторону младших разрядов, из результата с выхода первого сумматора 4i. Результат с выхода второго сумматора 4 ij поступает в регистр 35 5 и далее в накапливающий сумматор 7р , где по достижении заданного числа отсчетов N получается значение

, .40.

В течение N тактов работы коррелятора на первом 4 и втором 4 сумматорах и регистре 5 осуществляется вычисление произведения отсчетов сиг.2 У(

г.

, на сумматоре и т.д.

75 В (N+1)-M такте работы появляется сигнал на первом выходе блока 1, который в (N+2)-M такте, прбйдя через триггер 8 ,коммутирует выход накапливающего сумматора 7 с входом накапливающего сумматора 7, и запирает вход накапливающего сумматора 7 . В этом же такте в накапливающем сумматоре 7 образуется сумма j;; х у + Nf-V

Л.,-Ур . В (N+3)-M такте единичный сигнал с прямого выхода триггера 8 поступает на первый управляющий вход коммутатора 6 4 и данные иэ накапливающего

налов x(t) и y(t) н их накопление на 45 сумматора. 7 поступают в накапливающий сумматор 7jj , образуя сумму V,.,y.ev.

накапливающем сумматоре 7, . В резултате этого в N-м такте в накаплива-

ющем сумматора 7 образуется сумма,

м равная р X у . По достижении зар 1 f

данного числа отсчетов, равного N, блок 1 синхронизации вырабатьшает в (N+1)-M такте по первому выходу сигнал, который в (N+2)-M такте, пройдя через триггер 8,, коммутируе выход накапливающего сумматора 7 с входом накапливающего сумматора 7, и запирает вход накапливающего сумматора 7о

Число отсчетов N выбира-Ю t5 20

2920064

ется обычно пелой степени двойки,

Под действием импульсов с второго выхода блока 1 осуществляется продвижение информапии .из второго ; узла 2 в регистры 3 -3 , соединенные последовательно, прием информаци в регистр 5, накапливающие сумматоры 7о-7f, и триггеры 8,-8п.

По сигналам, поступающим с третьего выхода блока 1 на второй управляющий вход первого узла 2,, осуществляется выдача кода с выхода первого узла 2| на второй вход первого сумматора 4 ,. В течение этого времени значение единичного сигнала с инверсных выходов триггеров ,, поступающее на второй управляющий вход коммутаторов 6, -6, , разрешает коммутацию выходов регистров 3,-3 с входами накапливающих сумматоров

7, -7 .

25

на сумматоре т.д.

75 --.-i

В (N+1)-M такте работы появляется сигнал на первом выходе блока 1, который в (N+2)-M такте, прбйдя через триггер 8 ,коммутирует выход накапливающего сумматора 7 с входом накапливающего сумматора 7, и запирает вход накапливающего сумматора 7 . В этом же такте в накапливающем сумматоре 7 образуется сумма j;; х у + Nf-V

Л.,-Ур . В (N+3)-M такте единичный сигнал с прямого выхода триггера 8 поступает на первый управляющий вход коммутатора 6 4 и данные иэ накапливающего

сумматора. 7 поступают в накапливаю

щий сумматор 7jj , образуя сумму V,.,y.ev.

ги

И т.д. Б этом же такте происходит запирание входа накапливающего сумматора 7, и т.д. В (N+l+n)-M такте в сумматоре 7., образуется cyiviMa

.nyr ходит запирание входа накапливающего сумматора 7., и на выход 13 устройства поступает сигнал, свидетельствующий об окончании вычислекия ординат корреляционной функции R(kt) при всех ,n.

формула изобретения

1 . Многоканальный цифровой коррелятор, coдepжal Jлй два узла формирования кода приращений, два сумматора, накапливающий сумматор, регистр и блок синхронизации, вход запуска которого соединен с входами начальной установки обоих узлов формирования кода приращений, регистра и являются входом запуска коррелятора, информационные входы первого и второго узлов формирования кода приращений являются первым и вторым информационными входами коррелятора сответственно, выход первого сумматора соединен с первым информционным входом второго сумматора, выход котрого соединен с информационным входом регистра, выход которого соединен с информационным входом накапливающего сумматора, вход разрешения работы которого соединен с первым выходом блока синхронизации, второй выход которого соединен с тактовыми входами обоих узлов формирования кода приращений и входом разрешения работы второго узла формирования кода приращений, третий выход блока синхронизации соединен с входом разрешения работы первого узла формирования кода приращ,ений, отличающийся тем, что, с целью повьш1ения быстродействия-, в него введены группа регистров и п каналов, каждый из которых содержит триггер, коммутатор и накапливающий сумматор, входы начальной установки триггера и накапливающих сумматоров всех каналов соединены с одноименными входами регистров группы и подключены к входу запуска блока синхронизации, первьй выход которого соединен со счетным входом триггера первого канала, счетный вход триггера каждого последуюп1его канала соединен с прямым выходом триггера и с первым управляющим входом комутатора предыдущего канала, тактовые входы триггеров и накапливающих сумматоров всех каналов соединены одноименными входами регистров группы, регистра и накапливающего сумматора и подключены к второму выход блока синхронизации, инверсный выхо триггера каждого канала со-единен с

5

10

15

25

30

20

92(К)66

HTiipbiM xTipaPJiяюшим нхопом ког--;мутлто- ра ciioei o канала,, выход каждого ре- гнстра группы соединен с первым информационным входом коммутатора соответствующего канала -; информационным входом по Следующего рег истра группы, информационный вход первого pei HCTpa группь соединен с вторым информационным входом второго сумматора и с выходом дополнительного кода второго узла формирования кода приращений, выход кода приращения которого соединен с входом разрешения работы первого суг-даатора, первый информапионный вход которого соединен с выходом регистра у второй информационный вход первого сумматора соединен с выходом дополнительного кода первого узла формирования кода приращений, выход кода приращения которого соединен с входом разреоге- мия работы второго сумматора и входом выбора режима работы накапливающего cyiviMaTopa каждого канала, выход коммутатора ка вдого канала сое- динен с информационным входом накапливающего сумматора своего канала, вьгход накапливающего сумматора каждого канала соединен с вторым ин- формапйонным входом коммутатора последующего канала J вь ходы накапливающих сумматоров всех каналов и выход накапливающего сумматора являются выходами значений соответству- 35 ющих ординат корреляционной функции корре1;ятора , выход накапливающего сумматора соединен с вторым информационным входом коммутатора первого канала, прямой выход триггера последнего канала является выходом сигнализации окончания вычислений коррелятора, вход выбора режима работы накапливающего сумматора соединен с о иной нулевого потенциала коррелятора ,

2, Коррелятор по п. 1, от л и- чающийся тем, что узел формирования кода приращений содержит элемент сравнения, элемент И, накапливающий сумматор, цифроаналоговый преобразовате:гь и коммутатор, выход которого является выходом дополнительного кода узла, первый вход элемента сравнения является информационным входом узла, второй вход элемента сравнения соединен с выходом цифроаналогового преобразователя, входы которого соединены с инфорЕу1а- циокными входами кo tмyтaтopa и под40

45

50

712920068

ключены к выходам накапливающего нонменным входом узла, выход элемен- сумматора, информационный вход кото- та сравнения соединен с первым вхо- рого соединен с выходом элемента И и является выходом кода приращения

дом элемента И, второй вход которого является.тактовым входом узла.

узла, вход начальной установки на- 5 управляющий вход коммутатора являет- капливающего сумматора является од- ся одноименным входом узла.

нонменным входом узла, выход элемен- та сравнения соединен с первым вхо-

дом элемента И, второй вход которого является.тактовым входом узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифровой коррелятор | 1985 |

|

SU1397938A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Многофункциональный анализатор случайных процессов | 1986 |

|

SU1399766A1 |

| ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2000 |

|

RU2178894C1 |

| Коррелометр | 1984 |

|

SU1179368A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

| Устройство для определения корреляционной функции | 1987 |

|

SU1501086A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

Изобретение относится к области вычислительной техники, предназначено для оперативного определения корреляционных функций случайных процессов в реальном масштабе времени и может быть использовано в гидрометеорологии, автоматике, биологии, медицине и др. областях.Цель изобретения - повышение быстродействия . Цель достигается за счет введения в коррелятор узлов формирования кода приращений и п каналов обработки информации, что позволяет оперативно обрабатывать большой объем информации. 1 з.п, ф-лы, 2 ил.

Составитель Е.Ефимова Редактор В.Петраш Техред: Л.Сердюкова:

Заказ 273/49 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

-.- ..«.-,-.™.™.-..-.-.---.и----..---...-.-.--------- --- ---- - -------- -

Проияводгтвенно-полиграфическое предприятие, .г. Ужгород, ул. Проектная, 4

BtiiroS кода прирощеюл

Корректор М.Самборская

| Грибанов Ю.И | |||

| и др | |||

| Автоматические цифровые корреляторы | |||

| - М.: Энергия, 1971 , с | |||

| Деревянный коленчатый рычаг | 1919 |

|

SU150A1 |

| Коррелометр | 1984 |

|

SU1179368A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1984-12-28—Подача