(54) ЯЧЕЙКА ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Программируемое запоминающее устройство | 1985 |

|

SU1282219A1 |

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

| ПРОЦЕССОР ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2000 |

|

RU2180969C1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМПУЛЬСОВ НА ОДНОРОДНОЙ СРЕДЕ С ПРОГРАММНО МЕНЯЮЩЕЙСЯ СТРУКТУРОЙ | 2005 |

|

RU2331915C2 |

| Регистр сдвига | 1979 |

|

SU847372A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

изобретение относится к автоматик и вычислительной технике и предназна чено для построения вычислительной среды (однородного процессора), орйен тированной на решение информационнологических задач и массовое Ьыполнениз арифметических операций. Известна ячейка вычислительной среды, содержащая блоки хранения и обработки информации, группы элементов И, ИДИ 1. Однако она отличается низким быст; родействием. Наиболее близким техническим решением к изобретению является ячейка вычислительной среды, ссщержащая эле мент хранения информации, информационные выходы которого соединены с первой группой входов блока сравнения, вторая группа входов которого соединена с первой группой информаци онных .входов ячейки, входы записи и входы управления элемента хранения информации соединены соответственно со входами записи и первой группой входов управления ячейки, дополнител ный вход управления элемента хранени инфоржлации соединен с выходом маркер ного триггера и первым входом сДвиговото регистра, выходы блока сравне ния и элемента хранения информации соединены соответственно со вторым и третьим входами сдвигового .регистра, управляющие и информационные входы которого подключены соответственно ко второй группе входов управления и второй группе информационных . входов ячейки, причем выход сдвигового регистра подключен к первому входу блока локализации 2. вычислительная среда, построенная на базе такого элемента, обладает недостаточным быстродействием, потому что при решении информационно-логических задач возникает необходимость обработки многозначного ответа, так как в активном состоянии находиться несколько элементов, а в указанной вычислительной среде.в одно и то же ремя мржно выполнять либо операцию поиска слов, совпадающих с заданным признаком, либо вывод информации. Целью изобретения является повышение быстродействия ячейки. . Это достигается тем, что в ячейку введены три элемента И, группа входных элементов- И, элемент ИЛИ и элемент задержки, причем выходы маркерного триггера и сдвигового регистра

ссйедйнены соответственно с первым и вторым входами первого элемента И, выход которого подключен к четвертому входу сдвигового регистра, а выходы бдока сравнения и сдвигового ьегистра соединены с первыми входами соответственно второгр и третьего элементов И, выходы группы входных элементови через элемент ИЛИ соединены с: первым входом маркерного триггера, причем первые входы входных элементов И соединены с третьей группой информационных входов ячейки, а вторые входы второго, третьего и входньЬс элементов И соединены с третьей группой входов управления ячейки, второй /вход маркерного Триггера соединен с шиной сдвига ячейки; выход маркерi 6r6 TpiHWepa через элемент задержки ; подключен ко второму входу блЪкг1 локаййзаций, третий вход которого сое- I динен с входом локализации ячейки, а выходы блока локализации соединены ; с выходаки ячейки.

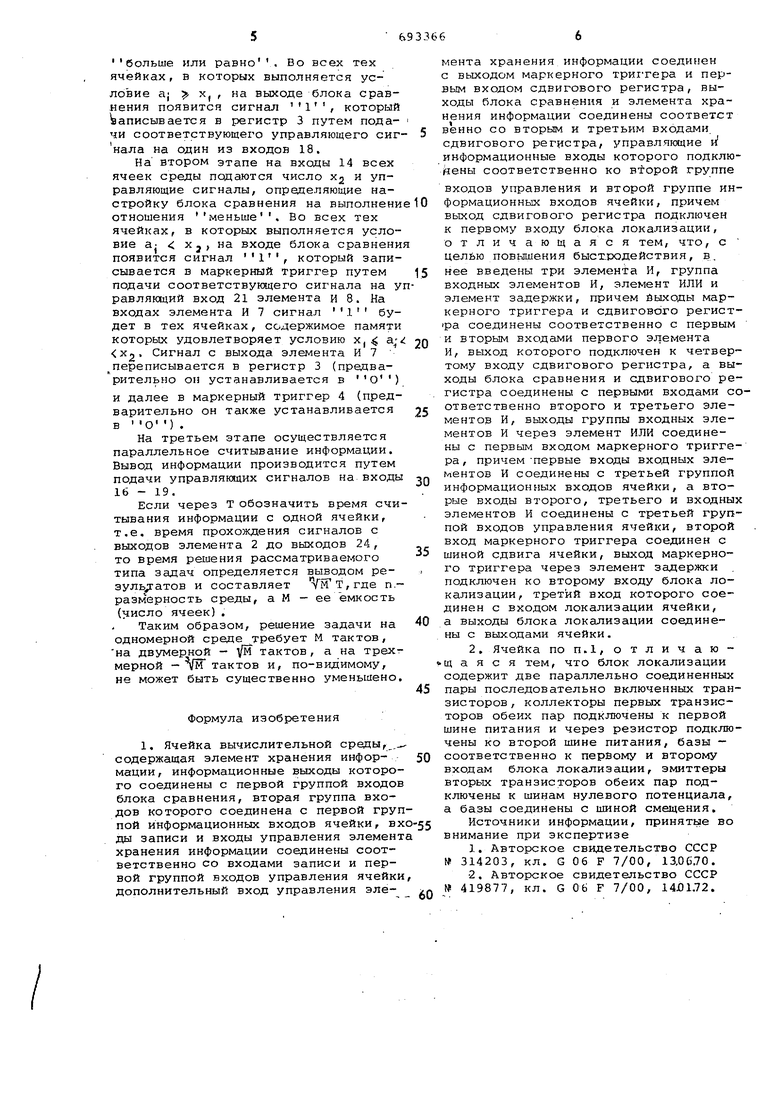

К тому же,блс к локализаций содержит две параллельно соединенных пары пОследовательно включенных транзисторов, коллекторы первых Транзис- ; торов обеих пар подключены к первой Ьаине питания и через рёзйдтор йойключены ко второй шине питания, -базы собтветствён« о к первому и второму входам, блока локализации, эмиттеры вторых транзисторов обеих пар подклю;чены к шинам нулевого потенциала, а -базы соединены С шиной смещения.

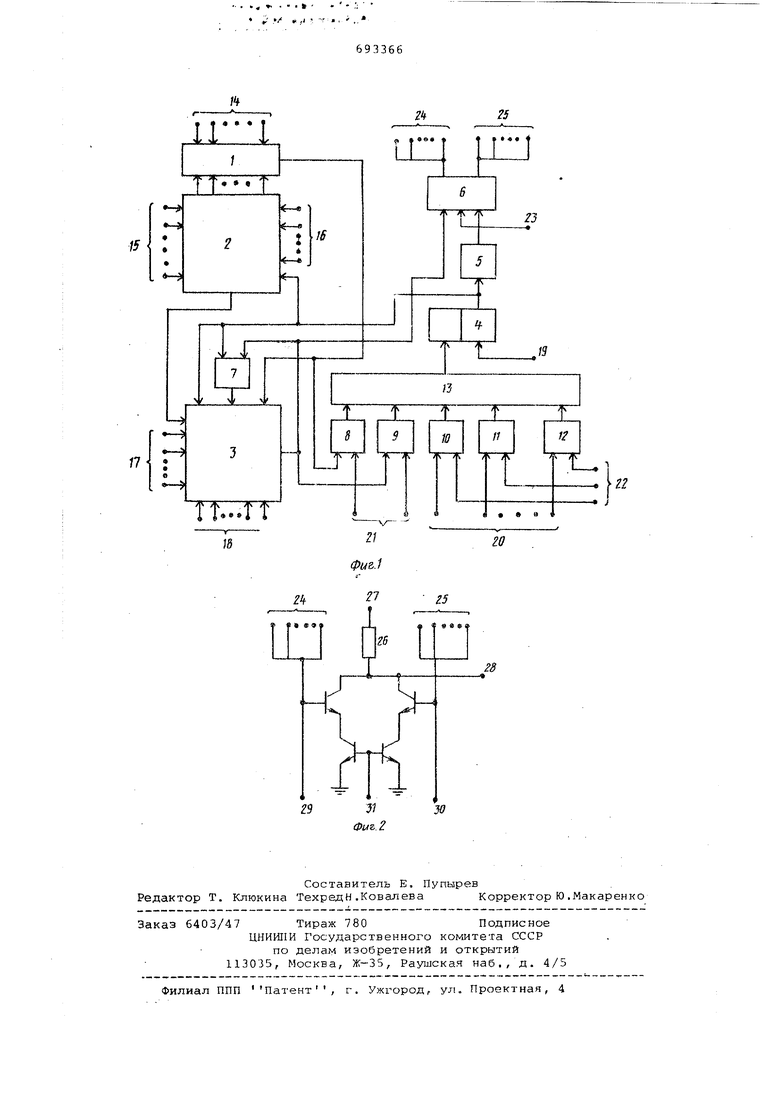

На фиг. 1 .дана структурная схема устройства; на фиг. 2 - блок локализации, пример выполнения.

: Устройство содержит блок 1 сравнения, элемент 2 хранения информации, : сдвиговый регистр 3, маркерный трйг- гер 4, элемент 5 задержки, блок 6 локализации, первый, второй и третий Элементы И 7, 8 и 9 соответственно, группу входных элементов И 10, 11 и 12, элемент ИЛИ 13, первую группу информационных входов 14, входы 15 запиСИ, первую группу входов 16 управяения , Группу инфЬрмацй(Э1ййах входов 17, вторуюгруппу входов 18 управления, ишну 19 cja;BHra, третью . -группу входов управления 20 и 21, третью группу. инфо мациоаных входов 22,вход23 локализации ячейки.

Блок локализации имеет выходы 24 и 25 ячейки, резистор 26, вторую шину 27 итания, первую шину 28 питания, .первый вход 29 блока локализации, второй вход 3D блока локализации, шину 31 смещения.

Уст р6йство работает следующим образом.. . . .

Основными режимами функционирования вычислительной среды являются-. локализация неисцравных ячеек; ввод информации , вычисление; вывОд информации .

Режим локализации предназначен для странения влияния |неисправных ячеек ычислительной сред|ы на исправные. окализация неиспра вных ячеек осущестляется без обнаружения их местополоения в среде, т.е. автоматически. Локализация основайа на отключении неисправной ячейки Iот шины питания. В зависимости от вида неисправности локализация ее производится либо с, помощью блока локализации неисправной ячейки, если в ней исправен блок локализации, либо блоками локализации соседних ячеек, если в отказавшем элементе неисправен блок локализации. Локализация неисправных ячеек осуществляется путем подачи соответствующих наборов сигналов, образующих автоматический контрольно-локализующий тест, на управляющиевхода вычислительной среды. При этом вторьте транзисторы необходимо открыть i сигналом, подаваемым на вход 31. Под действием сигналов неисправности,возникающих в вйчйслительной среде на вьтсоде сдвигового регистра и на выходе элемента 5 задержки, открываются первые транзисторы, а в результате протекания тока через резистор 26 происходит размыкание шин 27 и 28, т.е. отключение ячейки среды от питающих ;шин.

, После выполнения локализации неисправных элементов производится ввод информации в среду. В процессе ввода в эле 4енты- хранения информации ячеек вь1числительной с.реды записываются исходные данные и .программа работы среды в целом. .

В данном случае параллельно с записью информации в ячейки среды можно осуществлять и считывание информации с ячеек, так как имеются два сдвиroBfcJx регистра. Если маркерный триггер 4 находится в состоянии , то в память ячейки можно записать информационно и считать ее с помощью сдвигового регистра. При этом, не дожидаясь появления считанных сигналов , можно осуществлять запись (или считывание) информации с других ячеек.

.Для более ясного представления о функционировании вычислительной среды рассмотрим решениеследующей задачи.

Пусть требуестя отыскать в вычислительной среде, содержащей М ячеек, все числа а; , хранящиеся в блоках памяти элементов среды и удоЛхетворяющие, например, условию Xj а; «с Xj .

Решение задачи складывается из трех этапов,- .. . .

На первом этапе на входы 1,4 всех ячеек среды подаютсях, и управляющие сигналы, определяющие настройку блока сравнения на выполнение- отнсшения

.:;- Si Ччад

,N-i.Si больше или равно . Во всех тех ячейках, в которых выполняется условие aj Xj , на выходе блока сравнения появится сигнал , который Записывается в регистр 3 путем подачи соответствующего управляющего сиг нала на один из входов 18. На втором этапе на входы 14 всех ячеек среды подаются число Xj и управляющие сигналы, определяющие настройку блока сравнения на выполнени отношения меньше. Во всех тех ячейках, в которых выполняется условие aj Xj, на входе блока сравнени появится сигнал , который записывается в маркерный триггер путем подачи соответствующего сигнала на у равляющий вход 21 элемента и 8. На входах элемента И 7 сигнал 1 будет в тех ячейках, содержимое памяти которых удовлетворяет услоВИю х, 4 . Сигнал с выхода элемента И 7 переписывается в регистр 3 (предварительно он устанавливается в О) и далее в маркерный триггер 4 (предварительно он также устанавливается в О) . На третьем этапе осуществляется параллельное считывание информации. Вывод информации производится путем подачи управляющих сигналов на входы 16 - 19. Если через Т обозначить время счи тывания информации с одной ячейки, т.е. время прохождения сигналов с выходов элемента 2 до выходов 24, то время решения рассматриваемого типа задач определяется выводом резуль атов и составляет У1Гт,где п.- размерность среды, а М - ее емкость (число ячеек). Таким образом, решение задачи на одномерной среде требует М тактов, на двумерной - 1н тактов , а на трехт мерной - л/М тактов и, по-видимому, не может быть существенно уменьшено. Формула изобретения 1. Ячейка вычислительной среды,. содержащая элемент хранения инфор- .мации, информационные выходы которого соединены с первой группой входов блока сравнения, вторая группа входов которого соединена с первой груп пой информационных входов ячейки, вх ды записи и входы управления элемент хранения информации соединены соответственно со входами записи ;и первой труппой входов управления ячейки дополнительный вход управления элеЛ6 мента хранения, информации соединен с выходом маркерного триггера и первым входом сдвигового регистра, выходы блока сравнения и элемента хранения информации соединены соответст венно со вторым и третьим входами, сдвигового регистра, управляющие W информационные входы которого подклю ены соответственно ко второй группе входов управления и второй группе информационных входов ячейки, причем выход сдвигового регистра подключен ; к первому входу блока локализации, о т л и ч аю щ а я с я тем, что, с целью повышения быстлх)действия, в, нее введены три элемента И, группа входных элементов И, элемент ИЛИ и элемент задержки, причем быходь маркерного триггера и сдвигового регистipa соединены соответственно с первым И вторым Вход ами первого элемента И, выход которого подключен к четвертому входу сдвигового регистра, а выходы блока сравнения и сдвигового регистра соединены с первыми входами соответственно второго и третьего элементов И, выходы группы входных элементов И через элемент ИЛИ соединены с первым входом маркерного трйггера, причем первые входы входных элементов И соединены с третьей группой,,,, информационных входов ячейки, а вторые входы второго, третьего и входных элементов И соединены с третьей группой входов управления ячейки, второй ... вход маркерного триггера соединен с шиной сдвига ячейки, выход маркерного триггера через элемент задержки . подключён Кб второму входу блока локализации/ третий вход которого соедине й с входом локализации ячейки, а выходы блока локализации соединены с выходами ячейки...;; 2 . Ячейка по п. 1, отличаю- .... щ а я с я .тем, что блок локализации содержит две параллельно соединенных пары последовательно включенных транзисторов , коллекторы первых транзисторов обеих пар подключены к первой шине питания и через резистор подключены ко второй шине питания, базы - соответственно к первому и второму входам блока локализации, эмиттеры вторых транзисторов обеих пар подключены к шинам нулевогр потенциала, а ба.эы соединены с шиной смещения. Источники информации, принятые во внимание при экспертизе J. Авторское свидетельство СССР № 314203, кл. G Об F 7/00, 13,06,70. L. 2. Авторское свидетельство СССР № 419877, кл. G 06 F 7/00, 14Л1,72.

Авторы

Даты

1979-10-25—Публикация

1976-02-26—Подача