(54) УСТРОЙСТВО ДЛЯ ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ . ЦИФРОВЫХ ИНТЕГРАТОРОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| ПРОГРАММНОЕ УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ НЕИСПРАВНОСТЕЙ В ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ | 1973 |

|

SU370609A1 |

| Устройство для разбраковки полупроводниковых диодов | 1983 |

|

SU1164636A1 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1221655A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1166121A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля и диагностики радиоэлектронной аппаратуры | 1986 |

|

SU1432463A1 |

I

Изобретение относится к вычислительной технике.

Известно программное устройство для обнаружения неисправностей в цифровых вычислительных машинах, содержащее блоки управления, блоки коммутации, блоки анализа и регистрации сигналов, блоки индикации,, предназначенное для автоматизации обнаружения неисправностей в режиме наладки различных узлов в машине. П.

Недостатком известного устройства является то, что оно не позволяет обнаруживать неисправности в цифровых интеграторах в режиме их наладки.

Наиболее близким по технической, сущности к предлагаемому является программное устройство для обнаружения неисправностей в цифровых вычислительных машинах, содержащее блок коммутации, блок выдачи контрольных кодов, блок управления, блок .вывода, счетчик микроциклов, блок ангшиза

и регистрации сигналов, вкшочаклций матрицу регистрации рабочих сигналов, матрицу регистрации помех, дешифратор и счетчик номера контролируемого элемента, причем выходы блока вьщачи контрольных Vкодов подключены к кодовым шинам цифровой машины, входам счетчика микроциклов и блока вывода, выходы счетчика микроциклов подключены Ко входам блока вцдачи

10 контрольных кодов и блока вывода, выходы которого подключены ко входам блока управления, подключенного ко входам блока выдачи контрольных кодов , счетчика микроциклов, блока выtsвода, блока коммутации и счетчика номера контролируемого элемента блока анализа и регистрации сигналов, выходы матрицы регистрации рабочих сигналов и матрицы регистрации помех

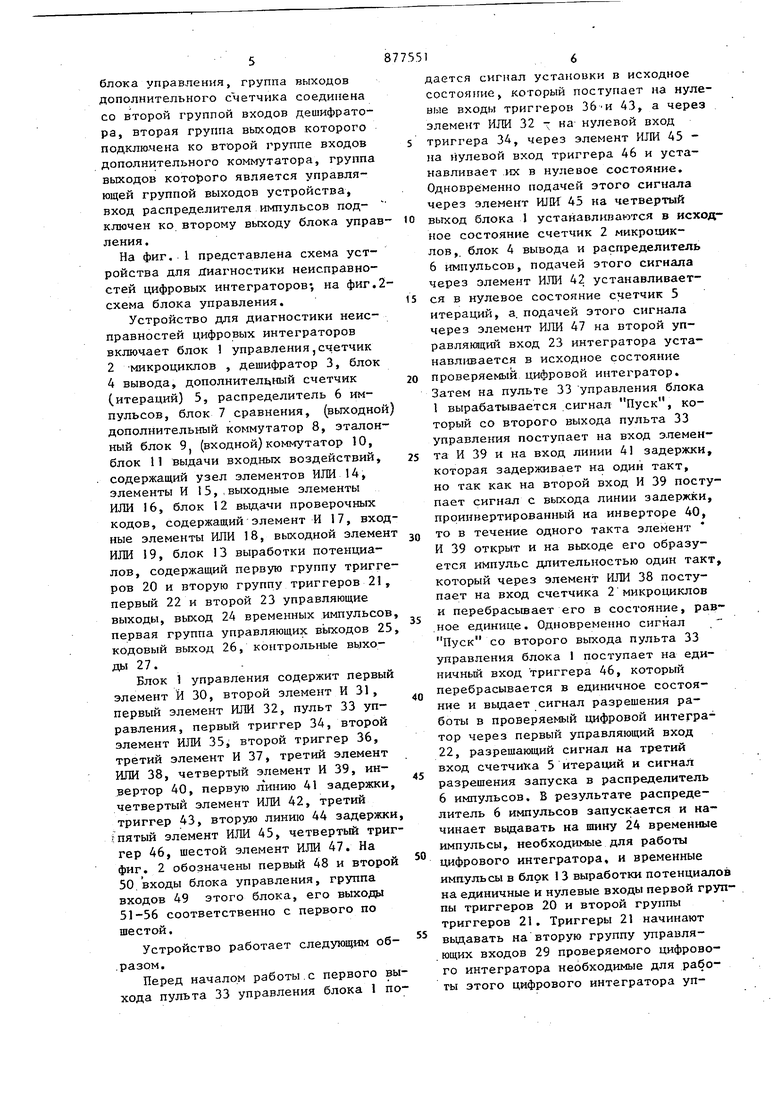

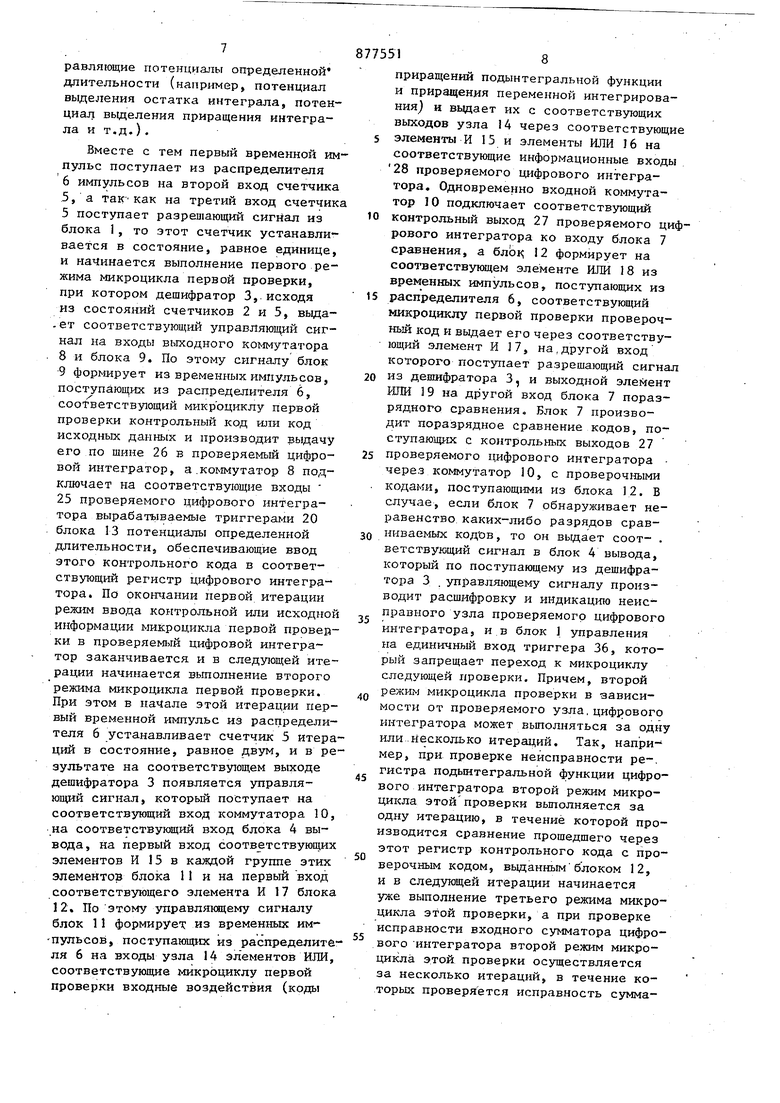

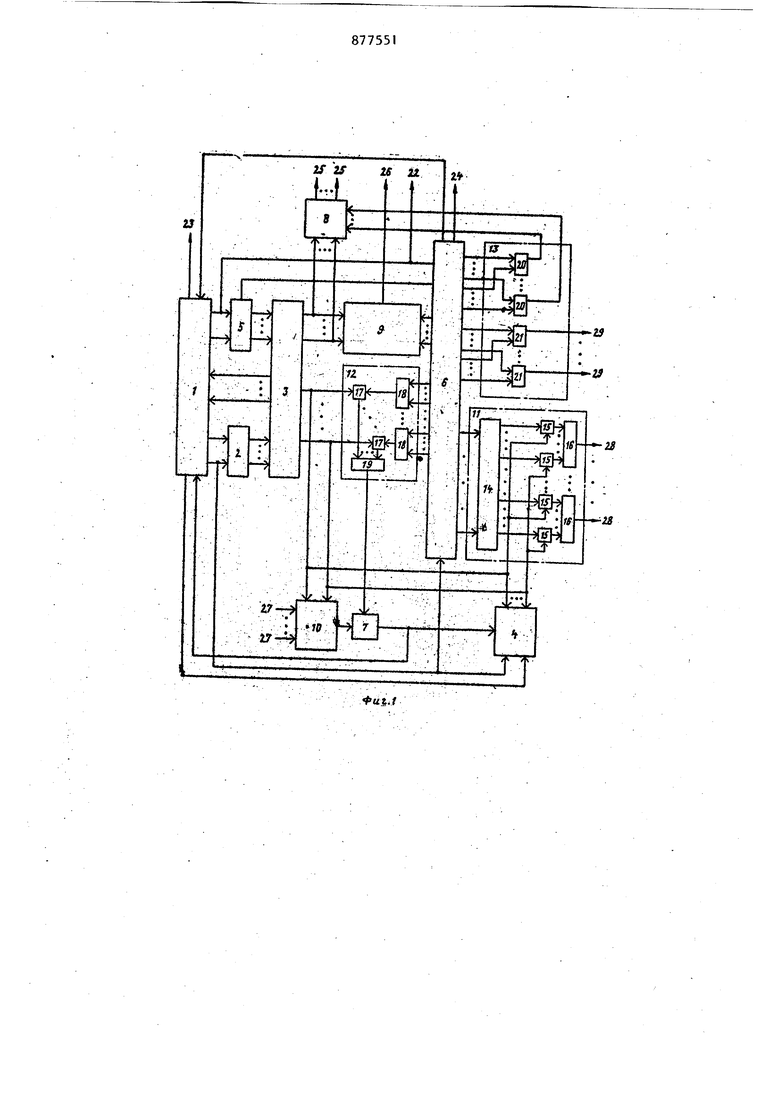

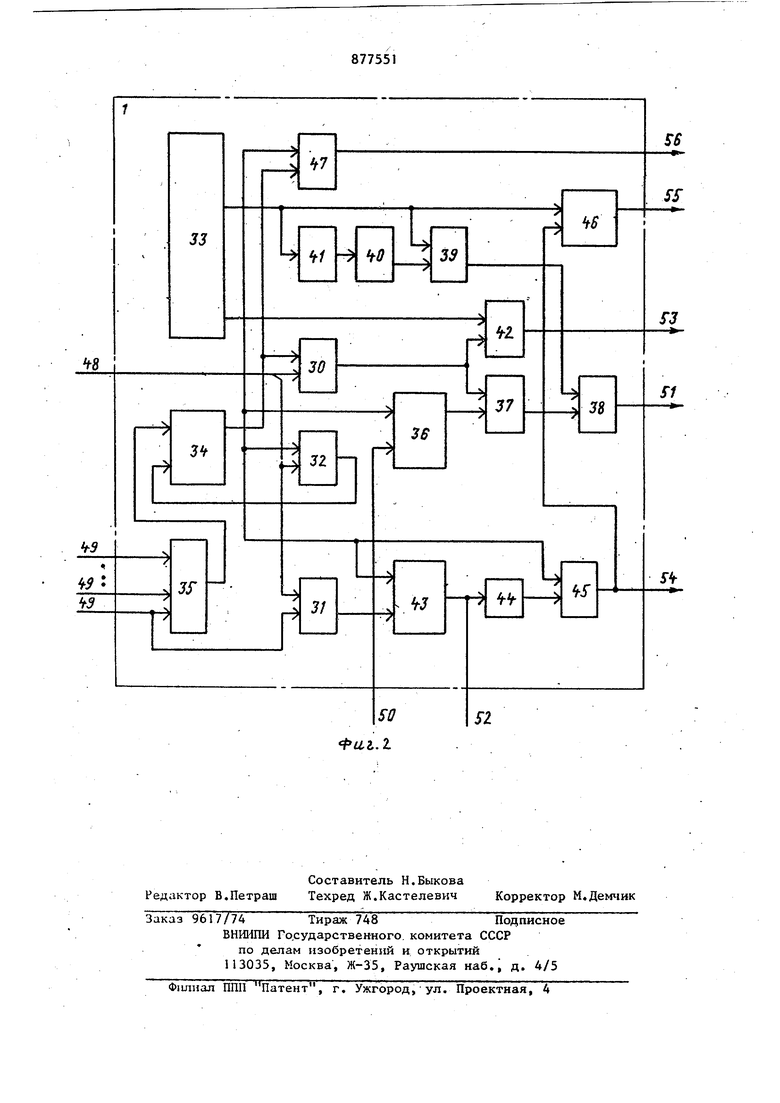

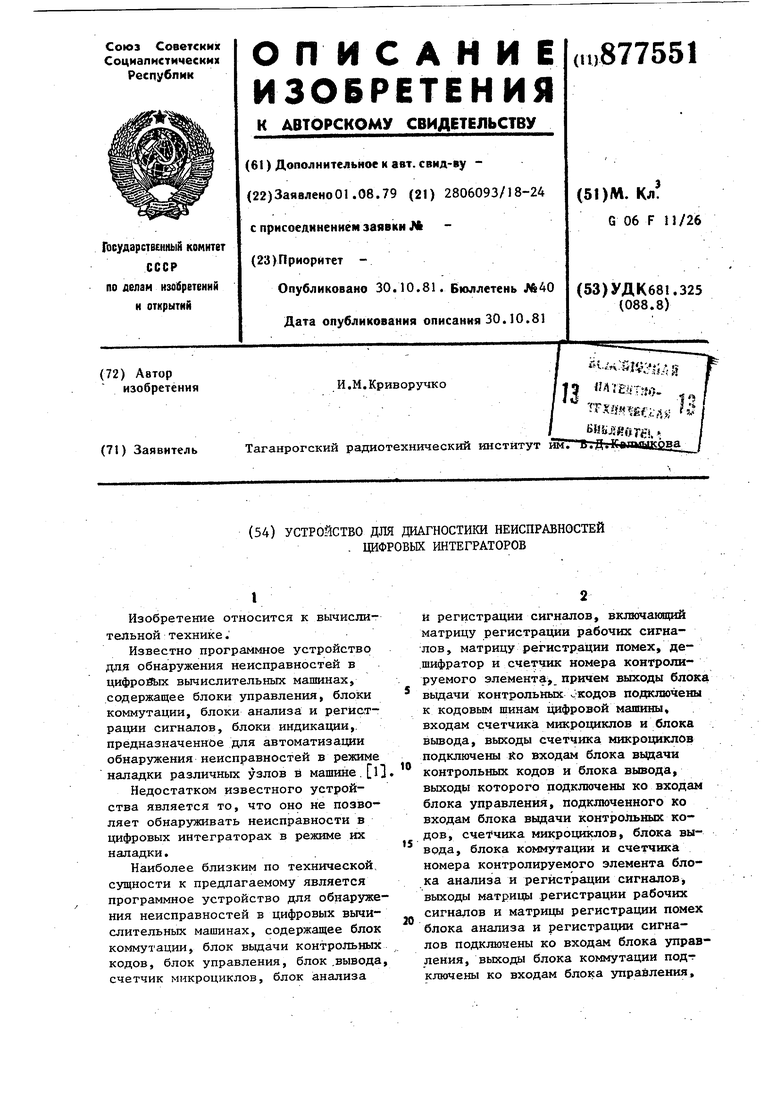

30 блока анализа и регистрации сигналов подключены ко входам блока управления, выходы блока коммутации под-г ключены ко входам блока упрайления. блока вывода, матрицы регистрации«ра бочих сигналов и матрицы, регистрации помех блока анализа и регистрации сигналов, а входы блока коммутации подключены к контрольным точкам контролируемых узлов цифровой йашины, выходы счетчика номера контролиру-емого элемента блока анализа и регистрации сигналов подключены ко вхо ду блока вывдда и через дешифратор блока .анализа и регистрации сигналов ко входам матрицы регистрации рабочих сигналов и матрицы регистрации помех блока анализа и регистрации сигналов 2 . Недостатком известного устройства является, то, что оио не позволяет . обнаруживать неисправности в цифровьп .интеграторах в режиме их -налаДки В то же время ручной поиск неисправностей в цифровых интеграторах в режиме наладки требует з-начительных зат рат времени на каждый интегратор. Цель изобретения - увеличение быс родействия. . Поставленная цель достигается .тем что в.устройство для диагностики неисправностей цифровых интеграто ров, содержащее блок управления эта лонный блок, блок контрольных .кодов блок ввода, коммутатор и счетчик, пр этом первый выход блока управления соединен с первым входом счетчика, второй выход блока управления объеди нен с первым входом блока ввода и подключен ко второму входу c4eT4Hka, группа выходав:жоторого соединена с первой группой входов дешифратора, группа выходов которого подключена к группе входов блока управления, третий выход которого является управляющим входом устройства, вторая группа выходов дешифратора соединена с первой группой входов эталонного бло ка, третья группа выходов дешифратора объединена с первой группой вхо дов коммутатора, первой группой входов блока ввода и подключена к перво группе входов блока контрольный кодов, вторая группа входов коммутатор является группой контрольных выходов устройства, четвертый выход блока управления соединен со вторым входом блока ввода, введены дополнительный счетчик, дополнительный коммутатор, распределитель импульсов, блок выработки потенциалов, блок вьщачи входнык воздействий и блок сравнения, |причем блок выдачи входных воздействий содержит две группы элементов И и три группы элементов ИЛИ, выходы элементов ИЛИ первой и второй групп блока выдачи входных воздействий являются группой информационных выходов устройства, выходы элементов И первой и второй групп подключены к соответствунщим входам элементов ИЛИ первой и второй групп, первые входы элементов И первой и второй групп подключены к соответствующим входам элементов ИЛИ третьей группы, группы входов которых соединены с первой грзшпой выходов распределителя импульсов, вторыевходы элементов И первой и второй групп объединены и подклк)чены к группе входов блока ввода; блок выработки потенциалов содержит две группы триггеров, при- .чем выходы триггеров первой группы являются первой группой управляющих выходов устройства, вь;1ходы триггеров второй группы подгслючены к первой группе входов дополнительного коммутатора, первые входы триггеров второй группы подключены ко второй группе выходов распределителя импульсов, к третьей группе которого подключены вторые выходы триггеров второй груп пы, первые триггеров первой . грзгапЫ подключены к четвертой группе выходов распределителя импульсов, к пятой группе выходов которого подключены вторые входы триггеров первой группы, шестая группа выходов распределителя импульсов соединена со второй группой входов эталонного блока, седьмая группа выходов рас пределителя импульсов подключена ко второй группе входов блока контролььшх кодов, выход которого соединен с первым входом блока сравнения,, второй вход которого подключен к выходу коммутатора, выход блока сравнения объединен со входом блока ввода и подключен к первому входу блока управления, второй вход которого соединён -с первым входом распределителя импульсов, второй выход которого является Импульсным выходом устройства, четвертый выход распределителя импульсов объединен с первым входом дополнительного счетчика, подключен к пятому выходу блока управления и является управляющим выходом устройства, пятый выход распределителя импульсов соединен со вторым входом дополнительного счетчика, третий вход которого подключен к шестому выходу 5 блока управления, группа выходов дополнительного счетчика соединена со второй группой входов дешифратора, вторая группа выходов которого подключена ко второй группе входов дополнительного коммутатора, группа выходов которого является управляющей группой выходов устройства, вход распределителя импульсов подключей ко второму выходу блока управ ления. На фиг, 1 представлена схема устройства для диагностики неисправностей цифровых интеграторов; на фиг. схема блока управления. Устройство для диагностики неисправностей цифровых интеграторов включает блок 1 управления,счетчик 2 микродиклов , дешифратор 3, блок 4 вывода, дополнител1 ный счетчик (итераций) 5, распределитель 6 импульсов, блок 7 сравнения, (выходной дополнительный коммутатор 8, эталон кый блок 9, (входной) коммутатор 10, блок 11 выдачи входных воздействий, содержащий узел элементов ИЛИ 14, элементы И 15,,выходные элементы ИЛИ 16, блок 12 вьщачи проверочных кодов, содержащий элемент И 17, вход ные элементы ИЛИ 18, выходной элемен ИЛИ 19, блок 13 выработки потенциалов, содержащий первую группу тригге ров 20 и вторую группу триггеров 21 первый 22 и второй 23 управляющие выходы, выход 24 временных импульсов первая группа управляющих вьгходов 25 кодовый выход 26, контрольные выходы 27. Блок 1 управления содержит первый элемент И 30, второй элемент И 31, первый элемент ИЛИ 32, пульт 33 управления, первый триггер 34, второй элемент ИЛИ 35; второй триггер 36, третий элемент И 37, третий элемент ИЛИ 38, четвертый элемент И 39, инвертор 40, первую линию 41 задержки четвертый элемент ИЛИ 42, третий триггер 43, вторую линию 44 задержки пятый элемент ИЛИ 45, четвертый триг гер 46, шестой элемент ИЛИ 47. На фиг. 2 обозначены первый 48 и второй 50, входы блока управления, группа входов 49 этого блока, его выходы 51-56 соответственно с первого по шестой. Устройство работает следующим об.разом. Перед началом работы.с первого вы хода пульта 33 управления блока 1 по 1 дается сигнал установки в исходное состояние, который поступает на нулевые входы триггеров 36-и 43, а через элемент ИЛИ 32 - на нулевой вход триггера 34, через элемент ИЛИ 45 на нулевой вход триггера 46 и устанавливает их в нулевое состояние. Одновременно подачей этого сигнала через элемент ИЛИ 45 на четвертый выход блока 1 устанавливаются в исходное состояние счетчик 2 микроаиклов,, блок 4 вывода и распределитель 6 импульсов, подачей этого сигнала через элемент ИЛИ 42 устанавливается в нулевое состояние счетчик 5 итераций, а. подачей этого сигнала через элемент ИЛИ 47 на второй управляклдиз вход 23 интегратора устанавл1шается в исходное состояние проверяемый цифровой интегратор. Затем на пульте 33 управления блока 1 вырабатывается .сигнал Пуск, который со второго выхода пульта 33 управления поступает на вход элемента И 39 и на вход линии 41 задержки, которая задерживает на один такт, но так как на второй вход И 39 поступает сигнал с вькода линии задержки, проиивертированный на инверторе 40, то в течение одного такта элемент И 39 открыт и на выходе его образуется импульс длительностью один такт, который через элемент ИЛИ 38 поступает на вход счетчика 2микро11 1клов и перебрасьшает его в состояние, рав,ное единице. Одновременно сигнал Пуск со второго выхода пульта 33 управления блока 1 поступает на единичный вход триггера 46, который перебрасывается в единичное состояние и выдает сигнал разрешения работы в проверяемый цифровой интегратор через первый управляющий вход 22, разрешающий сигнал на третий вход счетчиХа 5 итераций и сигнал разрешения запуска в распределитель 6 импульсов. В результате распределитель 6 импульсов запускается и начинает выдавать на шину 24 временные импульсы, необходимые для работы цифрового интегратора, и временные импульсы в блок 13 выработки потенциалов на единичные и нулевые входы первой группы триггеров 20 и второй группы триггеров 21. Триггеры 21 начинают выдавать на вторую группу управляющих входов 29 проверяемого цифрового интегратора необходимые для работы этого цифрового интегратора управляющие потенциалы определенной длительности (например, потенциал выделения остатка интеграла, потенциал выделения приращения интеграла и т.д. ),

Вместе с тем первый временной импульс поступает из распределителя 6 импульсов на второй вход счетчика 5, а так как на третий вход счетчика 5 поступает разрешающий сигнал из блока 1, то этот счетчик устанавливается в состояние, равное единице, и начинается выполнение первого режима микроцикла первой проверки, при котором дешифратор 3, исходя из состояний счетчиков 2 и 5, вьща.ет соответствующий управляющий сигнал на входы выходного коммутатора

8и блока 9. По этому сигналу блок

9формирует из временргых импульсов, поступающих из распределителя 6, cootвeтcтвylOIЦий микроциклу первой проверки контрольный код или код исходных данных и производит выдачу его по шине 26 в проверяемый цифровой интегратор, а.коммутатор 8 подключает на соответствующие входы 25 проверяемого цифрового интегратора вырабатываемые триггерами 20 блока 13 потенциалы определенргой длительности, обеспечивающие ввод этого контрольного кода в соответствующий регистр цифрового интегратора. По окоргчании первой итерации режим ввода контрольной или исходной информации микроцикла первой провепки в проверяемый цифровой интегратор заканчивается и в следующей итерации начинается выполнение второго режима микроцикла первой проверки. При этом в начале этой итерации первый временной импульс из распределителя 6 устанавливает счетчик 5 итераций в состояние, равное двум, и в результате на соответствующем выходе дешифратора 3 появляется управляющий сигнал, который поступает на соответствующий вход коммутатора 10 на соответствующий вход блока 4 вывода, на первый вход соответствующих элементов И 15 в каждой группе этих элементов блока 11 и на первый вход соответствующего элемента И 17 блок 12. По этому управлямщему сигналу блок 11 формирует из временных им

пульсов, поступающих из распределит ля 6 на входы узла 14 элементов ИЛИ соответствующие кикроциклу первой проверки входные воздействия (коды

775518

приращений подынтегральной функции и приращения переменной интегрирования) н вццает их с соответствующих выходов узла 14 через соответствующие

S элементы И 15 и элементы ИЛИ 16 на соответствующие информационные входы 28 проверяемого цифрового интегратора. Одновременно входной коммутатор 10 подключает соответствующий

10 контрольный выход 27 проверяемого цифрового интегратора ко входу блока 7 сравнения, а бло 12 формирует на соответствующем элементе ИЛИ 18 из временных импульсов, поступающих из

15 распределителя 6, соответствующий микроциклу первой проверки проверочный код и выдает его через соответствующий элемент И 17, на,другой вход которого поступает разрешающий сигнал из дешифратора 3, и выходной элемент ИЛИ 19 на другой вход блока 7 поразрядного сравнения. Блок 7 производит поразрядное сравнение кодов, поступаю11р-1Х с контрольных выходов 27 проверяемого цифрового интегратора через коммутатор 10, с проверочными кодами, поступающими из блока 12. В случае, если блок 7 обнаруживает неравенство каких-либо разрядов сравниваемых кодов, то он выдает соот- . ветствующий сигнал в блок 4 вывода, который по поступающему из дешифратора 3 . управляющему сигналу производит расшифровку и индикацию неисправного узла проверяемого цифрового интегратора, ив блок 1 управления на единичный вход триггера 36, который запрещает переход к микроциклу следующей проверки. Причем, второй режим микроцикла проверки в зависимости от проверяемого узла,цифрового интегратора может выполняться за одну или .ргесколько итераций. Так, например, при проверке неисправности ре-, гистра подьштегральной функции цифрового интегратора второй режим микроцикла этой проверки выполняется за одну итерацию, в течение которой производится сравнение прошедшего через этот регистр контрольного кода с проверочным кодом, выданнымблоком 12, и в следующей итерации начинается уже выполнение третьего режима микроцикла эТой проверки, а при проверке исправности входного сумматора цифрового интегратора второй режим микроцикла этой проверки осуществляется за несколько итераций, в течение коTopbJK проверяется исправность сумматора по каждому входу, при этом счетчик 5 итераций последовательно устанавливается в начале каждой итерации в состояние, равное двум, трем, и т.д., и на соответствующих выходах дешифратора 3 появляются управляющие сигналь, последовательно вызывающие формирование блоком 11 соответствующих приращений подынтегральной функции и их выдачу на первый, второй, первый и второй, третий, первьй и третий, второй и третий, и т.д. информационные входы 28 проверяемого цифрового интегратора, а также формирование и выдачу блоком 12 соответствующих проверочных кодов на вход блока 7, на другой вход которого поступают с соответствующего контрольного выхода 27 через коммутатор 10 проверяемые коды суммы приращений, образующиеся на выходе входного сумматора проверяемого цифрового интегратора и, аким образом, последовательно изменяя свое состояние во втором режиме микроцикла проверки входного сумматора, счетчик 5 обеспечивает последовательную проверку этого сумматора по каждому входу.

После Окончания второго режима .ми- кроцикла данной проверки начинается третий режим, выполняющийся за одну итерацию. При этом в начале этой итерации счетчик 5 итерации устанавливается первым временным импульсом из распределителя, 6 в следующее состояние и на соответствующем выходе первой группы выходов дещифратора 3 появляется сигнал, который поступает в блок 1 управления через элемент ИЛИ 35 на единичный вход триггера 34, который перебрасывается в единичное состояние и выдает через элемент ИЛИ 47 по входу 23 в проверяемый цифровой интегратор сигнал установки в исходное состояние. А по окончании этой итерации в блок 1 управления на первый его вход поступает последний , временной импульс, который проходит через открытый элемент И 30 и элемент ИЛИ 42 на первый вход счетчика 5 и .устанавливает его в нулевое состояние ОдновременнЬ этот временной импульс проходит с выхода элемента. И 30 через открытый элемент И 37 (триггер 36 переходит в единичное состояние и закрывает элемент И 37 лишь в том случае, если проверяемый узел интегратора оказывается неисправным и из блока 7 поступает сигнал неравенства кодов)

и элемент ИЛИ 38 на первый вход счетчика 2 микроциклов и перебрасывает его в следующее состояние, подготавливая тем самым устройство к выполнению микроцикла следукнцей проверки. Тогда в начале следующей итерации первый временной импульс поступает в блок 1 управления через элемент ИЛИ 32 на нулевой вход триггера 34

0 и по переднему фронту устанавливает его в нулевое состояние, заканчивая тем самым выработку на вход 23 сигнала установки в исходное состояние проверяемого цифрового интегратора. Одновременно счетчик 5 устанавлива5ется первым временным импульсом из распределителя 6 f состояние,.равное единице, и начинается выполнение первого режима микроцикпа следующей

0 проверки, и далее вьтолнение микро цикла этой проверки осуществляется аналогично предыдущему.

В случае, если же проверяемый узел оказывается неисправным, то во вто5ром режиме микроцикла проверки этого узла при сравнении в блоке 7 проверяемого и проверЧ}1Ых кодов обнаруживается их неравенство, и, как уже отмечалось, блок 7 выдает соответств ующий сигнал в блок 4 вывода, где

0 производится расшифровка и индикация неисправного узла проверяемого цифрового интегратора, и в блок 1 управления на единичный вход триггера 36, который устанавливается в единичное состояние и закрывает элемент И 37, запрещая тем самым прохождение соответствующих импульсов на вход счетчика 2, т.е. запрещая переход к микро- циклу следущей проверки. Тогда в третьем режиме микроц№кла этой проверки блок 1 по сигналу из дещифратора 3, прошедшему через ИЛИ 35 на вход триггера 34, устанавливает в исходное состояние проверяемый цифровой

5 интегратор подачей соответствукяцего сигнала с выхода триггера 34 через элемент ИЛИ 47 на вход 23, а по последнему временному импульсу, прошедщему через элементы И 30 и ИЛИ 42,

0 блок 1 устанавливает в нулевое состояние счетчик 5, подготавливая тем самым устройство к повторению микроцикла проведенной проверки, так как счетчик 2 микроциклов остается

5 в исходном состоянии рследствие того, ЧТОтриггер 36 устанавливается по сигналу из блока 7 в единичное состояние и закрывает элемент И -37,

запрещая тем самым прохождение импульсов с выхода элемента И 30 на вход счетчика 2. В начале следующей итерации по первому временному импульсу, поступающему в блок I через элемент ИЛИ 32 на .вход триггера 34,- заканчивается выработка на вход 23 сигнала установки в исходное состояние проверяемого цифрового интегратора и одновременно этим же временным импульсом, поступающим из распределителя б, счетчик 5 устанавливается в состояние, равное единице, и начинается снова выполнение первого режима, микроцикла это же проверки, в который обнаружена неисправность, а далее все режимы микроцикла этой проверки начинают циклически повторяться и с п рмощью осциллографа, входящего в состав блока 4, просмотром динам1-гческого режима / работы неисправного узла выясняется причина его неисправности. Затем устройство выключается и после устр-анения неисправности вновь включается, устанавливаются сигналом с пульт

33управления блока 1 в нулевое состояние соответствующие узлы устройства; триггеры 34,;36, 43, 46 блока

1 , счетчик 2 микроциклов, блок 4 вывода, счетчик 5 итераций, распреде литель 6 .импульсов и в исходное состояние устанавливается проверяемый цифровой рштегратор. Затем вырабатывается сигнал Пуск и все проверки снова повторяются.

После окончания микроцикла последней проверки с соответствующего выхода дешифратора 3 в блок 1 управления на единичный вход триггера 34 через элемент ИЛИ 35 и на вход элемента И 31 поступает сигнал окончания диагностики, по которому триггер

34перебрасывается в единичное состояние и подачей соответствующего сигнала через элемент ИЛИ 47 в проверяемый цифровой интегратор устанавливает его в исходное состояние, А

по окончании этой итерации в блок i управления поступает предпоследний временной импулъс, который проходит через открытый элемент И 31 и устанавливает в единичное состояние триггер. 43, который вьщает на индикацию в блок 4 вывода сигнал исправности проверяемого цифрового интегратора. По последнему временному импульсу, проходящему через элемент И 30 и ИЛИ 42, устанавливается в нулевое

состояние счетчик 5 и одновременно в том же такте с выхода триггера 43, задерживаясь на один такт на линии 44 задержки, поступает через элемент

ИЛИ 45 сигнал, по которому .блок 1 прекращает диагностику неисправностей, устанавливая в нулевое состояние соответствующие узлы устройства и прекращая выработку разрешающего

сигнала на входы счетчика 5, распределителя 6 и на первый управляющий вход 22 проверяемого цифрового интегратора, сбрасывая в нулевое состояние триггер 46. На этом проверка

исправности цифрового интегратора заканчивается.

Таким образом, предлагаемое устройство позволяет автоматизировать процесс., поиска и обнаружения неисправностей в цифровых интеграторах и тем самым значительно сократить время обнаружения неисправностей в них, ускорить и облегчить их наладку.

Формула изобретения

Устройство для диагностики неисправностей цифровых интеграторов, содержащее бйок управления, эталон-ный блок, блок контрольных кодов, блок ввода, коммутатор и счетчик, при этом первый выход блока управления соединен с первым входом счетчика, второй выход блока управления объединен с первым входом блока вво-. да и подключен ко второму входу счетчика, группа выходов которого соединена с первой группой входов дещи-фратора, группа выходов которого подключена к группе входов блока управления, третий выход которого .является управляющим входом устройства, вторая группа выходов дешифратора соединена с первой группой входов эталонного блока, третья группа выходов дешифратора объединена с первой группой входов коммутатора, первой группой входов блока ввода и подключена . к первой группе входов блока контрольных .-кодов, вторая группа входов коммутатора является группой контрольных выходов устройства, четвертый выход блока управления соединен со вторым входом блока ввода, отличающееся тем, что,, с целью увеличения быстродействия, устройство содержит дополнительный счетчик, дополнительный коммутатор, распределитель импульсов, блок выработки потенциалов, блок выдачи входных воздействий и блок сравнения, причем блок выдачи входных воздействий содержит две группы элементов И и три группы элементов ИЛИ, выходы элементов ИЛИ первой и второй групп блока вьщачи входных воздействий являются группой информационных выходов устройства, вькоды элементов И первой и второй групп подключены к соответств ющим входам элементов ИЛИ первой и второй групп, первые входы элементов И первой и второй пзупп подключены к соответствукщим входам элементов ИЛИ третьей группы, группы входов которых соединены с первой группой выходов распределителя импульсов, вторые входы элементов И первой и второй групп объединены и подключены к группе входов блока вво да; блок выработки потенциалов содержит две группы триггеров, причем выходы триггеров первой группы яв.ляются первой группой управляющих выходов устройства, выходы триггеров второй группы подключены к первой группе входов дополнительного коммутатора, первые входы триггеров второ группы подключены ко второй группе выходов распределителя импульсов, к третьей группе которого подключены вторые выходы триггеров второй группы, первые входы триггеров первой группы подключены к четвертой группе выходов распределителя импульсов, к пятой группе выходов которого подключены вторые входы триггеров первой группы, шестая группа выходов распределителя импульсов соединена СО второй группой входов эталонного -, блока, седьмая группа выходов распределителя импульсов подКлюч на ко второй группе входов блока контрольных кодов, выход которого соединен с первым входом блока сравнения, второй вход которого подключен к выходу коммутатора, выход блока сравнения объединен со входом блока ввода и подключен к первому входу блока управления, второй вход которого соединен с первым выходом распределителя импульсов, второй выход которого является импульсным выходом устройства, четвертый выход распределителя импульсов объединен -с первым входом до.полнительного счетчика, подключен к пятому выходу блока управления и является управляющим выходом .устройства, пятый выход распределителя импульсов соединен со вторым входом дополнительного счетчика, третий вход которого подключен к шестому выходу блока управления, группа выходов дополнительного счетчика соединена со второй группой входов дешифратора, вторая группа выходов которого подключена ко второй группе входов дополнительного коммутатора, группа выходов которого является управля щей группой выходов устройства, вход распределителя импульсов подключен ко второму выходу блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 378852, кл. G 06 F 11/00, 1971. 2.Авторское свидетельство СССР № 370609, кл. G 06 F 11/04, 1969.

23

PUi.l

Авторы

Даты

1981-10-30—Публикация

1979-08-01—Подача