1

Изобретение относится к вычислительной технике и может быть использовано при конструировании вычислительных систем и систем телекоммуникации.

Известно устройство для передачи двоичной информации, содержащее схемы сопряжения (адаптеры) с линиями передачи, память для хранения управляющих слов для каждой линии передачи, управляющий регистр для временного хранения одного управляющего слова, схему синхронизации, схему управления, соединенную с управляющим регистром, входным и выходным регистрами и -через схему коммутации с памятью, буферный регистр для связи с процессором 1.

Это устройство в соответствии с каждым управляющим словом, которое считывается из памяти, осуществляет управление передачей данных между одной из линий связи и процессором, причем системы передачи данных, подключаемые к. линиям связи, могут быть как синхронного, так и асинхронного типа. Управляющее слово вместе с входными сигналами из соответствующего адаптера и содержимого счетчика синхроимпульсов устанавливают все состояния, необходимые для обслуживания адаптера и записи нового или частичного модифицированного или того же управляющего слова, обратно в память.

В данном устройстве . для выполнения операций ввода-вывода выделен автономный блок памяти для хранения управляющих слов для каждой линии передачи, что разгружает центральный процессор от обслуживания операций ввода-вывода. Однако структурное построение устройства препятствует увеличению количества обслуживаемых линий передачи данных, а также предъявляет достаточно высокие требования к центральному процессору в отношении времени ожидания данных.

Инициация ввода или вывода данных --В устройстве производится под управлением счетчика-таймера, т. е. имеет место сугубо последовательное обслуживание каналов передачи данных.

При этом по каждому очередному синхроимпульсу счетчик-таймер увеличивает свое содержимое на «1, что соответствует переходу на обслуживание очередного канала.

Поскольку устройство должно обеспечить работу линий связи с достаточно широким диапазоном скоростей передачи данных, то частота синхроимпульсов должна быть выбрана с учетом максимальной скорости передачи данных и при этом выход на обслужи-вание менее скоростных каналов часто будет производиться впустую. Это снижает производительность устройства в целом..

Поток данных между процессором и устройством передачи довольно значителен. Поэтому при наличии одного регистра связи, как это имеет место в рассматриваемом, центральный процессор должен прерывать свою работу всякий раз по исчерпанию слова данных в обслуживаемом канале передачи данных. При этом время поиска слойа Данных в центральном процессоре не должно превышать квант времени обслуживания данного канала в устройстве, что вызывает дополнительные требования к центральному процессору.

Наиболее близки.м по технической сущности к. изобретению является устройство, содержащее триггеры, дешифратор, блок коррекции, блок сопряжения, шифратор,

блок приоритета, блок управления, таймер, регистр и блок анализа управляющих слов 2.

Каждому каналу соответствует триггер маркера передачи, триггер буфера данных, триггер передачи. В процессе выдачи информации производится последовательная загрузка триггеров под управлением блока анализа управляющих слов. При этом каждому кааалу в области главной памяти соответствует свой набор управляющих слов, в которых находятся как слова, подлежащие передаче, так и управляющая информация. В процессе передачи под управлением блока анализа управляющих слов производится чтение.управляющих слов из главной памяти и пересылка их в блок анализа управляющих слов. Далее производится корректировка управляющих слов и пересылка их в главную память. Подобная операция производится при выдаче каждого битапо каждому из каналов.

Недостатками этого устройства являются ограниченные функциональные возможностиу так как при выдаче каждого бита по каждому из каналов производится чтение и запись управляющих слов в память процессора, что резко замедляет процесс передачи, снижая возможное количество обслуживаемых каналов и диапазон рабочих скоростей, а также препятствует выполнению более сложных алгоритмов по контролю информации и приоритетной выборке каналов, высокие аппаратурные затраты в пересчете на один обслуживаемый канал, так как все указанное оборудование используется для сравнительно небольшого числа кандлов.

Целью изобретения является сокращение оборудования и расширение функциональHbix возможностей за счет увеличения числа обслуживаемых каналов и диапазона рабочих скоростей передачи.

Поставленная цель достигается тем, что устройство, содержащее триггеры, дешифратор, блок коррекции контрольной суммы, шифратор, блок приоритета, блок управления, генератор импульсов, регистр адреса, причем выходы дешифратора соединены соответственно с первыми входами триггеров, вторые входы которых подключеньг к первому выходу блока коррекции контрольной суммы, выход блока приоритета соединен со входом шифратора, первый вход дешифратора подключен к выходу шифратора, второй вход дешифратора подключен к первому выходу регистра адреса, первый вход которого подключен к первому выходу генератора импульсов, второй выход которого соединен с первым входом блока управления, второй вход регистра адреса соединен с выходом блока сопряжения, входы которого соединены со входами устройства , блок сопряжения соединен двухсторонними связями с блоком управления, выходы триггеров подключены соответственно с выходам устройства, содержит блок памяти .синхронизации, блок памяти групп и блок памяти вывода, соединенный двухсторонними связями с блоком сопряжения., с блоком коррекции контрольной сум.мы и с блоком управления, входы блока памяти вывода подключены соответственно к первому выходу регистра адреса, к выходу шифратора и к перво.му выходу блока памяти синхронизации, который соединен двухсторонни.ми связями с блоком управления, входы блока памяти синхронизации подключены соответственно к выходу шифратора, к выходу блока сопряжения и к первому выходу регистра адреса, блок памяти групп соединен двухсторонними связями с блоком управления, входы блока памяти групп . соединены соответственно со вторым выходом регистра адреса и с выходом блока сопряжения, выход блока памяти групп подключен ко входу блока приоритета.

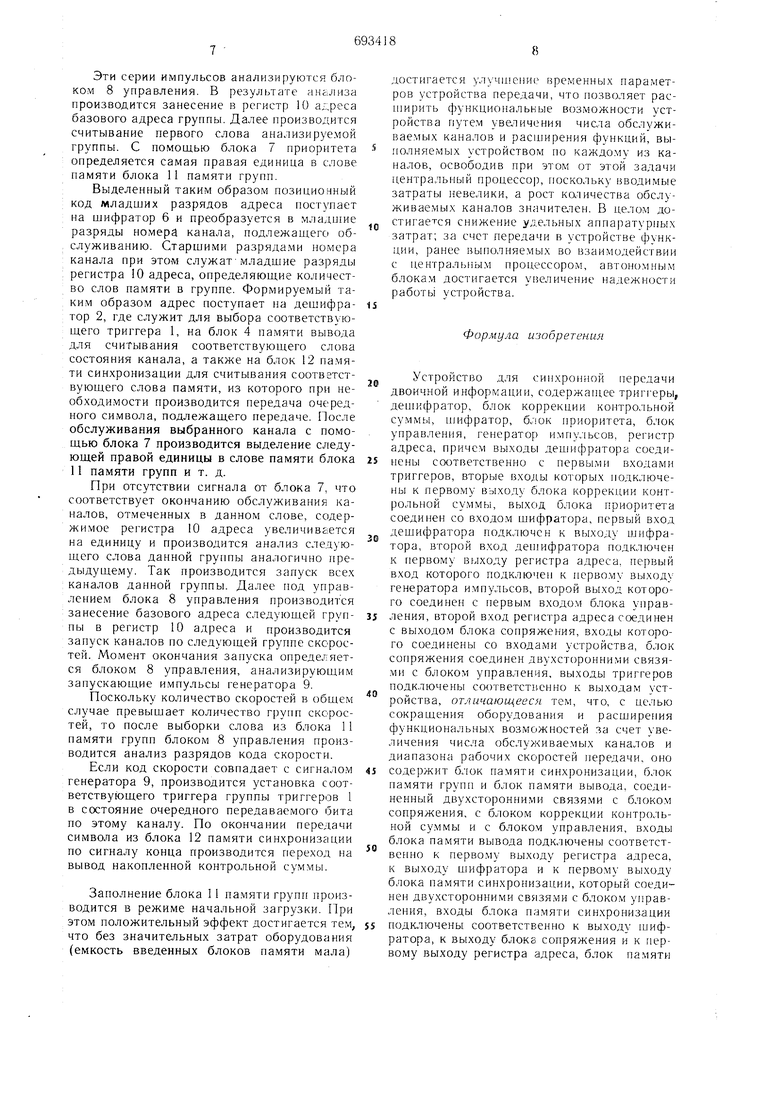

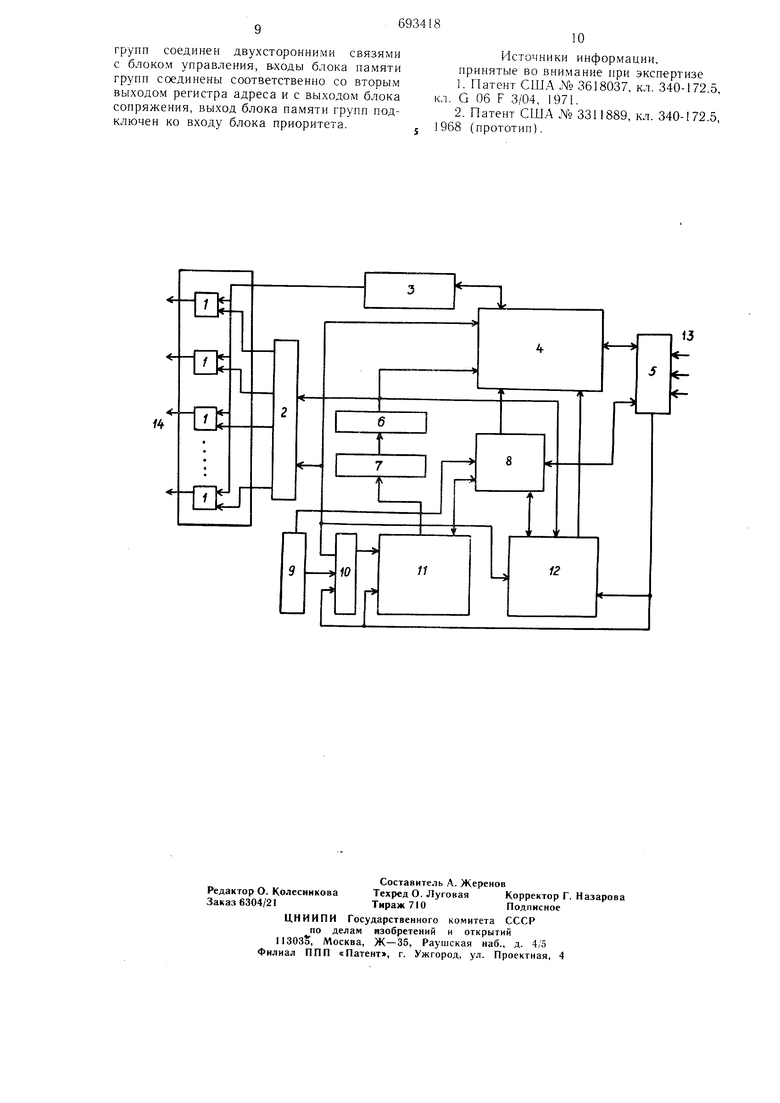

На чертеже представлена схема устройства.

Устройство содержит триггеры 1, служащие для запоминания Уровней сигналов, передаваемых в линии, дешифратор 2 для выборки линии связи, обслуживаемой в данный момент времени, блок 3 коррекции контрольной суммы, блок 4 памяти вывода, служащий для запоминания кодов символов, контрольных сумм, а также служебной информации по каждому каналу в процессе передачи, блок 5 сопряжения, служащий для сопряжения устройства с ЭВМ, шифратор 6, предназначенный для преобразования позиционнего кода номера канала внутри группы

в двоичный код номера канала, блок 7 приоритета, служащий для выбора старшего по номеру канала внутри анализируемой группы каналов, блок 8 управления, необходимый для координации работы всех блоков устройства, генератор 9 импульсов для формирования сигналов запуска устройства в работу, причем каждой скорости передачи соответствует свой сигнал таймера, регистр адреса 10, блок 11 памяти групп для приоритетного обслуживания каналов, блок 12 памяти синхронизации, необходимый для промежуточного запоминания кодов символов, подлежащих передаче в каналы связи, входы 13 и выходы 14 устройства.

Работа устройства заключается в соответствующем управлении триггерами 1, каждый из которых через модем или другое согласующее звено работает на линию связи.

При этом все линии связи обслуживаются в пневдопараллельном режиме одним оборудованием.

Поскольку информация, подлежащая передаче, поступает в устройство посимвольно, а в линии связи подается побитно, в устройстве производится ее запоминание. С этой целью в блоке 4 памяти вывода каждо му каналу соответствует своя ячейка памяти,. В этой ячейке хранится выводимый символ. После выдачи очередного бита производится сдвиг кода знака и начинается в.ывод следующего бита. В этой ячейке памяти также хранится код контрольной суммы, которая формируется по мере передачи символов и выдается вслед за последним символом в блоке подготовленном ЭВМ. Поскольку возможны различные виды контроля информации в линиях связи (наиболее часто встречаются циклический и матричный контроль), то способы формирования контрольной суммы различны. Общим моментом для всех видов контроля является то, что контрольная сумма накапливается, в процессе выдачи символов.

Правило, по которому, производится накопление контрольной суммы, задается блоком 3 коррекции контрольной суммы в зависимости от состояния разрядов типа контроля, которые также хранятся для каждого канала в ячейке блока 4 памяти вывода.

В ячейке блока 4 памяти вывода также хранится код скорости, определяющий момент окончания выдачи очередного бита передаваемого символа.

Устройство обеспечивает передачу информации по каждому каналу в широком диапазоне скоростей.

Таким образом в ячейке блока 4 памяти вывода хранится вся информация, характеризующая процесс передачи по данному каналу. При этом код символа заносится в ячейку оперативно по мере передачи, контрольная сумма также накапливается оперативно, а код скорости и тип контроля заносится в блок 4 памяти вывода в режиме начальной загрузки. Замена этой информации производится достаточно редкоари изменении параметров линии связи.

Поскольку режим работы с линиями связи имеет достаточно жесткий, синхронный характер, то для согласования устройства в момент перехода на передачу очередного символа с асинхронно работающей ЭВМ применяется буферное запоминание поступающих от ЭВМ символов в блоке 12 памяти синхронизации. Поступающие из блока 5 сопряжения символы и номер канала подаются в блок памяти синхронизации 12. При этом с помощью блока 8 управления производится коммутация на блок 12 памяти синхронизации выходов блока 5 сопряжения.

Ес,ти информация от ЭВМ отсутствует, блок 12 памяти синхронизации работает синхронно с блоком/4 памяти вывода по одним и тем же адресам. .По окончании передачи символа из блока 4 памяти выво0да производится перепись следующего символа, подлежащего передаче из блока 12 -памяти синхронизации, и генерируется запрос на следующий символ по данному каналу в блок 5 сопряжения. Для обеспечения работы устройства в широком диапазоне скоросSтей в нем применено приоритетное обслуживание каналов связи в зависимости от скорости их работы. Для этого служит блок 11 памяти групп, блок 7 приоритета и шифратор 6. Весь диапазонско ростей, обеспечи0ваемый устройством, разбит на 8 групп. Каждый канал может находиться в любой из групп и может иметь любую скорость внутри группы. В одной группе могут находиться каналы с различными, но соизмеримыми скоростями. При этом считается, что

$ интегральный поток информации, передаваемый устройством, остается неизменным, хотя соотношение скоростей работы каналов может меняться произвольно.

В соответствии с этим построен алгоритм

0 работы устройства при обслуживании каналов.

Каждой группе каналов в блоке 11 памяти групп выделена зона памяти, внутри которой каждому каналу выделен один бит паSмяти.

Каждый канал может находиться в любой группе. Принадлежность канала к данной группе определяется единичным состоянием соответствующего бита памяти внутри

O группы.

Выборка канала производится по сигналам генератора 9, который вырабатывает серии импульсов запуска с периодами, рав5ными длительностям одного бита информации в линиях связи для всех применяемых скоростей.

Эти серии импульсов анализируются блоком 8 управления. В результате анализа производится занесение в регистр 10 адреса базового адреса группы. Далее производится считывание первого слова анализируемой группы. С помощью блока 7 приоритета определяется самая правая единица в слове памяти блока И памяти групп.

Выделенный таким образом позиционный код младших разрядов адреса поступает на шифратор 6 и преобразуется в младшие разряды номера канала, подлежащего обслуживанию. Старшими разрядами номера канала при этом служатмладшие разряды регистра 10 адреса, определяющие количество слов памяти в группе. Формируемый таким образом адрес поступает на дешифратор 2, где служит для выбора соответствующего триггера 1, на блок 4 памяти вывода для считывания соответствующего слова состояния канала, а также на блок 12 памяти синхронизации для считывания соответствующего слова памяти, из которого при необходимости производится передача очередного символа, подлежащего передаче. После обслуживания выбранного канала с помощью блока 7 производится выделение следующей правой единицы в слове памяти блока 11 памяти групп ит. д.

При отсутствии сигнала от блока 7, что соответствует окончанию обслуживания каналов, отмеченных в данном слове, содержимое регистра 10 адреса увеличивается на единицу и производится анализ следующего слова данной группы аналогично предыдущему. Так производится запуск всех каналов данной группы. Далее под управлени ем блока 8 управления производится занесение базового адреса следующей группы в регистр 10 адреса и производится запуск каналов по следующей группе скоростей. Момент окончания запуска определяется блоком 8 управлений, анализирующим запускающие импульсы генератора 9.

Поскольку количество скоростей в общем случае превышает количество групп скоростей, то после выборки слова из блока 11 памяти групп блоком 8 управления производится анализ разрядов кода скорости.

Если код скорости совпадает с сигналом генератора 9, производится установка соответствуЬЩего триггера группы триггеров 1 в состояние очередного передаваемого бита по этому каналу. По окончании передачи символа из блока 12 памяти синхронизации по сигналу конца производится переход на вывод накопленной контрольной суммы.

Заполнение блока 11 памяти групп производится в режиме начальной загрузки. При этом положительный эффект достигается тем, что без значительных затрат оборудования (емкость введенных блоков памяти мала)

достигается улучшение временных параметров устройства передачи, что позволяет расширить функциональные возможности устройства путем увеличения числа обслуживаемых каналов и расширения функций, выполняемых устройством по каждому из каналов, осбободив при этом от этой задачи центральный процессор, поскольку вводимые затраты невелики, а рост количества обслуживаемых каналов значителен. В целом достигается снижение удельных аппаратурных затрат; за счет передачи в устройстве функции, ранее выполняемых во взаимодействии с центральным процессором, автономным блокам достигается увеличение надежности pa6oTbi устройства.

Формула изобретения

Устройство для синхронной передачи двоичной информации, содержащее триггеры, дешифратор, блок коррекции контрольной суммы, шифратор, блок приоритета, блок управления, генератор импульсов, регистр адреса, причем выходы дешифратора соединены соответственно с первыми входами триггеров, вторые входы которых подключены к первому выходу блока коррекцииконтрольной суммы, выход блока приоритета соединен со входом шифратора, первый вход дешифратора подключен к выходу шифратора, второй вход дешифратора подключен К перйому выходу регистра адреса, первый вход которого подключен к первому выходу генератора ,импульсов, второй выход которого соединен с первым входом блока управления, второй вход регистра адреса соединен с выходом блока сопряжения, входы которого соединены со входами устройства, блок сопряжения соединен двухсторонними связями с блоком управления, выходы триггеров подключены соответственно к выходам устройства, отличающееся тем, что, с целью сокрашеНия оборудования и расширения функциональных возможностей за счет увеличения числа обслуживаемых каналов и диапазона рабочих скоростей передачи, оно содержит блок памяти синхронизации, блок памяти групп и блок памяти вывода, соединенный двухсторонними связями с блоком сопряжения, с блоком коррекции контрольной суммы и с блоком управления, входы блока памяти вывода подключены соответственно к первому выходу регистра адреса, к выходу шифратора и к первому выходу блока памяти синхронизации, который соединен двухсторонними связями с блоком управления, входь блока памяти синхронизации подключены соответственно к выходу шифратора, к выходу блока сопряжения и к первому выходу регистра адреса, блок памяти

групп соединен двухсторонними связями с блоком управления, в-ходы блока памяти групп соединены соответственно со вторым выходом регистра адреса и с выходом блока сопряжения, выход блока памяти групп подключен ко входу блока приоритета.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3618037, кл. 340-172.5, кл. G 06 F 3/04, 1971.

2.Патент США № 3311889, кл. 340-172.5, 1968 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Многоканальное устройство для сопряжения | 1985 |

|

SU1282142A1 |

| Мультиплексный канал | 1979 |

|

SU922713A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

Авторы

Даты

1979-10-25—Публикация

1976-12-03—Подача