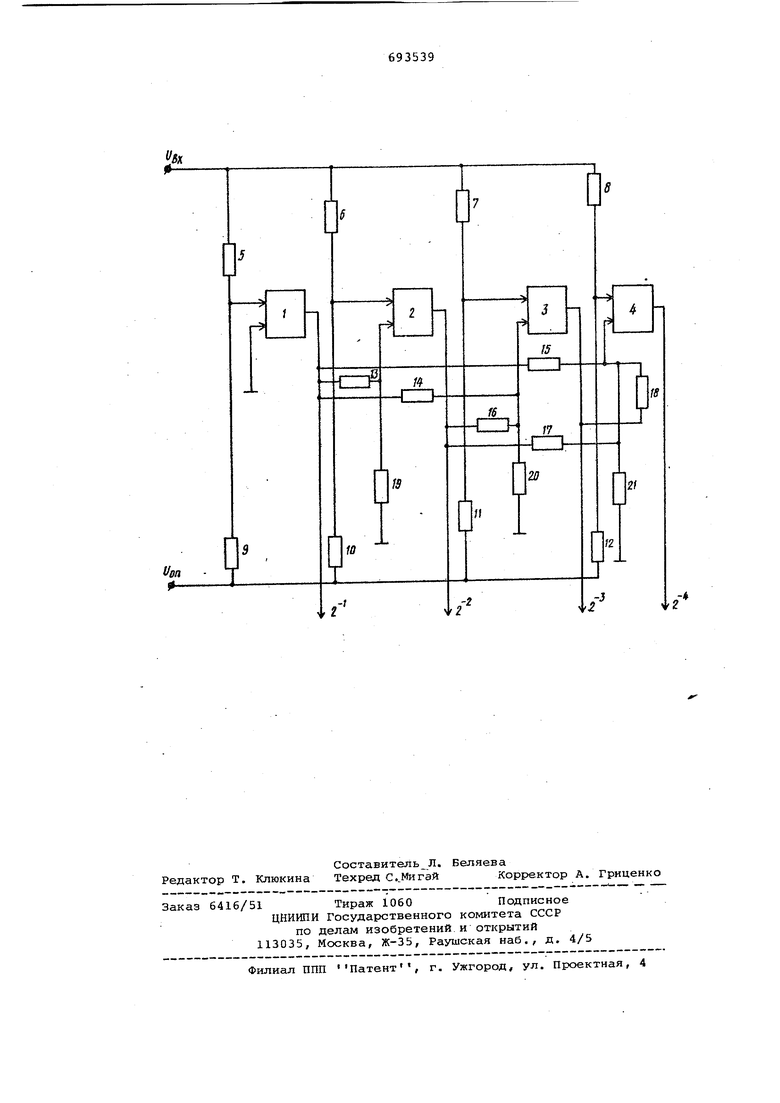

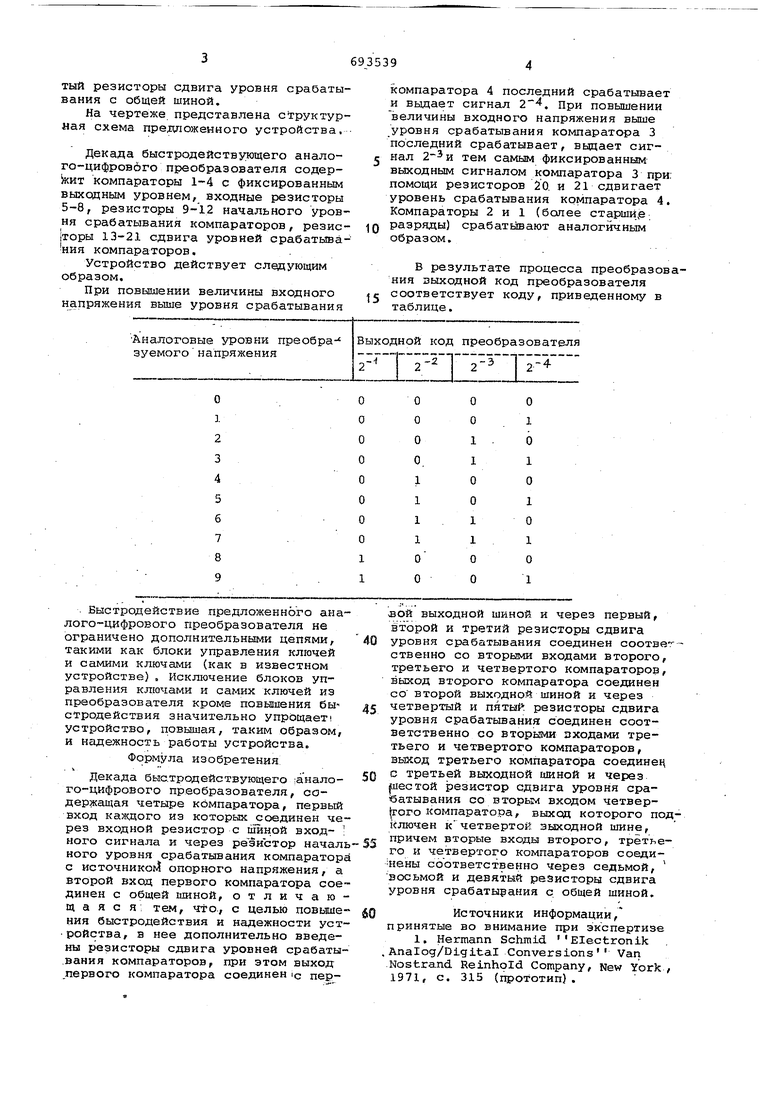

Изобретение относится к приборос ению и предназначено для использова в качестве преобразовательного каскада в быстродействующих аналого-ци ровых преобразователях, измерительных приборах и системах автоматичес кого управления и контроля. Известна декада быстродействующего аналого-цифрового преобразозат ля, содержащая компараторы, источни опорного напряжения, резисторы начал ного уровня срабатывания компараторов, входные резисторы, ключи и блок управления работой ключей .для измен ния уровней срабатывания компарато ров 1 . Однако это устройство имеет низкое быстродействие за счет задержек в схемах управления ключами ив самих ключах, а также сложную и детале емкую схему, что снижает надежность работы устройства. Целью изобретения является повышение быстродействия и надежности устройства. Это достигается тем, что в декаду быстродействующего аналого-цифрового преобразователя, содержащую четыре компаратора, первый вхся каж, дого из которых соединен через входной резистор с шиной входного сигнала и через резистор начального уров.ня срабатывания компаратора с источником опорного напряжения, а второй вход первого компаратора соединен с общей шиной, дополнительно введены .резисторы сдвига уровней срабатывания компараторов,при выход первого компаратора соединен с первой выходной шиной и через первый, второй и третий резисторы сдвига уровня срабатывания соединен соответственно со вторьели входами второго, третьего и четвертого компараторов, выход второго компаратора соединен со второй выходной шиной и че,рез четвертый и пятый резисторы сдвига уровня срабатывания соединен соответственно со вторыми входами третьего и четвертого компараторов, выход третьего компаратора соединен с третьей выходной шиной и через шестой резистор сдвига уровня срабатывания со вторым входом четвертого компаратора i выход которрго подключен к четвертой выходной шине, причем вторые входы второго,, третьего и четвертого компараторов соединены соответственно чедез седьмой, восьмой и девятый резисторы сдвига уровня срабатывания с общей шиной. На чертеже представлена структурная схема предложенного устройства. Декада быстродействующего аналого-цифровбго преобразователя содерkHT компараторы 1-4 с фиксированным выхсдным уровнем, входные резисторы 5-8, резисторы 9-12 начального уров ня срабатывания компараторов, резис торы 13-21 сдвига уровней срабатыва ния компараторов. Устройство действует следующим образом. При повышении величины входного напряжения выше уровня срабатывания компаратора 4 последний срабатывает и выдает сигнал 2. При повышении величины входного напряжения выше уровня срабатывания компаратора 3 последний срабатывает, вьщает сигнал тем самым фиксированным выходным сигналом компаратора 3 при; помощи резисторов 20. и 21 сдвигает уровень срабатывания компаратора 4. Компараторы 2 и 1 (более старшйэ. разряды) срабатывают аналогичным образом. В результате процесса преобразования выходной код преобразователя соответствует коду, приведенному в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательно-параллельный аналого-цифРОВОй пРЕОбРАзОВАТЕль C КОРРЕКциЕйпОгРЕшНОСТи | 1977 |

|

SU834900A2 |

| Последовательно-параллельный аналого-цифровой преобразователь с коррекцией погрешности | 1976 |

|

SU702513A1 |

| Аналого-цифровой преобразователь параллельного действия | 1975 |

|

SU687586A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1239863A1 |

| Многоканальный аналого-цифровой преобразователь | 1987 |

|

SU1444945A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1152088A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

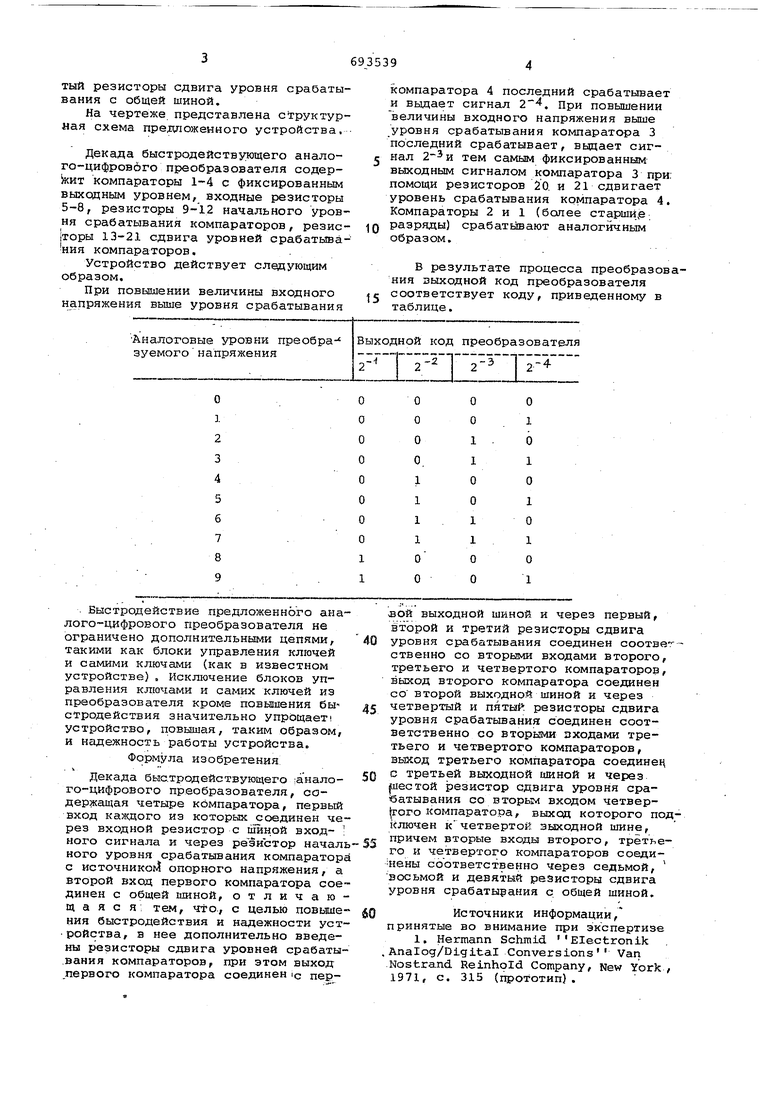

О

1 2 3 4 5 б 7 8 9 . Быстродействие предложенного аналого-цифрового преобразователя не ограничено дополнительными цепями, такими как блоки управления ключей и самими ключами (как в известном устройстве). Исключение блоков управления ключами и самих ключей из преобразователя кроме повышения быстродействия значительно упрощает устройство, повышая, таким образом, и нгщежность работы устройства. Формула изобретения. Декада быстродействующего .зналого-цифрового преобразователя, содержащая четыре компаратора, первый вход каж;цого из которых Jcoeдинeн че рез входной резистор с шиной вход- него сигнала и через резистор начал ного уровня срабатывания компаратор с иcтoчникo l опоргюго напряжения, а второй вход первого компаратора сое динен с общей шиной, отличаю щаяся: тем, что., с целью повьше ния быстродействия и надежности уст ройства, в нее дополнительно введены резисторы сдвига уровней срабаты.вания компараторов, при этом выход .первого компаратора соединенic перо

о о о

о о 1 1 о о 1 1 о о

1

о 1 о 1 о 1 о 1

0.

1

1

1

1

о

о ,вой выходной шиной и через первый, второй и третий резисторы сдвига уровня срабатывания соединен соотве ственно со вторыми входами второго, третьего и четвертого компараторов, выход второго компаратора соединен со второй выходной шиной и через четвертый и пяты, резисторы сдвига уровня срабатывания соединен соответственно со вторыми входами третьего и четвертого компараторов, выход третьего компаратора соедине с третьей выходной шиной и через шестой резистор сдвига уровня срабатывания со BTopbiM входом четвер|гого .компаратора, выход которого подключен кчетвертой выходной шине, причем вторые входы второго, третьего и четвертого компараторов соединены соответственно через седьмой, восьмой и девятый резисторы сдвига уровня срабатывания с общей шиной. Источники информации, принятые во внимание при экспертизе 1. Hermann Schmid Electronik Analog/Digital Conversions Van Nostrand Reinhold Company, New York , 1971, c. 315 (прототип).

Авторы

Даты

1979-10-25—Публикация

1973-11-05—Подача