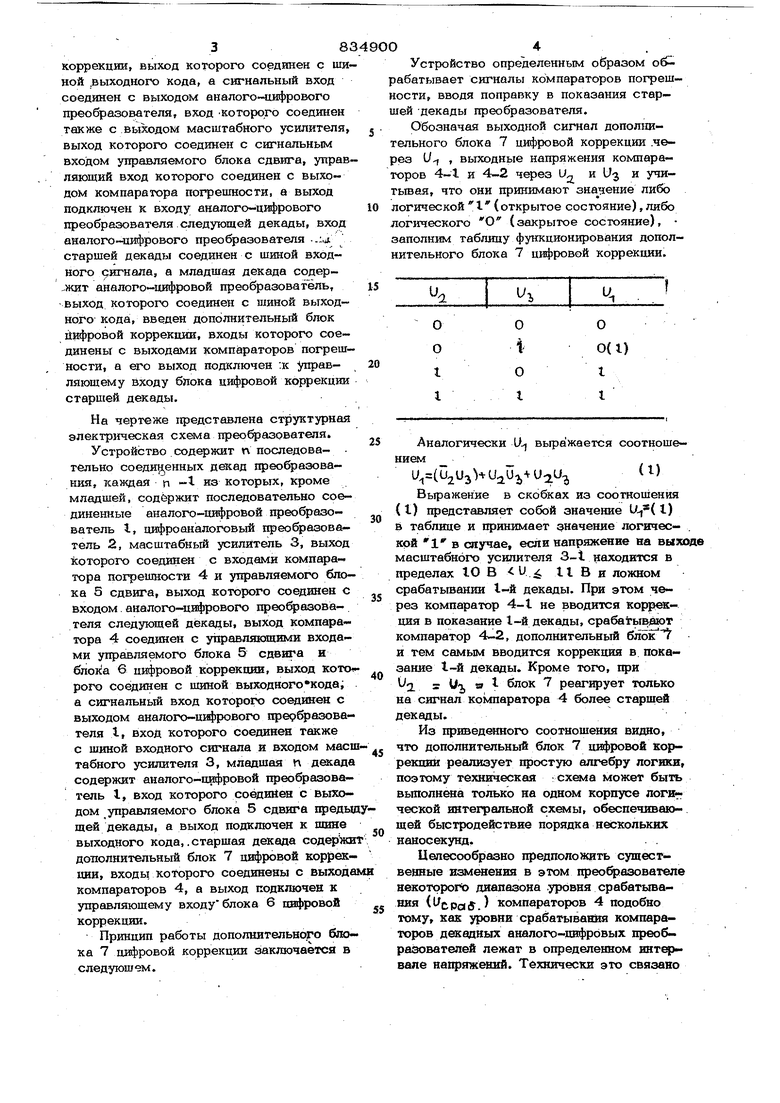

коррекции, выход которого соединен с ши ной .выходного кода, а сигнальный вход соединен с выходом аналого-цифрового преобре13ователя, вход Которого соединен также с выходом масштабного усилителя, выход которого соединен с сигнальным входом управляемого блока сдвига, управ ляющий вход которого соединен с выходом компаратора погрешности, а выход подключен к входу аналого-цифрового преобразователя следующей декады, вход аналого-цифрового преобразователя ..;а старшей декады соединен с шиной входного игнала, а младшая декада содер-жит аналого-цифровой преобразователь, - выход которого соединен с шиной выходного кода, введен дополнительный блок йифровой коррекции, входы которого соединены с выходами компараторов погрешности, а его выход подключен .к управляющему входу блока ци)ровой коррекции старшей декады. На чертеже гфедставлена структурная электрическая схема преофазователя. Устройство содержит п последова- тельно соеди11,енных декад преобразования, тсанодая и -1 из которых, кроме младшей, содержит последовательно соединенные аналого-цифровой преобразователь 1, цифроаналоговый преобразователь 2, масштабный усилитель 3, выход которого соединен с входами компаратора позтрешности 4 и управляемого блока 5 сдвига, выход которого соединен с входом аналого-цифрового преофазователя следующей декады, выход компаратора 4 соединен с у1фавляющту1и входами управляемого блока 5 сдвига и блок1а 6 цифровой коррекции, выход которого соединен с шиной выходного кода; а сигнальный вход которого соединен с выходом аналого-цифрового прербразователя I, вход которого соединетс также с шиной входного сигнала и входом масш табного усилителя 3, младшая п декада содержит аналого-цифровой преобразователь I, вход которого соедийен с Выходом управляемого блока 5 сдвига преды щей декады, а выход подключен к шиае выходного кода, .старшая декада содержн дополнительный блок 7 цифровой коррекции, входы, которого соединены с выхода компараторов 4, а выход подключен к управляющему входу блока 6 цифровой коррекции. Принцип работы дополнительного блока 7 цифровой коррекции заключается в следующем. Устройство определенным образом об абатывает сигналы компараторов погрешности, вводя поправку в показания старшей -декады преобразователя. Обозначая выходной сигнал допол1штельного блока 7 цифровой коррекции .через (J , выходные напряжения компараторов 4-1 и 4-2 через и и и учитьгоая, что они принимают зна нение либо логической 1 (открытое состояние), либо логического О (закрытое состояние), заполним таблицу функцион1фования дополнительного блока 7 цифровой коррекции. Аналогически 1Ц вьфажается соотношениемU,(U2U3HU.iUo, Вьфажение в скобках из соотношения ( I) представляет собой значение U-,( I) в таблице и принимает значение логической I в случае, если напряжение на выходе масштабного усилителя 3-t находится в пределах Ю В U II В и ложном срабатывании 1-й декады. При этом через компаратор 4-1 не вводится коррекция в показание 1-й декады, срабатывают компаратор 4-2, дополнительный и тем самьм вводится коррекция в показание 1-й декады. Кроме того, при UT, я блок 7 реагирует только на сигнал компаратора 4 более старщей декады. Из приведенного соотношения видао, что дополнительный блок 7 цифровой коррекцн реализует простую алгебру логгаш, поэтому техническая : схема может быть вьтолнена только на одном корпусе логической интегральной ск&лы, обеспечивающей быстродействие порядка нескольких наносекунд.. . Целесообразно предположить существенные взмененвя в этом преофазователе некоторого диапазона .уровня срабатывания ( У t Ря (У. компараторов 4 подобно тому, как уровни срабатывания компараторов декадных аналого-цифровых преобразователей лежат в определенном интервале натфнжений. Технически это связано со значительным упрощением сложной чувствительных компаратор-IB 4 и повышением быстродействия всего устройства. Выберем диапазон срабатывания компараторов 4, удовлетворяющий неравенет ву lOB Ucpa5$llB(2) Проиллюстрируем работу предлагаетлог поспедовательно-лараллельного аналогоцифрового прео азователя с коррекцией погрешности на численном примере. Пусть на шину входного сигнала преобразователя поступает преобразуемое напряжение 0 «ь2,013В и компаратор уровня 2 в декадном аналого- Еифровом преобразователе 1-1 срабатвает только при уровне 2,3 В. В результате на выходе преобразователя 1-1 мы будем иметь показание I, напряжение на выходе масштабного усилителя 3-1 (2,O13-1) S 10,13 В. Предположим что из-за неточности порога срабатывания компаратора 4-1 последний срабатывает при уровне 1О,4В В таком случае выходное напряжение управляемого блока 5 сдвига повторяет выходное напряжение масштабного усилителя 3-1, при входном напряжении Ю, 13 В1 в .аналого-цифровом гфеобразователе 1-2 срабатывает компаратор уровня 9 и показание на шине выходного кода блока 6-2 цифровой коррекции равно 9-.ТИ.. При этом напряжение на выходе масш табного усилителя 3-2 U atO(lO,l3-9 -11,3 В и, так как 11,3 В II В, то срабатывает компаратор 4-2, выходное напряжение дополнительного блока 7 цвф ровой коррекции повторяет сигнал компа- ратора 4-i2 и посредством блока 6-11 коррекции в показание аналого-цифрового прео азователя I-t вводится коррекция l+ls2, а при помощи блока 6-2 коррекцви в показание аналого-цифрового пр&обраэователя 1-2 вносится поправка 94-1а(1)0. Одновременно при помощи управляемого блока 5-2 сдвига на вход аналого-цифрового преобразователя 1-3 поступает напряжение (У -11,3 - tOa а 1,3 В. В зависимости от уровней срабатывания компараторов в аналого-цифровом преобразователе 1-3 показание на его выходе будет равно I или О, а показание устройства при входном напряжении UK 2,013 В в целом 201 или 200, полученная погрешность показания равна погрешности дискретности преофазования преобразователя. В предложенном аналого-цифровом 1реофазователе система коррекции погрешности допускает небольшую неточность уровней срабатывания компараторов, что достигается введением в схему устройства дополнительного блока цифровой коррекции, включенного в неточные цепи анало- го- цйфрового преобразователя. Техническая реализация решения щгаста, так как дополнительный блок цифровой коррекции погрешности может быть вьшолнен только на одном корпусе логической интегральной ск&лы, -Обеспечивающей быстро1ействие порядка нескольких наносекунд, тогда как в известном устройстве требук тся компараторы, которые должны обеспечить высокую точность, чувствительность и быстродействие, что является сложной проблемой. Формула изобретения Последовательно-параллельный аналого-цифровой щзеобразователь с коррекцией погрешности по авт. св. № 702513, о т)1ич ающийся тем, что, с целью повышения точности и упрощения устройства, в него введен дополнительный блок цифровой коррекции, входы которого соедине1б ы с выходами погрешвостн компараторов,а его выход подключен к управляющему входу цифрового блока коррекции старшей декады. Источники информации, принятые во внимание при экспертизе I. Авторское сввдетельство СССР №,702513, кл. Н 03 К 13/175, 2О.03.78 (прототип).

1

И//

I

ЬВш

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательно-параллельный аналого-цифровой преобразователь с коррекцией погрешности | 1976 |

|

SU702513A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Декада быстродействующего аналогоцифрового преобразователя | 1973 |

|

SU693539A1 |

| Измерительный преобразователь для тензорезисторных весоизмерительных устройств | 1990 |

|

SU1830463A1 |

| Аналого-цифровой преобразователь параллельного действия | 1975 |

|

SU687586A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1695499A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Адаптивный аналого-цифровой преобразователь | 1972 |

|

SU493019A1 |

| Устройство для централизованного контроля | 1974 |

|

SU652570A2 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

Авторы

Даты

1981-05-30—Публикация

1977-07-01—Подача