(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРЕРЫВАНИЕМ ПРОГРАММ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления прерыванием программ | 1981 |

|

SU962950A1 |

| Устройство для прерывания программ | 1978 |

|

SU736101A1 |

| Многоканальное устройство дляпРЕРыВАНия пРОгРАММ | 1979 |

|

SU811257A1 |

| Устройство для прерывания программ | 1978 |

|

SU744575A1 |

| Многоканальное устройство приоритета | 1989 |

|

SU1686444A1 |

| Многоканальное устройство приоритета | 1986 |

|

SU1417001A1 |

| Устройство приоритетного прерывания | 1990 |

|

SU1765827A1 |

| Устройство прерывания программ | 1983 |

|

SU1119015A1 |

| Устройство переменного приоритета с шифрацией адреса | 1984 |

|

SU1234837A1 |

| Устройство для обслуживания запросов | 1982 |

|

SU1109753A1 |

I

Изобретение относится к области вычислитепьной техники и может быть испопьзовано в мультипрограммных вычислвтепьных системах.

Известны устройства прерывания программ, содержащие регистры, блок анализа приоритетов, регистр масок и реализующее прерывание программы в вычислительной маш1ше при поступлении запроса с более высоким приоритетом, чем приоритет решаемой задачи 1.

Недостаток известных устройств заключается в ограниченных функциональных возможностях, исключающих юс применение в мультипрограммных системах.

Наиболее близким к данному по технической сущности является устройство, содержащее регистр запросов, вход которого являетсй информационным входом устройства, дешифратор приоритета запроса, подключенный вькодами к соответствуюшим входам памяти очередей запросов, управляющий вход которой является первым входом устройства.

вторым и третьим входами подключенного соответственно ко входам узла синхронизации и регистра масок, выходы которых соединены с соответствующими управпякяцими входами элементов И первой группы, подключенными выходом ко входу узла приоритета запросов, и элемент ИЛИ, выходом соединенный с управляющим выходом устройства 2,

Недостаток этого устройства состоитв его ограниченных функциональных возможностях, вследствие чего оно не может, быть использовано, в вычислительных системах, работающих в реальном масщтабе времени и решающих одновременно несколько задач,

Ыелью изобретения является расширение функциональных возможностей устройства за счет учета приоритета решаемых в каждый момент задач и выработки сигналов прерывания только в случае, если приоритет поступившего запроса соответствует задаче с более высоким приоритетом, чем приоритет хотя бы одной решаемой задачи.

Это достигается тем, что в устройство введены вторая группа элементов И, соединенная первым и вторым входами соответственно -с выходом регистра запросов и первым управляющим выходом узла синхронизации, шифратор приоритета решаемых задач, дешифратор коррекции и по числу одновременно решаемых задач регистры приоритета запроса, схемы сравнения приоритетов и регистры 11рйоритета раздела, причем второй управ/шюший выход узла синхронизации и вьвсод элемента ИЛИ соединены с соответствующими управлякицими входами шифратора приоритета решаемых задач, выход узла приори та запросов -нряключей к первому входу схем сравнения, вторые входы которых через соответствующие регистры приоритета запроса подключены к соответствующим выходам шифратора приоритета решаемых задач, вход которого подключен к выходу узла приоритета запросов, а входы из группы информационных входов соединены с выходами соответствующих регистров приоритета раздела, первыми входами соединенных с первым входом устройства, а вторыми входами - с выходом дешифратора коррекции, входы которого подключены к выходам соответствующих схем сравнения приоритетов и.соответствукшим входам элемента ИЛИ, выходы регистров приоритета раздела являются соответствующими вьDco aми устройства, выходы памяти очередей запросов подключены к соответствующим входам элементов И первой группы.

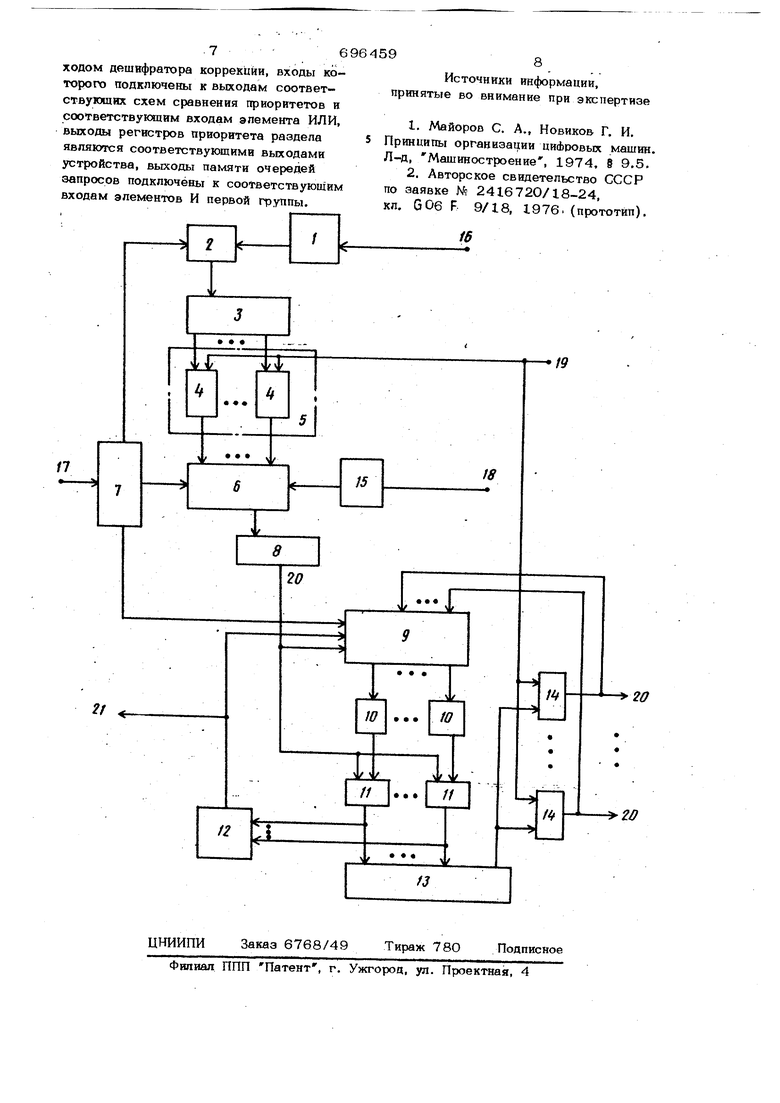

На чертеже представлена блок-схема устройства. Устройство содержит регистр 1 запросов, TpJ-nny элементов И 2, дешифратор 3 приоритета запроса, регистры 4 для хранения очереди для каждого приоритета запроса, образующие память 5 очередей запросов, группу . элементов И 6, узел 7 синхронизации узел 8 приоритета запросов, шифратор 9 приоритета решаемьк задач, регистры Ю приоритета запроса, схемы И сравнения пршритетов, элемент ИЛИ t2, дешифратор 13 адреса прерывания, регистры 14 приоритета раздела, регистр 15 масок, информационный вход 16, второй 17, третий 18 и первый 19 входы устройства, выход 20 и управляющий выход 21 устройства.;

Устройство работает следующим образом.

По информационному входу 16 в регистр 1 вводится фрагмент поступившего в память системы сообщения, содержащий код номера приоритета данного запроса. По сигналу из узла 7 через группу элементов И 2 этот код подается на дешифратор 3, на одном из выходов которого появляется сигнал . Каждый выход дешифратора 3 соответствует одному и только одному фиксированному номеру приоритета. Выдаваемые дешифратором 3 сигналы записываются в регигтры 4 так, что число, содержащееся в 4, в любой момент времени в точности равно количеству необслуженных запросов, т.е. содержимое отдельного регистра 4 хранит очередь запросов заданного приоритета. По сигналу из узла 7 через группу элементов И . на вход узла 8 поступают сигналы от всех незамаскированных кодом регистра 15регистров 4, находящихся в ненулевом состоянии. Узел 8 выделяет старшую по приоритету очередь и формирует соответствующий сигнал на вход схем 11 сравнения. В регистрах Ю хранятся приоритеты обрабатываемых в текущий момент времени запросов. Число регистров 10 соответствует числу одновременно обслуживаемых запросов (решаемых задач) системы. Каждая схема 11 сравнивает номер приоритета поступившего запроса с номером, хранящимся в регистре 10, и в случае, если номер поступившего запроса оказывается больше номера, хранящегося в регистре Ю, формирует на своем выходе сигнал. Появление сигнала на выходе одной схемы 11 свидетельствует о том, что приоритет поступившего запроса выше приоритета одИой из обрабатываемых в текущий момент времени задачи, и на выходе элемента ИЛИ 12 и управляющем выходе 21 устройства появляется, сигнал прерывания. С выходов дешифратора 13 в зависимости от набора сигналов, поступивших с выхода схем 11 сравнения, на входы регистров 14, хранящих приоритеты разделов пакшти системы, в которых размещены решаемьге задачи, поступают соответствующие сигналы. .Набор этих сигналов готовит запись новых приоритетов разделов, учитывающих приоритет поступившего запроса. В частности, обработка поступившего запроса будет осуществляться в разделе, содержащем задачу наинизшего приоритета среди решаемых в текущий момент Задач. Однако приорите новой задачи может быть выше приоритетов других ракаемых задач. Поэтому поступление каждой новой задачи требует изменения приоритета на единицу всех разделов, в которых обрабатываются запросы, приоритет которых ниже поступившего. Пусть, например число разрядов каждого регистра t4 равно числу разделов, и номер приоритета задается поэиционно, т.е. в каждом регистре имеется не более одного единичiHoro разряда. Тогда номер единичного ; разряда соответствует номеру приоркте;та. Если дешифратор 13, в зависимости от числа поступивших на Ход сигналов, возбуждает одни из своих выходов, то номер этого выхода будет характеризовать число младших разрядов, которые должны быть сдвинуты в регистрах 14. Естественно что при этом изменяется состояние только тех регистров 14, в которых единичный разряд находится в числе сдвигаемых. Поступление каждого нового запроса вызывает выпо тение описанного процесса, в результате которого происходит анализ приоритета поступившего запроса и Подготовка прерывания програмлФы решения задачи, находящейся в одном из разделов памяти системы. Если приоритет поступившего запроса ниже приоритетов решаемых в данный момент задач то выаоаы схем 11 не возбуждаются, и сигнал прерывания не вырабатывается. Сигнал прерывания управляющем выходе 21 сигнализирует только о необходимости прерывания процесса обработки и инициирует работу программы прерывания системы. По завершении работы этой программы па первый вход 19 устройства поступает сигнал, по которому .собственно происходит изменение состояния регистров 14 и изменение на единицу очереди эапросов в соответствующем регистре 4. После изменения состояния регистров 14 по сигналу узла 7 происходит изменение состояний регистров Ю в результате чего на входы схем 11 по даются новые коды, снимающие сигналы прерывания на управлякмпем выходе 21 устройства. Таким образом, устройство обеспечивает анализ немасированных приорите- : тон запросов, ожидаюших обслуживания, и немедленную передачу на офаботку 6 96 старших по приоритету запросов. При этом устройство учитывает приоритеты всех решаемых в текущий момент задач, что дает возможность его использования в мультипрограммных вычислительных системах. Формула изобретения . Устройство для управления прерыванием программ, содержащее регистр запросов, вход которого является Егаформационным входом устройства, дешифратор приоритета запроса, подключенный выходами к соответствующим выходам памяти очередей запросов, управляющий вход которой является первым входом устройства, вторым и третьим входами подключенного соответственно ко входам узла синхронизации и регистра масок, выходы которых соединены с соответствующими управляющими входа те элементов И первой группы, подключевиой выходом ко входу узла приоритета запросов, элемент ИЛИ, выходом соединенный с управляющим выходом устройства, отличающееся тем, чтч,. с целью расширения функциональных возможностей устройства за счет учета . приоритетов решаемых системой задач, в устройство введены вторая группа элементов И, соединенных первыми н вторыми входами соответственно с выходом регистра запросов и первым управляющим выходом узла сгаосронизацви, шифратор приоритета решаемых задач, дешифратор коррекции и по числу одновременно решаека.1Х задач регистры приоритета запроса, схемы сравнения приоритетов и регистры приоритета раздела, причем второй управляющий узла С1шхронизации н выход элемента ИЛИ соединены с соответствующими управляющими входами шифратора приоритета решаемых задач, выход узла приоритета запросов подключен к первому входу схем сравнения, вторые входы которых через соответствующие регистры приоритета запроса подключены к соответствующим входам ши||фатора приоритета рщцаемых задач, вход которого подключен к выходу узла приоритета запросов, а входы из группы информационных входов соединены с выходами соотрет- ствуюших регистров приоритета раздела, первыми вход&ми соединенных с первым входом устройства, а вторыми - с вы- ,

ходом дешифратора коррекции, входы которого подключены к выходам соответствующих схем сравнения приоритетов и соответствующим входам элемента ИЛИ, выходы регистров приоритета раздела являются соответствующими выходами устройства, выходы памяти очередей запросов подключены к соответствующим входам элементов И первой группы.

Источники информации, принятые во внимание при экспертизе

кл. G06 F 9/18, 1976. (прототип).

Авторы

Даты

1979-11-05—Публикация

1976-11-15—Подача