(21)4101916/24-24

(22)05.05.86

(46) 15.08.88. Бюл. № 30

(72) Г.А.Викторов, Л.П.Коршунов,

А.Б.Антонов и А.В.Аношкин

(53)681.325(088.8)

(56)Авторское свидетельство СССР № 1288698, кл. G 06 F 9/46, 1985.

: Авторское свидетельство СССР № 1315977, кл. G 06 F 9/46, 1986.

(54)МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА

(57)Изобретение относится к вычислительной технике и может быть использовано для динамического управления обработкой заявок в ЭВМ.с мультипрограммным режимом работы, а также в системах распределенной обработки данных при обработке запросов и сообщений.. Цель изобретения - расширение области применения за счет возможности кратковременного подключения низкоприоритетных запросов

при наличии высокоприоритетных. Устройство содержит шифраторы, кoм fyтa- торы, элементы НЕ, И, И-НЕ, схемы сравне шя, узел приоритета, дешифратор, счетчики, триггеры. Устройство решает поочередное отрабатьшарше до 7 циклов по одному кванту каждого запроса независ1-1мо от его уровня приоритета,. При этом подсчет квантов обеспечивается счетчиками; группа схем сравнения и группы коммутаторов осуществляют поочередное включение запросов о При достижении числа отработанных квантов, равного 7, устройство передает управление узлу приоритета, который организует полную отработку поступивших запросов в зависимости от установленных уровней приоритета. Устройство позволяет за счет динамического изменения видов приоритета осуществлять более оперативную обработку запросов, требующих определенного количества квантов решения процессора. 1 ил.

а S

(Л

4

Изобретение относится к вычислительной технике и oжeт быть исполь- зовано для управления обработки зая- тзок в ЭВМ с мультипрограммным режи- :мом работы, а также в системах рас- 1пределенной обработки данных при обработке запросов и сообщений.

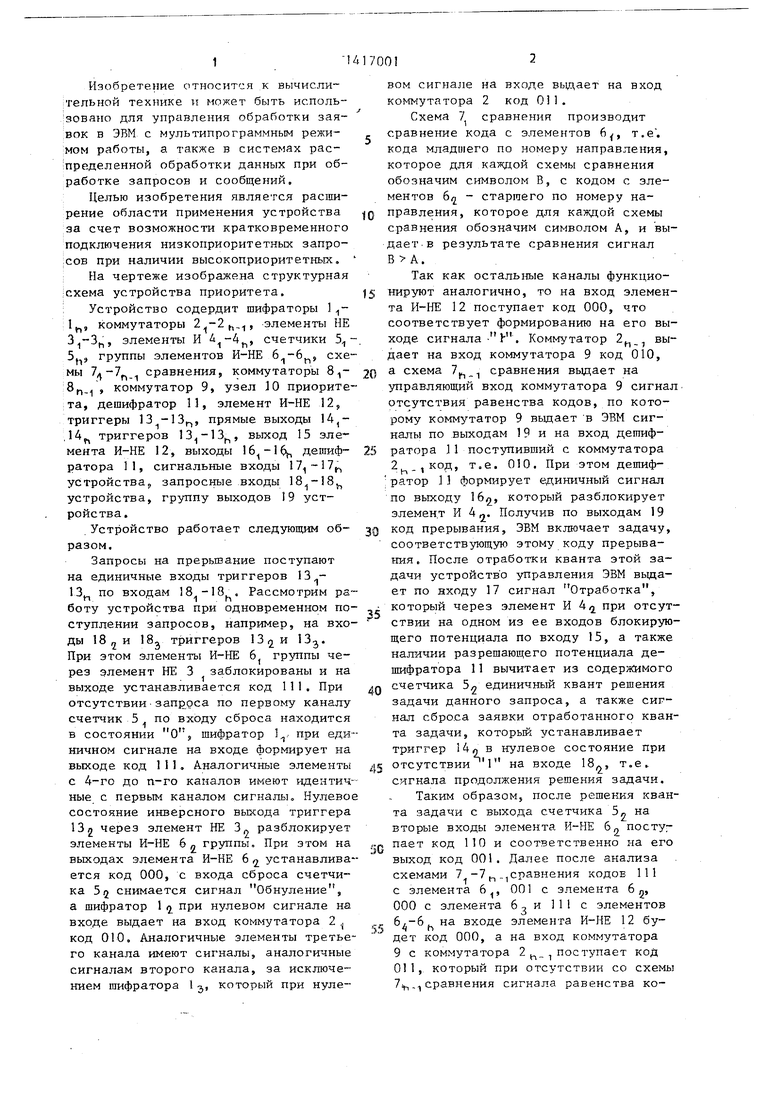

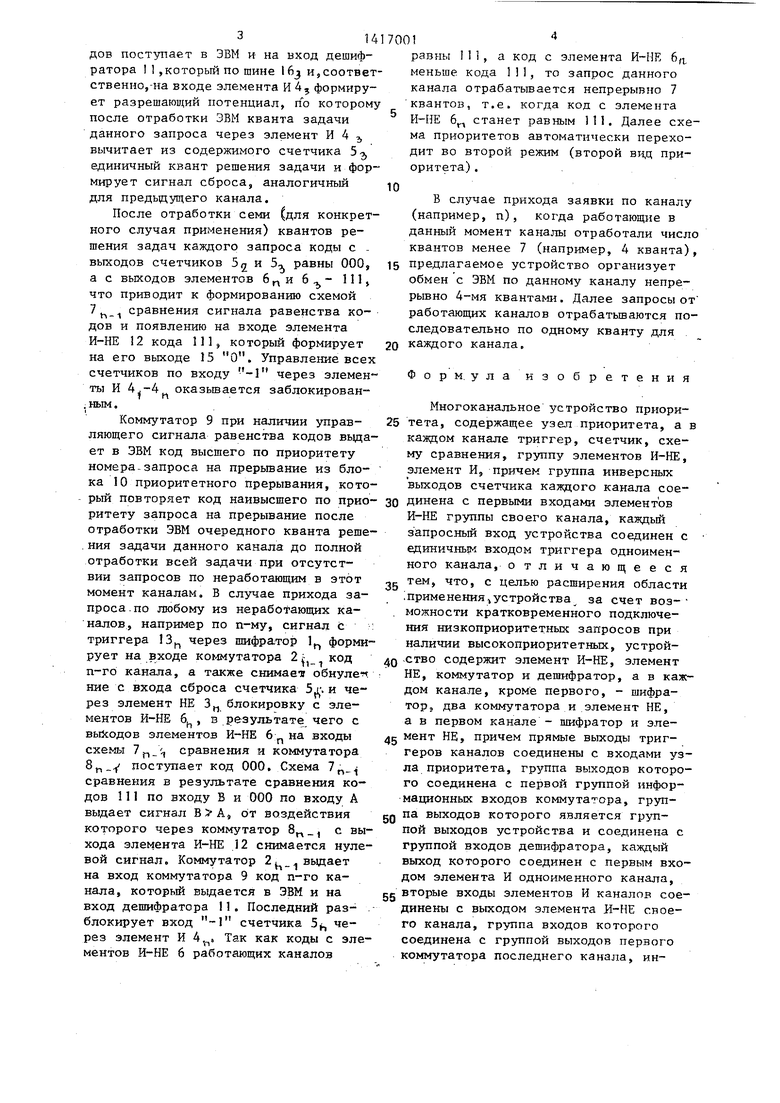

Целью изобретения является расиш- рение области применения устройства за счет возможности кратковременного подключения низкоприоритетных запро- :сов при наличии высокоприоритетных, : На чертеже изображена структурная 1схема устройства приоритета.

Устройство содердит шифраторы 1, коммутаторы ,,, элементы НЕ , элементы И -4, счетчики ,,9 группы элементов И-НЕ , схемы сравнения, коммутаторы 8f,. , коммутатор 9, узел 10 приоритета, дешифратор 11, элемент 12, триггеры 13 -13,, прямые выходы 14,- ,14 триггеров , выход 15 элемента И-НЕ 12, выходы , дешиф- ратора 11, сигнальные входы ,, устройства5 запросные входы устройства, группу выходов 19 устройства.

Устройство работает следующим об- разом.

Запросы на прерьшание поступают на единичные входы триггеров 13 - 13 по входам 18 -18. , Рассмотрим работу устройства при одновременном по- ступлении запросов, например, на вхо- ды 18 2 и 18j триггеров 13, и 132,. При этом элементы И-НЕ 6 группы через элемент НЕ 3 заблокированы и на выходе устанавливается код 111, При отсутствии-запроса по первому каналу счетчик 5 по входу сброса находится в состоянии шифратор при единичном сигнале на входе формирует на выходе код 111. Аналогичные элементы с 4-го до п-го каналов имеют идентичные с первым каналом сигналы Нулевое состояние инверсного выхода триггера 132 через элемент НЕ 3- разблокирует элементы И-НЕ 6л группы. При этом на выходах элемента И-НЕ 6 2 устанавливается код 000, с входа сброса счетчика 5 снимается сигнал Обнуление, а шифратор 1 ( при нулевом сигнале на

входе выдает на вход коммутатора 2 ,,

код 010. Аналогичные элементы третьего канала имеют сигналы, аналогичные сигналам второго канала, за исключением шифратора 1 т, который при нулевом сигнале на входе в з1дает на вход коммутатора 2 код Oil.

Схема 7 сравнения производит сравнение кода с элементов 6, т,е . кода младшего по номеру направления, которое для каждой схемы сравнения обозначим символом В, с кодом с элементов 6/2. старшего по номеру направления, которое для каждой схемы сравнения обозначим символом А, и выдает, в результате сравнения сигнал В А.

Так как остальные каналы функционируют аналогично, то на вход элемента И-НЕ 12 поступает код 000, что соответствует формированию на его выходе сигнала . Коммутатор 2, выдает на вход коммутатора 9 код 010, а схема 7 сравнения выдает на управляющий вход коммутатора 9 сигна отсутствия равенства кодов, по которому коммутатор 9 вьздает в ЭВМ сигналы по .вьпсодам 19 и на вход дешифратора 11 поступивший с коммутатора 2,код, т.е. 010. При этом дешиф- ратор 11 формирует единичный сигнал по выходу 16, который разблокирует элемент И 41. Получив по выходам 19 код прерывания, ЭВМ включает задачу, соответствзтощую этому коду прерыва- ьгая. После отработки кванта этой задачи устройство управления ЭВМ выдает по входу 17 сигнал Отработка, который через элемент И 4, при отсутствии на одном из ее входов блокирующего потенциала по входу 15, а также наличии разрешающего потенциала дешифратора 11 вычитает из содержимого счетчика 5 единичный квант решения задачи данного запроса, а также сигнал сброса заявки отработанного кванта задачи, который устанавливает триггер 14л в нулевое состояние при отсутствии 1 на входе 18, т.е. сигнала продолжения решения задачи.

Таким образом, после решения кванта задачи с выхода счетчика 5„ на вторые входы элемента И-НЕ 6п постуг пает код 110 и соответственно на его выход код 001. Далее после анализа схемами 7 -7,сравнения кодов 111 с элемента 6, 001 с элемента 6 „, 000 с элемента 6, и 111 с элементов 6,-6 на входе элемента И-НЕ 12 будет код 000, а на вход коммутатора 9 с коммутатора 2 поступает код 011, который при отсутствии со схемы 7| . сравнения сигнала равенства ко314

дов поступает в ЭВМ и на вход дешифратора 1 1 ,который по шине 16j HjCOOTseT ственно,-иа входе элемента И 4, Формирует разрешающий потенциал, пЪ которому после отработки ЭВМ кванта задачи данного запроса через элемент И 4 ,, вычитает из содержимого счетчика 52, единичный квант решения задачи и формирует сигнал сброса, аналогичный для предьдущего канала.

После отработки семи (для конкретного случая применения) квантов решения задач каждого запроса коды с - выходов счетчиков 52 и 5, равны 000, а с выходов элементов 6 и 6 - 111, что приводит к формированию схемой 7 j сравнения сигнала равенства кодов и появлению на входе элемента И-НЕ 12 кода 111, который формирует на его выходе 15 О. Управление всех счетчиков по входу - через элемен ты И 4j-4 оказьтается заблокирован- .ным.

Коммутатор 9 при наличии управляющего сигнала равенства кодов выдает в ЭВМ код высшего по приоритету номера-запроса на прерьшание из блока 10 приоритетного прерывания, который повторяет код наивысшего по приоритету запроса на прерывание после отработки ЭВМ очередного кванта реше- .ния задачи данного канала до полной отработки всей задачи при отсутствии запросов по неработающим в этот момент каналам, В случае прихода запроса -по любому из неработающих каналов, например по п-му, сигнал с триггера 13 через шифратор Ц формирует на входе коммутатора 2 L код п-го канала, а также снимае-в обнуле ние с входа сброса счетчика 5х. и через элемент НЕ 3 блокировку с элементов И-НЕ б, в результате чего с вьйсодов элементов И-НЕ 6 на входы схемы , сравнения и коммутатора поступает код 000. Схема 7„ сравнения в результате сравнения кодов 111 по входу В и 000 по входу А выдает сигнал , от воздействия которого через коммутатор 8 , с выхода элемента И-НЕ .12 снимается нулевой сигнал. Коммутатор 2ц вьщает на вход коммутатора 9 код п-го канала, который выдается в ЭВМ и на вход дешифратора П. Последний разблокирует вход -1 счетчика 5 через элемент И 4, Так как коды с элементов И-НЕ 6 работающих каналов

700

равны III, а код с элемента И-НЕ 6,-i меньше кода 111, то запрос данного канала отрабатывается непрерывно 7 квантов, т.е. когда код с элемента И-Effi 6,., станет равным )11. Далее схема приоритетов автоматически переходит во второй режим (второй ви,ц приоритета) .

10

В случае прихода заявки по каналу (например, п), когда работающие в данный момент каналы отработали числ квантов менее 7 (например, 4 кванта)

15 предлагаемое устройство организует обмен с ЭВМ по данному каналу непрерывно 4-мя квантами. Далее запросы от работающих каналов отрабатьшаются последовательно по одному кванту для

20 каждого канала.

Форм, ула изобретения

Многоканальное устройство приори25 тета, содержащее узап приоритета, а каждом канале триггер, счетчик, схему сравнения, группу элементов И-НЕ, элемент И, причем группа инверсных выходов счетчика каждого канала сое30 динена с первыми входами элементов И-НЕ группы своего канала, каждый запросный вход устройства соединен с единичнь М входом триггера одноименного канала, отличающееся

2g тем, что, с целью расширения области iпримененияJустройства за счет воз- можности кратковременного подключения низкоприоритетных запросов при наличии высокоприоритетных, устрой Q -ство содержит элемент И-НЕ, элемент НЕ, коммутатор и дешифратор, а в каждом канале, кроме первого, - шифратор, два коммутатора и элемент НЕ, а в первом канале - шифратор и мент НЕ, причем прямые выходы триггеров каналов соединены с входами узла приоритета, группа выходов которого соединена с первой группой информационных входов коммутатора, групgQ па выходов которого является группой выходов устройства и соединена с группой входов дешифратора, каждый выход которого соединен с первым входом элемента И одноименного канала,

gg вторые входы элементов И каналов соединены с выходом элемента И-НЕ своего канала, группа входов которого соединена с группой выходов первого коммутатора последнего канала, ин51

версный выход триггера ка к;п;ого канала соединен с входом шифратора своего канала, входом сброса счетчика своего канала и через элемент НЕ с вторыми входами элементов И-НЕ группы своего канала, выход элемента И канала соединен со счетным входом счет- ч;ика своего канала и с входом сброса Триггера своего канала, третий вход элемента И каждого канала соединен с соответствующим сигнальным входом устройства, группа выходов шифратора первого канала соединена с первой Группой информационных входов второго коммутатора второго канала вторая группа информадионных входов, второго коммутатора второго канала соединена с группой выходов шифратора второго канала, первая группа информационных входов второго коммутатора i-ro канала (, ., «,п, п-количество каналов) соединена с группой выходов второго коммутатора (1-1)-го канала, вторая группа информационных входов второго коммутатора i-ro канала соединена с группой выходов шифратора i-ro канала, выходы элементов И-НЕ группы первого канала соединены с первой группой входов схе- мы сравнения второго канала, вторая Группа входов схемы сравнения второго канала соединена с выходами элементов И-НЕ группы второго канала, первая группа входов схемы сравнения 1-го канала соединена с группой выходов первог о коммутатора (i-1) го кангша, вторая группа входов схемы сравнения i-ro канала соединена с выходами элементов К-НЕ группы i-ro канала, первая группа информационньпс

1 6

входов первого коммутатора второго канала соединена с выходами элементов И-НЕ группы первого канала, вторая группа информационных входов первого коммутатора второго канала соединена с выходами элементов И-НЕ группы второго канала, первая группа информационных входов первого коммутатора 1-го канала соединена с группой выходов коммутатора (i-l)-ro канала, вторая группа информационных входов первого коммутатора i-ro канала соединена с выходами элементов И-НЕ группы i-ro канала, выходы Равно и

Меньше схем сравнения всех каналов, кроме последнего, объединены и через монтажное ИЛИ соединены с первыми управляющими входами вторых коммутаторов своих каналов, второй управляющий вход второго коммутатора каждого канала,кроме последнего, соединен с выходом Больше схемы сравнения своего канала, выход Равно схемы сравнения последнего канала соединен с первым управляющим входом второго коммутатора своего канала, второй управляющий вход которого соединен с выходом Больше схемы сравнения последнего канала, выход Меньше схемы сравнения последнего канала соединен с первым управляющим входом коммутатора и через элемент НЕ - с вторым управляющим входом первого коммутатора, вторая группа входов которого соединена с ГРЗД1ПОЙ выходов второго ком- .мутатора последнего канала, первый и . второй управляющие входы первых коммутаторов каналов .соединены соответственно с выходами Больше и Меньше схем сравнения своих каналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1989 |

|

SU1686444A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство для распределения заданий между ЭВМ | 1990 |

|

SU1755280A1 |

| Многоканальное устройство управления вводом информации в микроЭВМ | 1984 |

|

SU1234844A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Многоканальное устройство ввода информации | 1988 |

|

SU1529238A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для сопряжения управляющей и управляемых вычислительных машин | 1988 |

|

SU1517033A1 |

| Устройство приоритетных прерываний | 1990 |

|

SU1741134A1 |

Авторы

Даты

1988-08-15—Публикация

1986-05-05—Подача