Устройство относится к вычислительной технике и может быть использовано для управления очередностью обращения нескольких абонентов к коллективно используемому ресурсу.

Известно устройство приоритетного прерывания 1, содержащее три регистра, группу элементов И, дешифратор и первый элемент ИЛИ, единичные входы первого регистра соединены с запросными входами устройства, информационные входы второго регистра соединены с выходами первого регистра, тактовый вход устройства соединен с тактовым входом второго регистра, информационные входы третьего регистра соединены с входами масок устройства, первые и вторые входы элементов И группы соединены соответственно с выходами второго и третьего регистров, выход дешифратора соединен с входом сброса соответствующего разряда первого регистра.

Недостатками известного устройства являются сложность конструкции, низкое быстродействие и низкая достоверность работы.

Наиболее близким по технической сущности к заявляемому является устройство 2, содержащее три регистра, группу элементов И, дешифратор, пять элементов ИЛИ и четыре мультиплексора, причем единичные входы первого регистра соединены с запросными входами устройства, информационные входы второго регистра соединены с выходами первого регистра, информационные входы третьего регистра соединены с входами масок устройства, тактовый вход устройства соединен с синхров- ходом второго регистра, первые и вторые входы элементов И группы соединены соответственно с выходами второго и третьего регистров, каждый выход дешифратора соединен с нулевым соответствующим входом первого регистра, выходы элементов И группы соединены с соответствующими входами первого элемента ИЛИ, выход которого является соответствующим разрядным выходом устройства, и соединен с управляющим входом первого мультиплексора, информационные входы которого соединены с выходами элементов И группы, выходы первого мультиплексора, второго элемента ИЛИ, второго мультиплексора, третьего элемента ИЛИ, третьего мультиплексора, четвертого элемента ИЛИ, пятого мультиплексора и пятого элемента ИЛИ соединены с последовательно,тактовый вход третьего регистра соединен с входом записи устройства, группа выходов кода прерывания устройства соединена с выходами дешифратора.

Недостатками известного устройства, выбранного в качестве прототипа, являются

сложность оборудования. Также прототип имеет узкую область применения.

Целью заявляемого устройства является расширение области применения за счет организации вложенных циклов обслужива0 ния запросов.

Поставленная цель достигается тем, что в устройство приоритетного прерывания, содержащее три регистра, первую группу элементов И, элемент ИЛИ и мультиплек5 сор, причем запросные входы устройства соединены с единичными входами разрядов первого регистра, выходы которого соединены с информационными входами второго регистра, информационные входы третьего

0 регистра соединены с входами масок устройства, одноименные выходы второго и третьего регистров соединены соответственно с первыми и вторыми входами соответствующих элементов И первой группы,

5 введены четвертый регистр, вторая группа элементов И, два формирователя импульсов, три элемента И, элемент задержки, блок сравнения и приоритетный шифратор, причем тактовый вход устройства соединен

0 с синхровходом второго регистра, с первыми входами первого и второго элементов И, управляющим входом мультиплексора и входом элемента задержки, выход которого подключен к первому входу третьего эле5 мента И, второй вход и выход которого соединены соответственно с выходом блока сравнения и входом второго формирователя импульсов, выход которого является сигнальным выходом устройства и соединен с

0 первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом первого формирователя импульсов и синхровходом четвертого регистра, информационные входы которого

5 соединены с выходами мультиплексора, первая и вторая группы информационных входов которого соединены соответственно с первой группой выходов преобразователя кодов и с информационными входами уст0 ройства, выходы четвертого регистра являются выходами кода прерывания устройства и соединены с первой группой блока сравнения, вторая группа входов которого соединена с выходами первой груп5 пы приоритетного шифратора, выходы второй группы которого соединены с первыми входами элементов И первой группы, выходы элементов И первой группы соединены с входами приоритетного шифратора, вторые входы элементов И второй группы

объединены и соединены с первым ответ-ным входом устройства, выходы подключе- 5 нгы к соответствующий уЛейЪГ г входам

-ра3 ядоҐ пёрбйго регйстраГвТо|)ой ответ-ный вход устройства соедине н с вторым входом втброго элемента И, выход которого

-пода л1бч ён°1ГвхоДу первого формирователя

-импуЖсбв, вхЪд записи устройства соеди- е ТГён с вторым входом первооГЗлемента И,

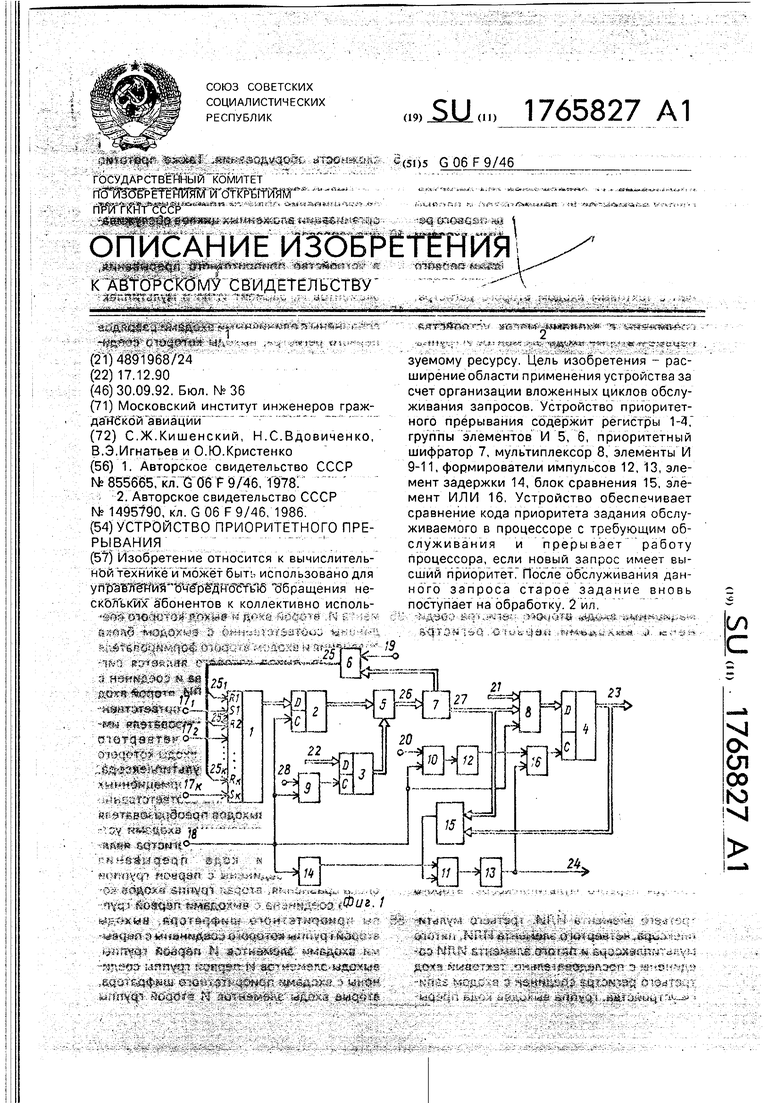

-выход кЪторо го подключен if синУровхЪду i третьего pterncfpa щр На фиг. 1 приведена структурная схема

-устройства приоритетного прерывания; на

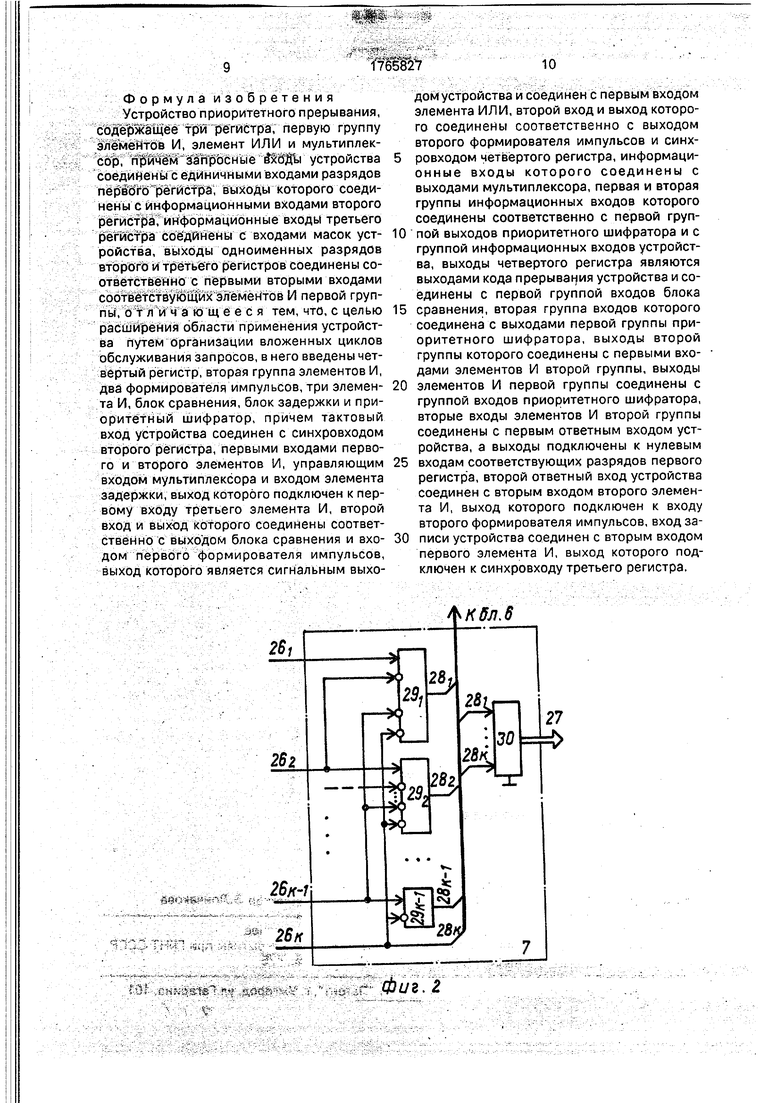

-фиг. 2 - структурная схема приоритетного Г шифратора.

-тве& Устройство приоритетного прерывания

-содержит регистры 1-4, группы элементов И 5, 6 приоритетный шифратор 7, мультиплексор 8, элементы И 9-11, формирователи импульсов 12, 13, элемент 14 задержки, блок 15 сравнения и элемент ИЛ И 16 Запросные 17i-17K входы устройства соединены с еди- ничн ымм входами соответствующих разрядов блока 1. Тактовый 18 вход устройства соединен с входами элементов 9, 10 14, с син ровходом регистра 2 и с управляющим мультиплексора 8 Первый 19 ответный вход устройства соединен с входами элементов И 6 группы. Второй ответный 20 вход устройства соединен с входом элемента И 10 Группа информационных входов 21 устройства соединена с первой группой информационных входов мультиплексора 8 Группа входов 22 масок устройства соединена с информационными входами регистра 3 Выходы кода прерывания 23 соединены с выходами регистра 4 и с первой группой входов блока сравнения 15. Сигнальный 24 выход устройства соединен с выходом формирователя 13 и с входом элемента ИЛИ 16 Выходы 25 элементов И 6 группы соединены с соответствующими нулевыми вводами регистра 1 Выходы 26 элементов И 5 группы соединены с Входами приоритетного Шифратора 27, выходы 27 которого подключены к второй группы информационных входов блоков 8 и 15. Вход 28 записи устройства соединен с входом элемента И 9.

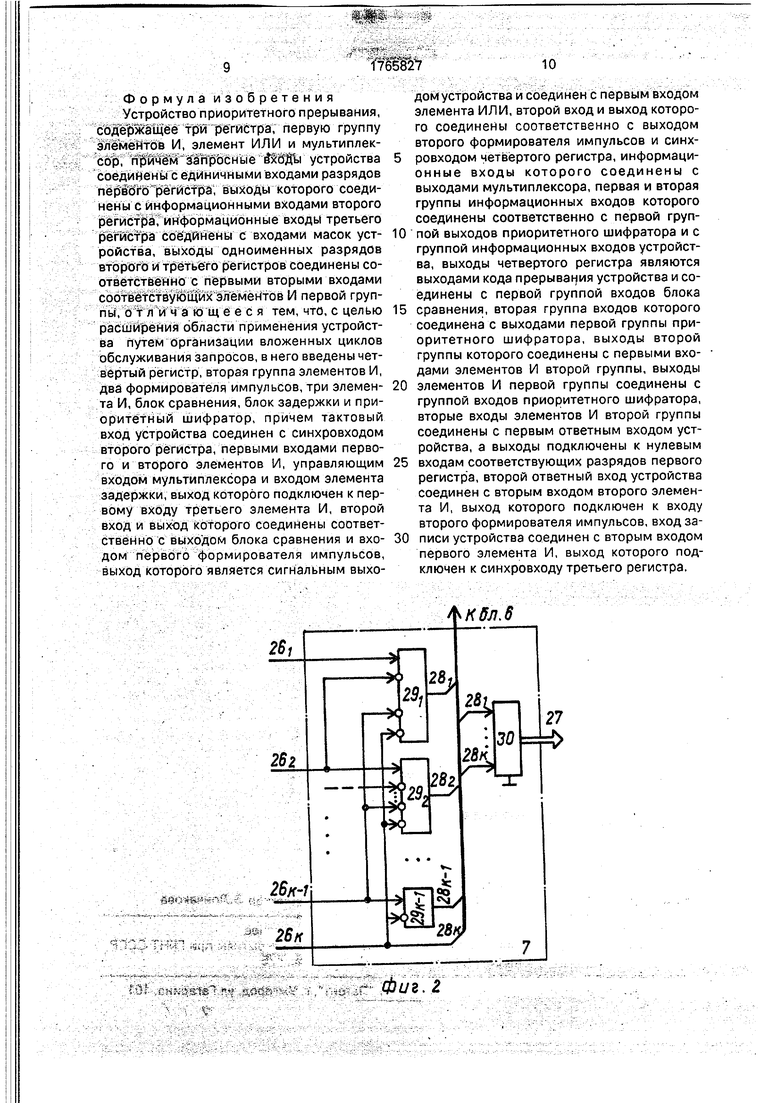

„ни Приоритетный шифратор 7 (фиг 2) содержит группу элементов И 29г29к 1 (где К - число каналов запросов устройства) и шифратор 30.

ту- Устройство работает следующим образом. -I-.-

с. В исходном состоянии регистры 1 и 2 обнулены в регистр 3 занесены значения масок (при единичном значении соответствующего разряда кода масок данный канал запросов участвует в обслуживании и имеет свой приоритет, при нулевом - нет), чем

больше номер канала запроса, тем выше его приоритет Первое занесение кода масок в pernctp 3 может производиться и при подаче на эле мТэнт И 9 сигнала записи, а на

информационное входы - кода масок - с первым тактовым импульсом на входе 18 Регистр 4 - также в нулевом состоянии. При отсутствии сйРнсГгГЗГ по л бж йтел ъного потенциала с выхода формирователя 12 мульти0 плексор 8 коммутирует на свои выходы сигналы с входов блока 7 Цепи начальной установки устройства не показаны на чертежах. --...Поступающие запросы записываются в

5 разряды регистры 1, устанавливая их в единичное состояние. Работа устройства осуществляется под управлением тактовых импульсов. Рассмотрим работу устройства в установившемся режиме (как наиболее

0 сложном; кроме того, практически работа в любой ситуации не отличается от описывае- мой ниже).

С приходом тактового импульса первоначально опрашивается обслуживающее ус5 тройство на факт окончания обслуживания Это производится следующим образом1 тактовый импульс поступает на элемент И 10, и если в данный момент времени процессор закончил обслуживание некоторого запро0 са, он (процессор) выставляет на вход 20 сигнал окончания обслуживания (второй ответный вход), а на входы 21 - код запроса, который был прерван в обслуживании при прерываний запросом, обслуживание кото5 рого в описываемый момент окончено (если такого прерванного запроса не было, процессор выставляет нулевой код на входах 21) При этом открывается элемент И 10, и тактовый импульс проходит на его выход и

0 запускает формирователь 12, формирующий положительный импульс требуемой Дл1йГтШьШЪт йГв 6дэлемё нтаУ ЛИ 16, при этом мультиплексор 8 подключает на свои выходы код с входов 21 Тактовый импульс

5 на формирователе 12 также задерживается (последовательно с блоком 12 может быть включен элемент задержки, не показанный на чертеже) с целью установления кода на выходах мультиплексора 8 и к моменту при0 хода положительного фронта с выхода формирователя 12, по которому код выходов 21 записывается регистр 4 Длительность тактового импульса выбирается таким обра5 зом, чтобы обеспечить запись кода в регистр 4 (может быть на управляющем входе блока 8 также включен формирователь не показанный на чертеже).

Таким образом, в регистр 4 записывается код прерванного запроса Если после окончания обслуживания очередного запроса процессор не имеет прерванного, в регистр 4 записывается нулевой код. В том случае, когда на данном тактовом импульсе окончания обслуживания запроса нет (нет сигнала на входе 20), формирователь 12 не вырабатывает импульса, а в регистре 4 остается код запроса, обрабатываемой в текущий момент времени процессором.

Одновременно с описанными процессами, тактовый импульс записывается совокупность пришедших (и уже содержащихся, но не обслуживаемых из-за низкой приоритетности) запросов из регистра 1 в регистр 2 и сигналом на синхровход регистра 2 (перепись происходит по положительному фронту тактового импульса); поступая на вход элемента И 9 тактовый импульс разрешает у (при необходимости) смену кода масок - если эта смена нужна, пользователь п выставляет на входы 22 новый код масок, а на вход 28 - сигнал записи).

Далее, записанные запросы в регистре 2, прореживаются кодом масок на элементах И группы 5, и поступают на входы приоритетного шифратора (фиг. 2); совокупность элементов И 29 преобразует коды запросов на входах 26 блока 7 в позиционный код разрядности К, о где позиция единственной единицы определяется номером канала запроса, имеющего наивысший приоритет (максимальный номер канал), это обеспечивается закрытием сигналом запроса максимального приоритета элементов И всех запросов меньших приоритетов. В шифраторе 30 данный позиционный код преобразуется в двоичный, соответствующий номеру запроса на данном такте с наивысшим приоритетом, этот код поступает по выходам 27 в мультиплексор 8, а с окончанием управляющего импульса на управляющем входе мультиплексора 8 - и на его выходах. Длительность тактового импульса и интервал задержки элемента 14 выбираются таким образом, чтобы задержанный тактовый импульс появлялся на выходе элемента 11 после окончания тактового импульса на входе 18.

На блоке сравнения производится сравнение приоритетов текущего запроса, выполняемого процессором,и максимального среди ожидающих (с выходов 27 блока 7). Если ожидающий запрос максимального приоритета больше приоритета выполняемого запроса, на выходе блока сравнения 15 появляется положительный потенциал; задержанный тактовый импульс проходит через открытый этим потенциалом элемент И 11 на формирователь импульсов 13, на выходе которого формируется импульс требуемой длительности, отправляемый процессору с требованием прерывания; по положительному фронту этого импульса в регистр А записывается максимальный приоритет (его код) из мультиплексора 8, который также поступает к процессору.

Процессор, принимая сигнал требования прерывания и код прерывания, прерывает выполнение текущего запроса (либо

выходит из состояния останова при отсутствии выполняемого запроса), и выставляет на выходе 19 (первом ответном выходе) код подтверждения прерывания; по этому сигналу подтверждения прерывания срабатывает соответствующий элемент И группы 6 и сбрасывает в нулевое состояние соответствующий разряд регистра 1, фиксируя успешное прерывание работы процессора. Если же код с выходов 27 меньше или

равен коду с выходов регистра 4, прерывания быть не должно (иначе это означало бы прерывание заявкой низшего приоритета более высокоприоритетной заявки); при этом задержанный тактовый импульс не

проходит через элемент И 11 и вышеупомянутые процессы не происходят.

Со следующим тактовым импульсом описанные процессы повторяются.

Следует отметить некоторые специфические особенности заявляемого устройства (свойственные, естественно и прототипу, и, как правило, всем устройствам прерывания):

-связь по информационным входам (выходам с процессором) обслуживающим

устройством)и при реализации последнего с двунаправленной шиной данных - может быть реализована включением соответствующих шинных формирователей, работающих под управлением процессора, и обеспечивающих двунаправленную работу шины с попеременной передачей - в соответствии с тактовыми импульсами - сигналов по входам процессора 23 и выходам 21;

для этой же цели могут быть использованы регистры-защелки с тремя состояниями выходных цепей, так это обычно реализуется в процессорах при их связи по двунаправленной шине данных с несколькими внешними

устройствами. Указанные цепи не показаны на чертежах;

-на выходах 17-20 устройства могут быть использованы формирователи импульсов, не показанные на чертеже с целью обеспечения длительности входных сигналов, требуемого при конкретной выбранной частоте тактовых импульсов, и временных параметрах обслуживающего устройства (процессора), и заявляемого устройства.

Формула изобретения Устройство приоритетного прерывания, содержащее три регистра, первую группу элементов И, элемент ИЛИ и мультиплексор, причём Опросные i&dfty устройства соединены с единичными входами разрядов перв 5го регистра, выходы которого соединены с информационными входами второго регистра, информационные входы третьего регистра сое дйнены с входами масок устройства, выходы одноименных разрядов второго и третьего регистров соединены соответственно с первыми вторыми входами соответствующих элементов И первой группы, отличающееся тем, что, с целью расширения области применения устройства путем организации вложенных циклов обслуживания запросов, в него введены четвертый регистр, вторая группа элементов И, два формирователя импульсов, три элемента И, блок сравнения, блок задержки и приоритетный шифратор, причем тактовый вход устройства соединен с синхровходом второго регистра, первыми входами первого и второго элементов И, управляющим входом мультиплексора и входом элемента задержки, выход которого подключен к первому входу третьего элемента И, второй вход и выход которого соединены соответственно с выходом блока сравнения и входом первого формирователя импульсов, выход которого является сигнальным выходом устройства и соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго формирователя импульсов и синх- 5 ровходом четвертого регистра, информационные входы которого соединены с выходами мультиплексора, первая и вторая группы информационных входов которого соединены соответственно с первой груп0 пой выходов приоритетного шифратора и с группой информационных входов устройства, выходы четвертого регистра являются выходами кода прерывания устройства и соединены с первой группой входов блока

5 сравнения, вторая группа входов которого соединена с выходами первой группы приоритетного шифратора, выходы второй группы которого соединены с первыми входами элементов И второй группы, выходы

0 элементов И первой группы соединены с группой входов приоритетного шифратора, вторые входы элементов И второй группы соединены с первым ответным входом устройства, а выходы подключены к нулевым

5 входам соответствующих разрядов первого регистра, второй ответный вход устройства соединен с вторым входом второго элемента И, выход которого подключен к входу второго формирователя импульсов, входза0 писи устройства соединен с вторым входом первого элемента И, выход которого подключен к синхровходу третьего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обслуживанием запросов | 1990 |

|

SU1709315A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для обработки прерываний | 1986 |

|

SU1606975A1 |

| Устройство для сопряжения группы процессоров с группой внешних устройств | 1988 |

|

SU1599865A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для формирования сигналов прерывания | 1986 |

|

SU1341640A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1283768A1 |

| Устройство приоритета | 1985 |

|

SU1269135A1 |

Изобретение относится к вычислительной технике и может быт использовано для уп|йВ7га Я №ГГреЯН беть1б Обращения не- скЬл ькШ абонентов к коллективно исполь« ч глекг 0/ .г v -„ О1, Р Ј. Л M, Э -Ь - , J 4f6r5 « AfjC4 ьос Ю и ., Rr lrO -tie-R C VS as-xy-js afat5Siw f. г H-9fts 3€r3 АВ fitwrn- feesw .Ґ Н АГивГвЗР t, smfTtuee ft oieraa Tsro ItvKl tO & isft#fa&Ј . 7/( pf T- eev jdoeaf жо«смз y Jg se awiit -- ®4иа®йР ч- Н Г f t;V f iiiJ-SI11 j. г I- Ct f „ .tw. о з &ООДЗП а. . Ј-ОЗ / ai, eaf§ i r«tt- . j 9 1 ЭЧ а{ 4 4««чй Ґ Й1й-«гтв { Д«5 - е -в5сь-з&Щ4С «sfetfi jxa i--п ч ,ец ейф|ва| зг «%аЭ2;}-чЗдй|г M fillip %oa0W W Aj -stSft X ftffT Srw 1 ч w. v « , i зуемому ресурсу Цель изобретения - расширение области применения устройства за счет организации вложенных циклов обслуживания запросов Устройство приоритетного прерывания содержит регистры 1-4, группы элементов И 5, 6, приоритетный шифратор 7, мультиплексор 8, элементы И 9-11, формирователи импульсов 12, 13, элемент задержки 14, блок сравнения 15, элемент ИЛИ 16 Устройство обеспечивает сравнение кода приоритета задания обслуживаемого в процессоре с требующим обслуживания и прерывает работу процессора, если новый запрос имеет высший приоритет После обслуживания данного запроса старое задание вновь поступает на обработку 2 ил 4 „Ул Ь t Ј.мf-Si . , f Wt.- a . - t. 4 vas J ic . - CO Os СЛ 00 hO X| J jresTSf- J; Ря-К tr -.-««tt «Ј. & Й-i.jf-svi |-чЯ14 Й1«-«наШ5йы51а 1|авч-(3,.«А -fesiyRtH к. ггшЁ &Јц&«&#г4;,.г. з м--э ЧГ ;- «С,7 3 ftttK 5 Od tdUJ - I f }J iei& ЪфИ&%& ,nSff i il

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-09-30—Публикация

1990-12-17—Подача