Изобретение относится к вычислительной технике и может быть использовано в мультипрограммных вычислительных системах.

Известно устройство, содержащее регистр запросов, вход которого является информационным входом устройства, дешифратор приоритета запроса, подключенный выходами к соответствующим входам памяти очередей запросов, узел синхронизации и регистра масок l..

Недостаток этого устройства состоит в его ограниченных функциональных возможностях, вследствие чего оно не может быть использовано в вычислительных системах, работающих в реальном масштабе времени и ре-. шающих одновременно несколько задач.

Наиболее близким к предлагаемому по технической суашости является устройство, содержащее регистр за- просов, дешифратор приоритета запроса; регистры хранения очереди для каждого приоритета запроса, образующие память очередей запросов, узел синхронизации, узел приоритета запросов , шифратор приоритета решаемых задач, регистры приоритета запроса, схемы сравнения приоритетов, дешифратор адреса прерывания, регистры приоритета раздела памяти, регистр масок 2}Недостатком этого устройства является его сложность.

Цель .изобретения - сокращение аппаратурных затрат за счет сравнения вновь поступившего запроса с наименьшим приоритетом, стоящим на

10 обслуживании.

Поставленная цель достигается тем, что устройство, содержащее регистр приоритета, два блока элементов И, блок памяти, распределитель 5 импульсов, узел выбора старшего

приоритета, группу блоков элементов И, группу выходных регистров, регистр маски и схему сравнения, причем кодовый вход устройства соеди20нен с информационным входом регистра приоритета, выход которого соединен с первым входом первого блока элементов И, второй вход которого соединен с первым выходом распреде25лителя импульсов, вход которого соединен с входом запуска устройства, второй выход соединен с первым входом второго блока элементов И, группа входов которого соединена с

30 группой информационных выходов блпка памяти, информационный вход которого соединен с первым информационным входом устройства, второй информационный вход которого соединен с информационным входом регистра маски, выход которого соединен с вторым входом второго блока элементов И, выход которого соединен с входом узла выбора старшего приоритета, выход первого блока элементов И соединен с входом дешифратора, группа выходов которого соединена с группой адресных входов блока памяти, выходы выходных регистров являются группой информационных выходов устройства, содержит группу дешифраторов, третий блок элементов И, шифратор, регистр младшего приоритета и узел выбора младшего приоритета, причем выход каждого выходного регистра соединен с входом соответствющего дешифратора группы, выход каждого дешифратора группы соединен с соответствующим входом группы входов третьего блока элементов И, вход которого соединен с третьим выходом распределителя импульсов, четвертый выход которого соединен с первьми входами блоков элементов группы, второй вход каждого из которых соединен с выходом узла выбора старшего приоритета и с первым входом схемы сравнения, выход которой является выходом прерывания устройства, выход третьего блрка элементов И соединен с входом узла выбора младшего приоритета, выход которого соединен с информационным входом регистра младшего приоритета, тактовый вход которого соединен с третьим выходом распределителя импульсов , выход регистра младшего приоритета соединен с входом шифратора и с третьим входом каждого блока элементов И группы, выход шифратора соединен с вторым входом схемы сравнения.

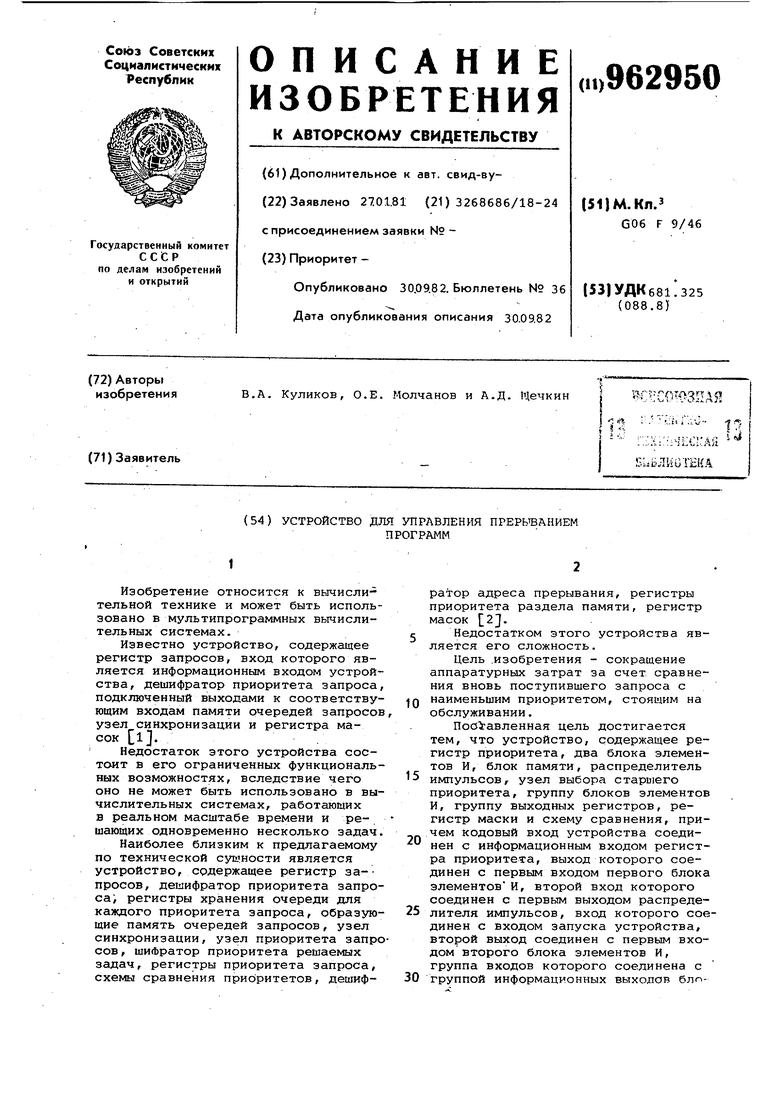

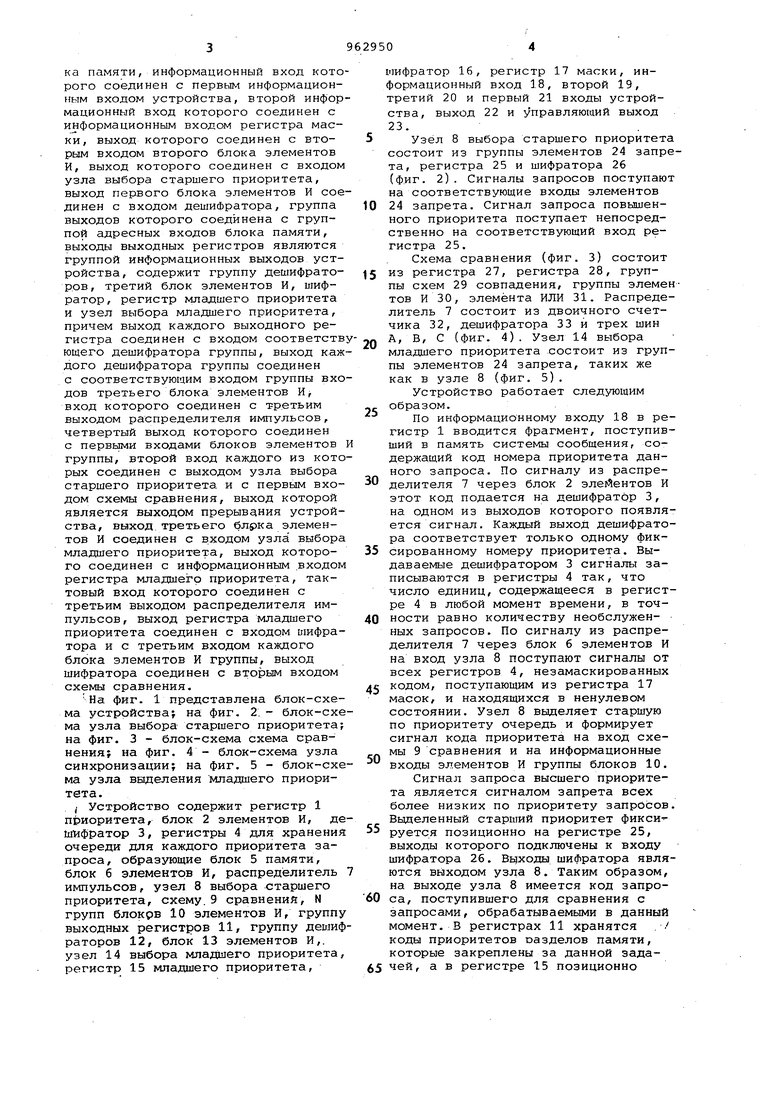

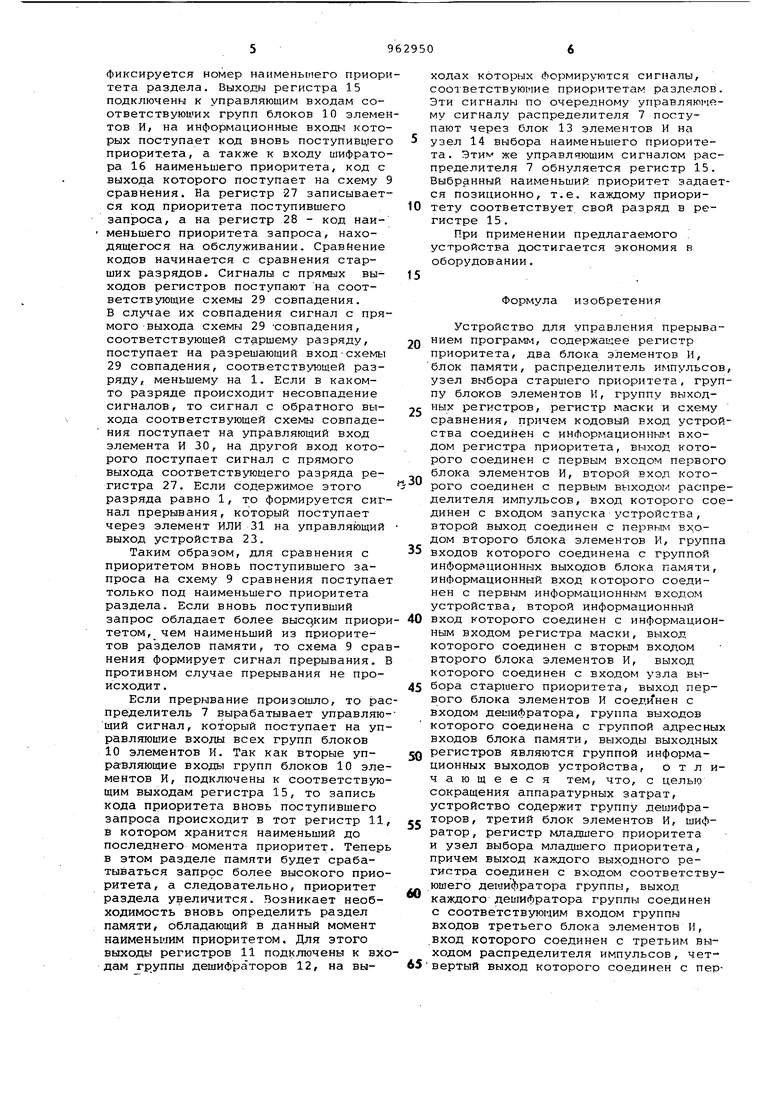

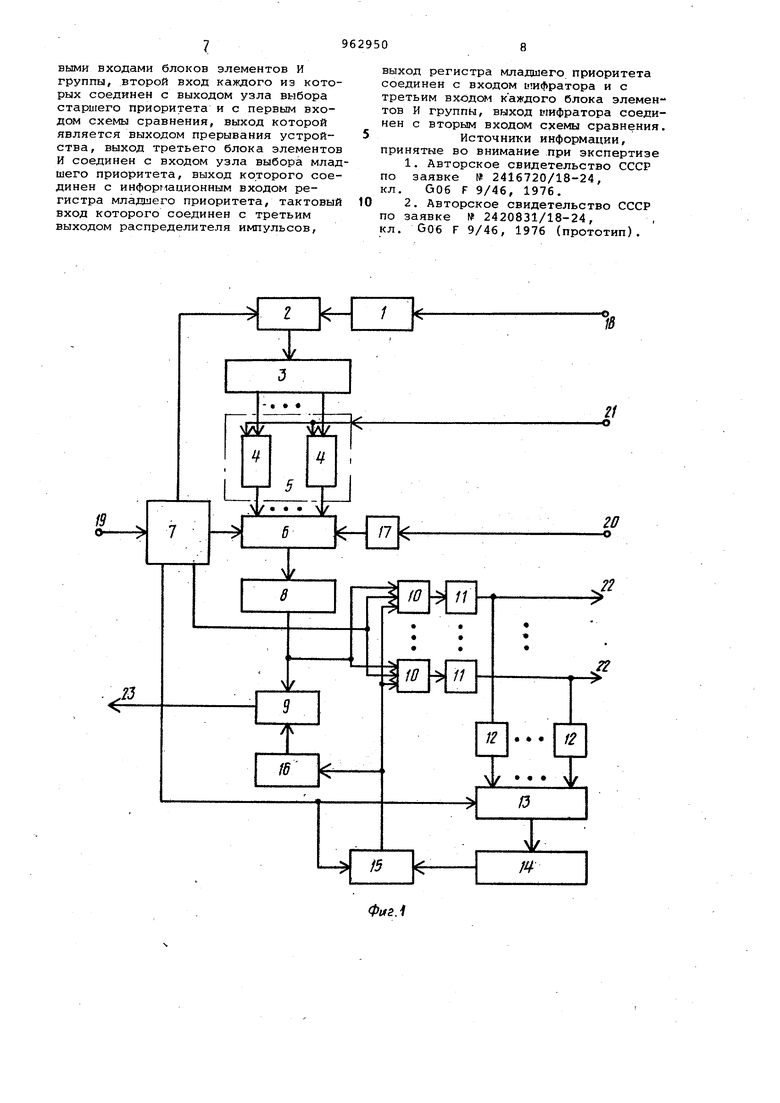

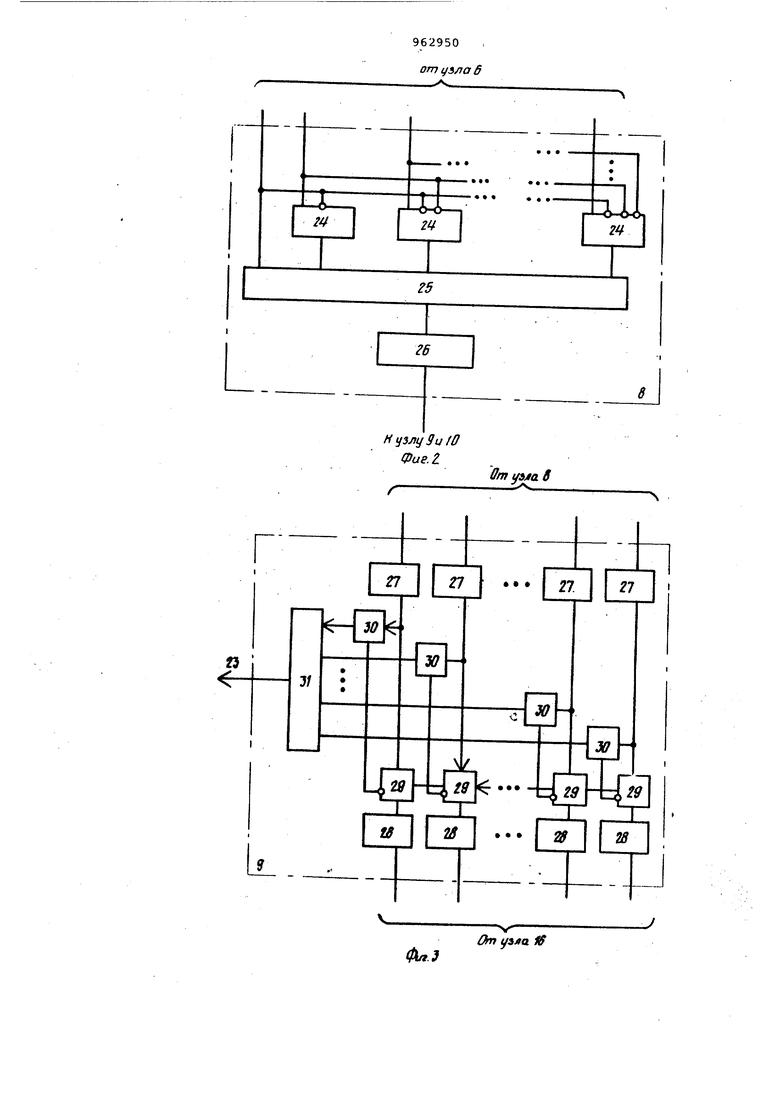

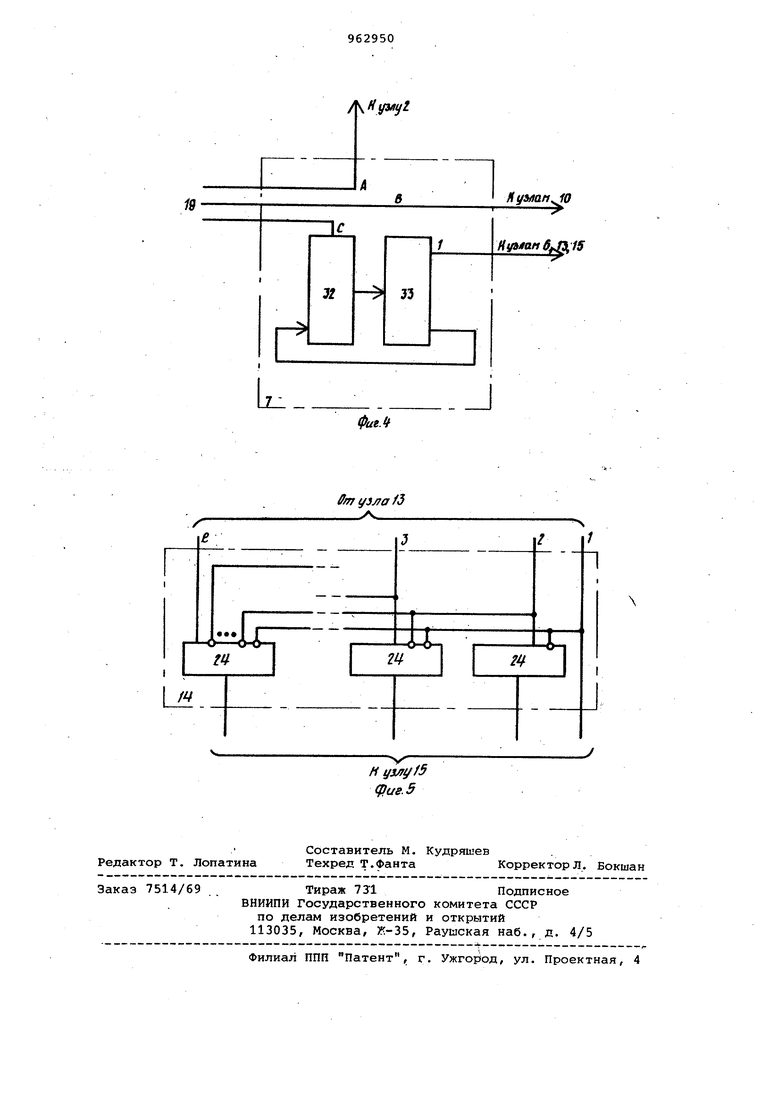

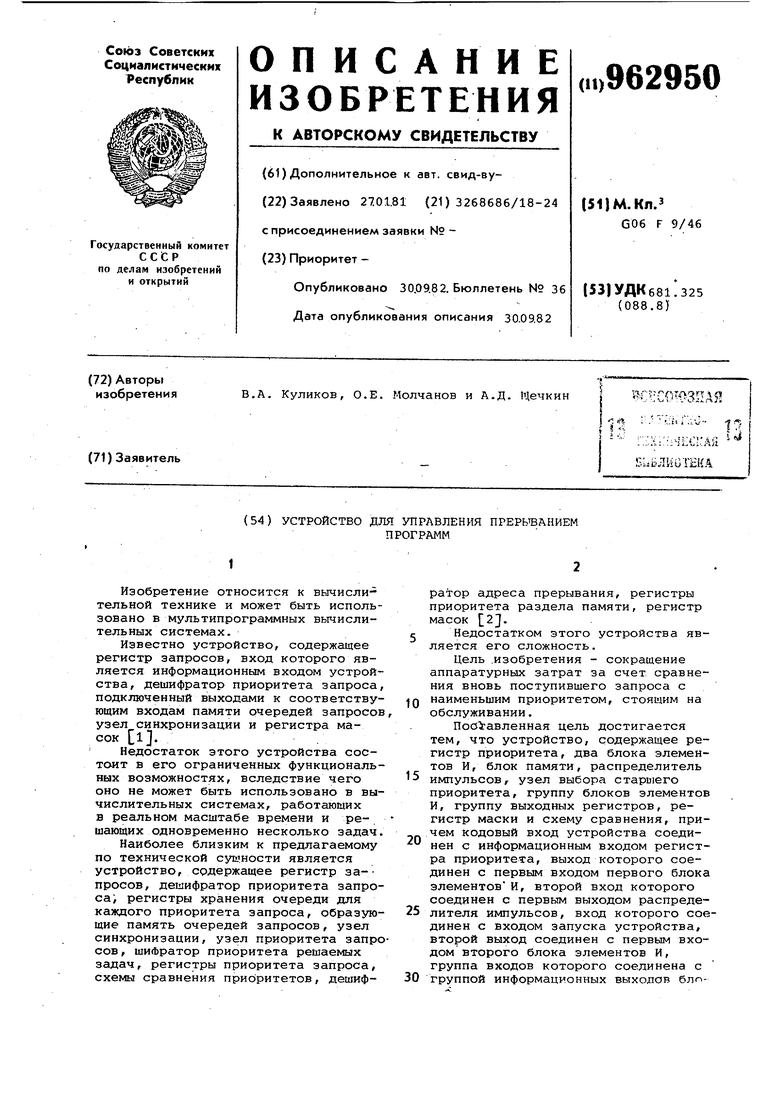

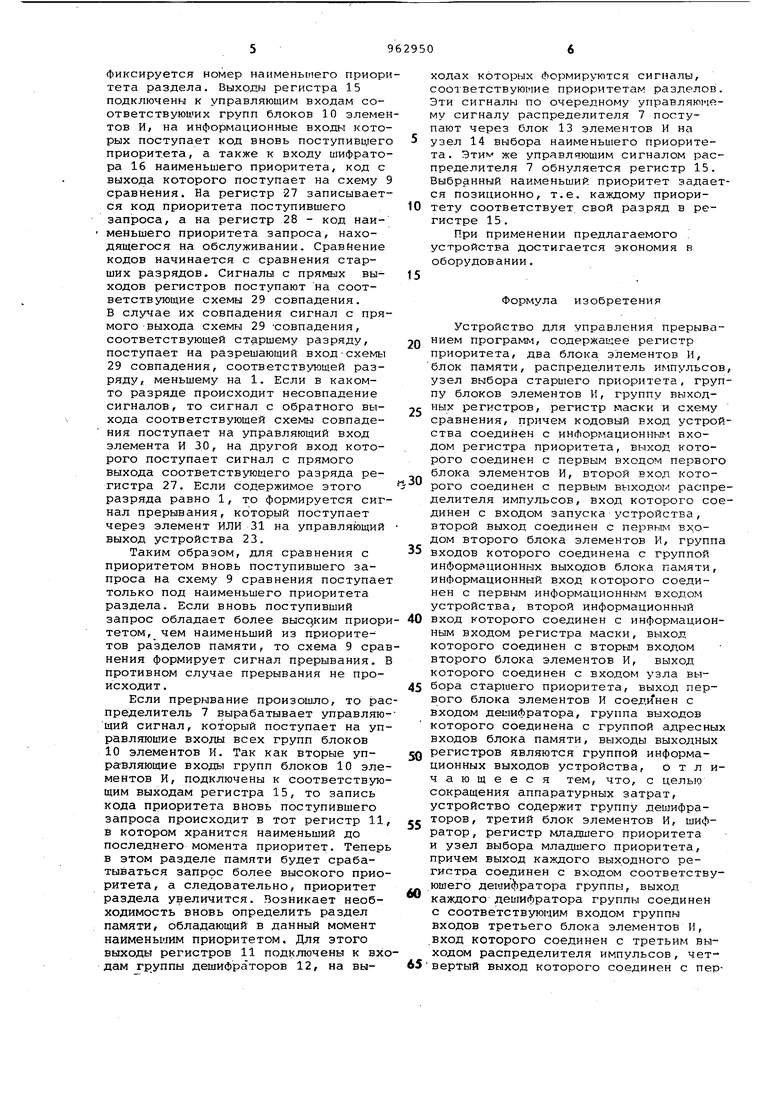

На фиг. 1 представлена блок-схема устройства; на фиг. 2.- блок-схема узла выбора старшего приоритета; на фиг. 3 - блок-схема схема сравнения; на фиг. 4 - блок-схема узла синхронизации; на фиг. 5 - блок-схема узла ВБщеления младаиего приоритета.

, Устройство содержит регистр 1 приоритета, блок 2 элементов И, дешифратор 3, регистры 4 для хранений очереди для каждого приоритета запроса, образующие блок 5 памяти, блок б элементов И, распределитель импульсов, узел 8 выбора старшего приоритета, схему.9 сравнения, N групп блокрв 10 элементов И, группу выходных регистров 11, группу дешифраторов 12, блок 13 элементов И,, узел 14 выбора младшего приоритета, регистр 15 младшего приоритета.

шифратор 16, регистр 17 маски, информационный вход 18, второй 19, третий 20 и первый 21 входы устройства, выход 22 и управляющий выход 23.

Узел 8 выбора старшего приоритета состоит из группы элементов 24 запрета, регистра 25 и шифратора 26 (фиг. 2). Сигналы запросов поступают на соответствующие входы элементов

24 запрета. Сигнал запроса повышенного приоритета поступает непосредственно на соответствующий вход регистра 25.

Схема сравнения (фиг. 3) состоит

из регистра 27, регистра 28, группы схем 29 совпадения, группы элементов И 30, элемента ИЛИ 31. Распределитель 7 состоит из двоичного счетчика 32, дешифратора 33 и трех шин

А, В, С (фиг. 4) . Узел 14 выбора

младшего приоритета состоит из группы элементов 24 запрета, таких же как в узле 8 (фиг. 5).

Устройство работает следующим образом.

По информационному входу 18 в регистр 1 вводится фрагмент, поступивший в память системы сообщения, содержащий код номера приоритета данного запроса. По сигналу из распределителя 7 через блок 2 элe Seнтoв И этот код подается на дешифратор 3, на одном из выходов которого появляется сигнал. Каждый выход дешифратора соответствует только одному фиксированному номеру приоритета. Выдаваемые дешифратором 3 сигнальт записываются в регистры 4 так, что число единиц, содержащееся в регистре 4 в любой момент времени, в точности равно количеству необслуженных запросов. По сигналу из распределителя 7 через блок 6 элементов И на вход узла 8 поступают сигналы от всех регистров 4, незамаскированных

кодом, поступающим из регистра 17 масок, и находящихся в ненулевом состоянии. Узел 8 выделяет старшую по приоритету очередь и формирует сигнал кода приоритета на вход схемы 9 сравнения и на информационные

входы элементов И группы блоков 10. Сигнал запроса высшего приоритета является сигналом запрета всех более низких по приоритету запросов. Выделенный старший приоритет фикси руется позиционно на регистре 25, выходы которого подключены к входу шифратора 26. Вцходы шифратора являются выходом узла В. Таким образом, на выходе узла 8 имеется код запроса, поступившего для сравнения с запросами, обрабатываемыми в данный момент. В регистрах 11 хранятся . / коды приоритетов оазделов памяти, которые закреплены за данной задачей, а в регистре 15 позиционно фиксируется номер наименьгпего приор тета раздела. Выходы регистра 15 подключены к управляющим входам соответствующих групп блоков 10 элеме тов И/ на информационные входы кото рых поступает код вновь поступивц ег приоритета, а также к входу шифрато ра 16 наименьшего приоритета, код с выхода которого поступает на схему сравнения. На регистр 27 записывает ся код приоритета поступившего запроса, а на регистр 28 - код наименьшего приоритета запроса, находящегося на обслуживании. Сравнение кодов начинается с сравнения старших разрядов. Сигналы с прямых выходов регистров поступают на соответствующие схемы 29 совпадения. В случае их совпадения сигнал с пря мого выхода схемы 29 -совпадения, соответствующей старшему разряду, поступает на разрешающий вход-схемь 29 совпадения, соответствующей разряду, меньшему на 1. Если в какомто разряде происходит несовпадение сигналов, то сигнал с обратного выхода соответствующей схемы совпадения поступает на управляющий вход элемента И 30, на другой вход которого поступает сигнал с прямого выхода соответствующего разряда регистра 27. Если содержимое этого разряда равно 1, то формируется сиг нал прерывания, который поступает через элемент ИЛИ 31 на управляющий выход устройства 23. Таким образом, для сравнения с приоритетом вновь поступившего запроса на схему 9 сравнения поступае только под наименьшего приоритета раздела. Если вновь поступивший запрос обладает более выс9ким приор тетом, чем наименьший из приоритетов разделов памяти, то схема 9 сра нения формирует сигнал прерывания. противном случае прерывания не происходит . Если прерывание произошло, то ра пределитель 7 вырабатывает управляю щий сигнал, который поступает на уп равляющие входы всех групп блоков 10 элементов И. Так как вторые управляющие входы групп блоков 10 эле ментов И, подключены к соответствую щим выходам регистра 15, то запись кода приоритета вновь поступившего запроса происходит в тот регистр 11 в котором хранится наименьший до последнего момента приоритет. Тепер в этом разделе памяти будет срабатываться запрос более высокого прио ритета, а следовательно, приоритет раздела увеличится. Возникает необходимость вновь определить раздел памяти, обладающий в данный момент наименьшим приоритетом. Для этого выходы регистров 11 подключены к вх дам группы дешифраторов 12, на выходах которых формируются сигналы, соответствующие приоритетам разделов. Эти сигналы по очередному управляющему сигналу распределителя 7 поступают через блок 13 элементов И на узел 14 выбора наименьшего приоритета. Эти же управляющим сигналом распределителя 7 обнуляется регистр 15. Выбранный наименьший приоритет задается позиционно, т.е. каждому приоритету соответствует свой разряд в регистре 15. При применении предлагаемого I устройства достигается экономия в оборудовании. Формула изобретения Устройство для управления прерыванием программ, содержащее регистр приоритета, два блока элементов И, блок памяти, распределитель импульсов, узел выбора старшего приоритета, группу блоков элементов И, группу выходных регистров, регистр маски и схему сравнения, причем кодовый вход устройства соединен с информационны входом регистра приоритета, выход которого соединен с первым входом первого блока элементов И, второй вход которого соединен с первым выходом распределителя импульсов, вход которого соединен с входом запуска устройства, второй выход соединен с первым входом второго блока элементов И, группа входов которого соединена с группой информационных выходов блока памяти, информационный вход которого соединен с первым информационным входом устройства, второй информационный вход которого соединен с информационным входом регистра маски, выход которого соединен с вторым входом второго блока элементов И, выход которого соединен с входом узла выбора старшего приоритета, выход первого блока элементов И соединен с входом дешифратора, группа выходов которого соединена с группой адресных входов блока памяти, выходы выходных регистров являются группой информационных выходов устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, устройство содержит группу дешифраторов, третий блок элементов И, шифратор, регистр младшего приоритета и узел выбора младшего приоритета, причем выход каждого выходного регистра соединен с входом соответствующего дешифратора группы, выход каждого дешифратора группы соединен с соответствующим входом группы входов третьего блока элементов И, .вход которого соединен с третьим выходом распределителя импульсов, четвертый выход которого соединен с первыми входами блоков элементов И группы, второй вход каждого из которых соединен с выходом узла выбора старшего приоритета и с первым входом схемы сравнения, выход которой является выходом прерывания устройства, выход третьего блока элементов И соединен с входом узла выбора младшего приоритета, выход которого соединен с информационным входом регистра младшего приоритета, тактовый вход которого соединен с третьим выходом распределителя импульсов.

выход регистра младшего приоритета соединен с входом иифратора и с третьим входом каждого блока элементов И группы, выход шифратора соединен с вторым входом схемы сравнения.

5Источники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке № 2416720/18-24, кл. G06 F 9/46, 1976,

10 2. Авторское свидетельство СССР по заявке № 2420831/18-24, кл. G06 F 9/46, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления прерыванием программ | 1976 |

|

SU696459A1 |

| Устройство для прерывания программ | 1981 |

|

SU972511A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство прерывания программ | 1983 |

|

SU1119015A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Устройство для сопряжения электронной вычислительной машины с абонентами | 1976 |

|

SU642701A1 |

| Устройство для трансляции логических адресов в адреса памяти на магнитных дисках | 1981 |

|

SU966695A1 |

п г

51

б

Hysjjyffufff Фие.2.

ffm узла 8

f7

21

27

30

Х/

- 44

/

2ff

tff

v

J Hf

(

19

Нумап О

L

. J

Авторы

Даты

1982-09-30—Публикация

1981-01-27—Подача