(54) ДННАИНЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2002 |

|

RU2221270C2 |

| Устройство для ввода информации от двухпозиционных датчиков | 1984 |

|

SU1156053A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Запоминающее устройство | 1979 |

|

SU809361A1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА АКТИВНОГО ВИДЕО | 1999 |

|

RU2173883C2 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU930656A1 |

| УСТРОЙСТВО ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2217791C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

1

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных машинах, интерпретирующих программу, записанную на языке высокого уровня минимашинах; не имеющих программных средств динамического распределения памяти, а также для страничного обмена между оперативными запоминающими устройствами ЗУ и внешними запоминающими устройствами.

Известно устройство для управления информацией в динамическом ЗУ, содержащем адресный блок, логические элементы и дешифратор с накопителем

fl.

Однако сложная структура и применение значительного количества оборудования ограничивают область испо1Тьзования данного устройства.

Наиболее близким по технической сущности к предложенному изобретению является динамическое запоминающее устройство, содержащее накопитель, один из входов которого соединен с первым выходом блока управления, другой вход которого соединен со входом счетчика и выходом блока делителей частоты, вход которого подключен ко второму выходу блока управления, первые входы блока управления соединены с выходами регистра уровня и блока сравнения соответственно, вход регистра уровня соединен с шиной сигнала номер уровня , входы блока сравнения соединены соответственно с выходами счетчика и регистра адреса, один из входов которого подключен к адресной шине, и шины сиг0налов з апрос и возврат, которые соединены со вторыми входами блока управления 2.

Недостатком известного устройства является большое среднее время на обслуживание заявки.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что устройство содержит блок

0 опроса, выходы которого соединены с третьим входом блока управления и другим входом регистра адреса соответственно, выход накопителя соединен с первым входом блока опроса,

5 второй и третий входы которого соединены с другими выходшли регистра уровня и регистра адреса соответственно.

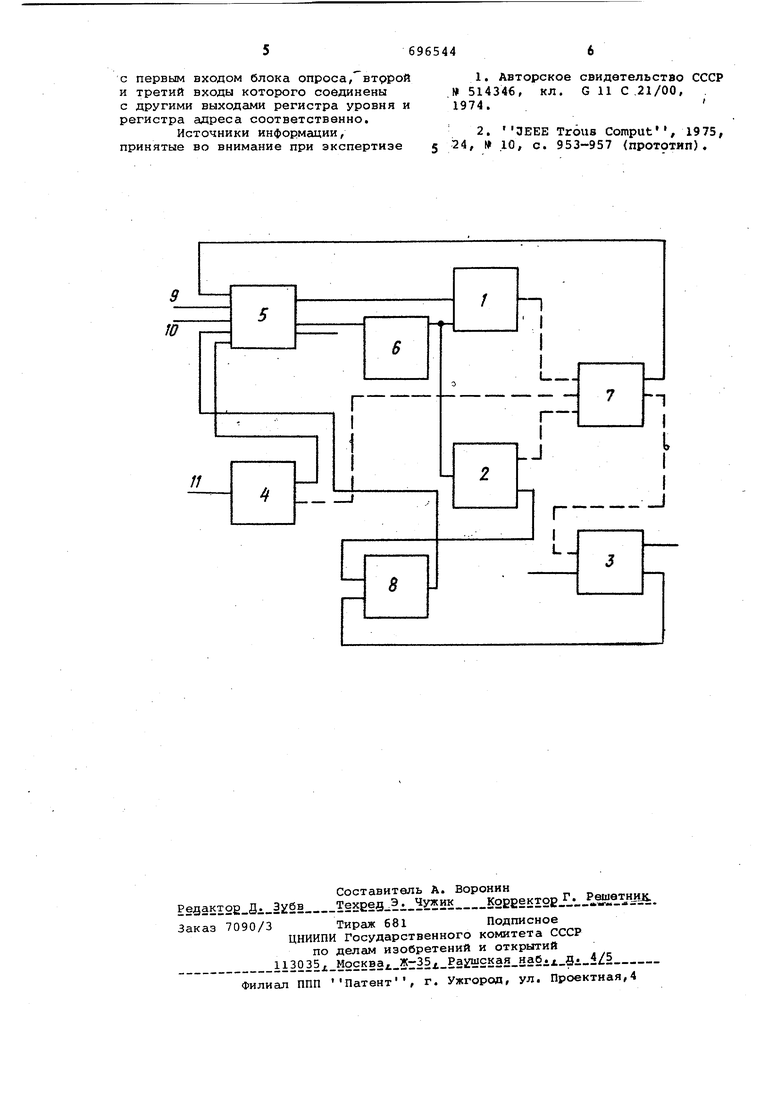

Сущность изобретения поясняется

0 чертежом, на котором изображена функциональная схема предложенного устройства, которое содержит накопитель 1, выполненный на сдвигающих регистрах,счетчик 2, регистр адреса 3, регистр уровня 4, блок управлени 5, блок делителей частоты б, блок опроса 7, блок сравнения 8, причем блок управления соединен С шиной 9 сигналов запрос и шиной 10 сигналов возврат, а регистр уровня 4 - с шиной 11 сигнала номер уровня .. Устройство работает следующим образом. На блок управления 5 поступает сигнал запрос по шине 9, а на регистр уровней 4 - номер уровня по шине 11, который соответствует объему запрашиваемой памяти. Вся распределяемая память объемом 2 слов разделяется на ячейки памяти объемом 2, , .. .2 двоичных слов. Все ячейки памяти одного размера представляются сдвиговым регистром. Следовательно, сдвиговых регистров в накопителе 1 столько, сколько существует различных размеров уровней памяти. Все сдвиговые регистры отображают, таким образом, структуру памяти в виде дерева. На каждом уровне, начиная с век хнего нулевого, количество разрядов в регистре определяется как 2 , где Е 0,1,п, (6- текущий номер уровня). . По сигналу запрос и номеру уровня блок управления 5 вырабатыва импульсы, которые выдаются на блок делителей частоты б. На самый нижний уровень - п, импульсы поступают с частотой fn, на каждый последующи уровень импульсы поступают с частотой вдвоеменьшей, чем на предыдуще Это объясняется тем, что количество ячеек памяти на каждом последующем уровне вдвое меньше, чем на предыду щем. Импульсы с блока делителей час тоты б поступают на накопитель 1 , для сдвига содержимого их влево на один разряд по каждому импульсу. Одновременно импульсы частоты подаю ся и на счетчик 2, где производитс их подсчет. Сдвиг в накопителе 1 продолжаетс до тех пор, пока в одной из ячеек п мяти накопителя 1 соответствующего уровня не будет зафиксирован нуль. Это свидетельствует о том, что данная ячейка Пс1мяти свободна. Этой яч ке соответствует начальный адрес, который содержится в счетчике 2. Од временно наличие нуля в ячейке пам ти накопителя 1 и сигнал с регистр уровня 4, поступающие на блок опро са 7, обеспечивают пересылку содер жимого счетчика 2 в регистр адреса 3 для последующей выдачи его. При этом блок опроса Т обеспечивает не бходимый сдвиг информации при переаче из счетчика 2 в регистр адреса в соответствии с номером уровня. ри этом в ячейку памяти накопителя данного уровня заносится единица, видетельствующая о том-, что данная чейка памяти накопителя 1 занята. аносятся единицы и в ячейки накопиеля 1 других уровней, которые свяаны с ячейками памяти накопителя 1. о древовидной структуре. Если все.ячейки памяти накопителя 1 данного уровня оказались занятыми, то с блока опроса выдается в блок управления 5 информация о том, что переписи из счетчика 2 в регистр адреса 3 не было и блок управления 5 выдает сигнал ошибка. При освобождении какой-либо ячейки памяти накопителя 1 начальный адрес этой ячейки памяти принимается в регистр адреса 3,а блок управления 5 обеспечивает выдачу импульсов на блок делителей частоты бис него на счетчик 2 и накопитель ,1. При этом происходит сравнение адресов в счетчике 2 и регистре адреса 3, блок сравнения вьщаст. сигнал на блок управления 5. Последний обеспечит запись нулей в разряды сдвиговых регистров накопителя, которые соответствуют освободившей , .я ячейке памяти с начальным адресом,, содержащимся в регистре адреса. Преимущество предложенного устройства заключается в том, что при его использовании сокращается среднее время на обслуживание заявки. Формула изобретения Динамическое запоминающее устройство, содержащее накопитель, один из входов которого соединен с первым выходом блока управления, другой вход которого соединен со входом счетчика и выходом блока делителей частоты, вход которого подключен ко второму выходу блока управления, первые входы блока управления соединены с выходами регистра уровня и блока сравнения соответственно, вход регистра уровня соединен с шиной сигнала номер уровня , входы блока сравнения соединены соответственно с выходами счетчика и регистра адреса, один из входов которого подключен к адресной шине, и шины сигналов запрос и возврат, которые соединены со вторыми входами блока управления, отличающееся тем, что, с целью повьаиения быстродействия устройства, в него введен блок опроса, выходы которого соединены с третьим входом блока управления и другим входом регистра адреса соответственно, выход накопителя соединен

с первым входом блока опроса,втррой и третий входы которого соединены с другими выходами регистра уровня и регистра адреса соответственно.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-11-05—Публикация

1977-08-01—Подача