I

Изобретение относится к вычислителной технике и может быть использовано в вычислительных машинах, интерпретирующих программу, записанную на языке высокого уровня, минимашинах не имеющих программных средств динамического распределения памяти, а также дл страничного обмена между оперативным запоминающим устройством и внешними запоминающими устройствами.

Известно устройство для управления кнфо мацией и передачи информации, содержащее адресный блок, логические элементы, дешифратор Г .

Однако сложная структура, применениё значительного количества оборудовашия ограничивают область использования этого устройства.

Наиболее близким техническим рапением к предлагаемому является динамическое запоминающее устройство, которое содержит накопитель на статических триггерах, блок управления, первый и второй регистры адреса, счетчик, блок опроса и блок сравнения pj Однако в известном устройстве время обслуживания заявки на выдачу свободного блока памяти зависит от количества занятых уже блоков на этом уровне и от быстродействия счетчика.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее накопитель, первый вход которого подключен к выходу дешифратора, первый регистр гщреса, вход которого подключен к шине управления, второй регистр адреса, выход которого подключен ко входу дешифратора, первый блок управления, первый вход которого подключен-к шине запроса, а второй - к шине контроля, введены второй блок управления, первый вход которого подключен к выходу первого регистра адреса, второй вход - к выходу первого блока управлениЯу тре.тий вход - к первому выходу накопителя, первый выход - ко второму входу накопителя, а второй выход - к третьему входу накопителя, и шифратор, вход которого подключен ко второму выходу накопителя, а выход - ко входу второго регистра адреса.

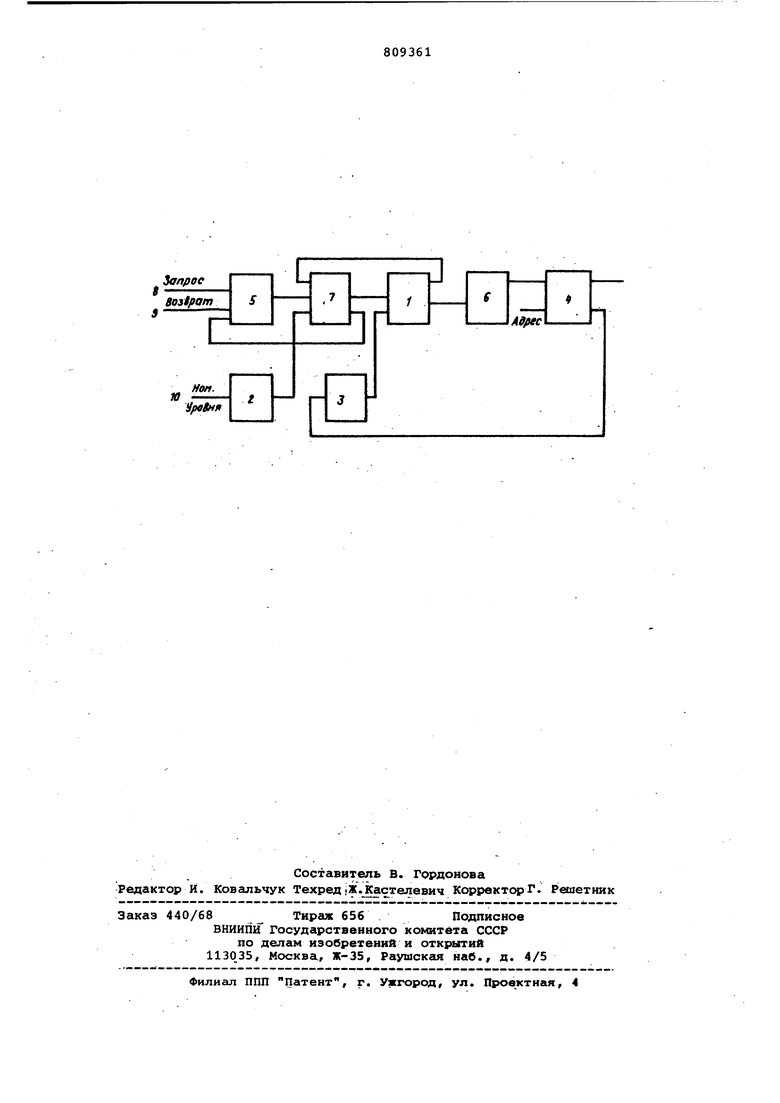

На чертеже представлена блок-схема устройства.

Запоминающее устройство содержит накопитель 1, первый регистр 2 гщреса, дешифратор 3, второй регистр 4 адреса, первый блок 5 управления, шифратор 6, второй блок 7 управления,

шину 8 запроса, шину 9 контроля и шину 10 Управления.

Устройство работает следующим образом.

На первый блок 5 управления поступает сиг-нал запроса по шине 8, а на первый регистр 2 - номер уровня по ifiKHe 10 управления, который соответ ствует объему запргшщваемой памяти. Вся распределяемая память объема 2 слов разделяется на блоки объема 2, l2 Л ..., двоичных, слов. :Все блоки памяти одного размера представляются статическим регистром. Следовательно, статических регистров в накопителе 1 столько, сколько существует различных размеров уровней памяти. Совокупность регистров накопителя отображает структуру распределяемой памяти в виде дерева. На кгивдом уровне, начиная с верхнего нулевого, :количество триггеров- в регистре определяется как 2, где б - текущий номер уровни.,

По сигналгш запроса и номера уроння первый блок 5 управления вырабатывает импульс, которой поступает иа второй блок 7 угфавления. Этот блок определяет первую свободную ячейку на этом уровне и соответствующей ей , триггер в накопителе 1, а также все | триггеры, связанные с данным по вовидной структуре и устанавливает их в единичное оостояние, что свндетельствует о том, что соответствуюищй данной ячейке накопителя блок распределяемой памяти занят. В момент перехода триггера из нулевого состояния в единичное сигнал с его прямого выхода поступает на соответствуквций вход шифратора 6, который выдает адрес ячейки памяти, соответствующей выбранному триггеру. Этот. адрес поступает на второй регистр 4 адреса и с него выдается Itoтpeбйтeлю Шифратор б представляет собой постоянное запоминающее устройство (ПЗУ) с потенциальными адресными шинами, коiTOpoe хранит номера адресов, соответствующие блокам распределяемой памяТИ. . . .

Если все ячейки накопителя 1 оказались занятыми, то с первого блока 5 управления на шину 9 контроля вьщается сигнал сшибки.:

При освобождении какого-либо блока распределяемой памяти во второй регистр 4 адреса принимается адрес освобождаемого блока, а на первый регистр 2 адреса поступает номер уровня. ,

Второй регистр 4 адреса возбуждает одну из шин дешифратора 3, который соответствует номеру освобождаемого блока и обеспечивает установку в нулевое состояние соответствующего триггера.

В предлагаемом устройстве время задержки на обслуживание будет зависеть только от динамических свойств используеьих логических элементов средней задержки распространения сигнала и количества последовательных элемено ов, через которые этот сигнал: проходит..

Таким образом, дальнейшее повышение быстродействия может быть достигнуто применением элементов с меньшим «-ср

Формула изобретения

Запсжинающее устройство, ссдержащее накопитель, первый вход которого подключен к выходу дешифратора, первый {регистр гщрёса, вход которого подключен к шине управления, второй регистр адреса, выход которого подключен ко входу дешифратора, первый блок управления, первый вход которого подключен к шине Запроса, а второй - к шине контроля, отличающеес я ,тем, что, с целью повьоиения быстродействия устройства, в него введены второй блок управления, первый вход котЬрого подключен к выходу первого регистра адреса, второй вход - к выходду первого блока управления, третий вход. - к первому выходу накопителя, первый выход - ко второму входу накопителя, а второй выход - к третьему входу накопителя, и шифратор, вхо которого подключен ко второму выходу накопителя, а выход - ко входу второго. jaemcTpa адреса. : Источники информации, принятые во внимание при зкрпертизе

1.Авторское свидетельство СССР М4346, кл. 611 С 21/00, 1976.

2.АвторОкое свидетельство СССР по :заявке 2617017/18-24, кл. G 11 С 21/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для динамического распределения памяти | 1984 |

|

SU1243031A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Динамическое запоминающее устройство | 1977 |

|

SU696544A1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство переадресации накопителяиНфОРМАции СиСТЕМы ОбРАбОТКи дАННыХ | 1979 |

|

SU845157A1 |

| Динамическое запоминающее устройство | 1984 |

|

SU1188785A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1534509A2 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Ассоциативное запоминающее устройство | 1976 |

|

SU649038A1 |

Авторы

Даты

1981-02-28—Публикация

1979-04-27—Подача