1

Изобретение относится к импульсной технике.

В основном авторском свидетельстве № 499672 описан резервированный делитель частоты, содержащий два канала, каждый из которых состоит из делителя частоты, схемы контроля, в состав ко- торой входят контрольный делитель час. тоты, логические элементы И и логический элемент НЕ, элемент намяти и элемент задержки l.

Недостатком даннот о делителя является недостаточная надежность, так как схема обнаруживает сбои вперед, т, е. появление импульсов на выходах делителей раньше установленного времени.

При сбоях назад одного из каналов деления, т. е. при появлении выходных импульсов позже установленного времени, схема обнаруживает эти сбои с не которым опозданием. Например, при сбое первого канала деления, элемент памяти первого канала (см. чертеж, испраиUjocTb 1 канала) сигнализирует о сбое

делителя частоты тааько через промежуток времени , Ноэтому в течение времени f резервированный яс.г итсль не контролируется и в случае сбоя г/горого канала деления устройство становятся неработоспособным.

Целью изобретения яБ.г1яегся иовг-лше- пие ииформациолиой илдожиости (1- вированного делмтсл51 частоты.

Поставленная цель достигаогся Т(м, что в резервиропаншлй целитель частоты, содержащий два канала, каждый из которых состоит из делителя частоты, схемы контроля, в состав которой входят контрольный делитель частоты, лог-нческио а ементы И и логичос.к1«й элемент НЕ, элемент памяти и элс-мемт ; адержки, введен логический алемоит ИЛИ, вхоД1.г которого подключены к соответствующим выходам схем контрс ля, а выход - ко входам установки;делителей частоты.

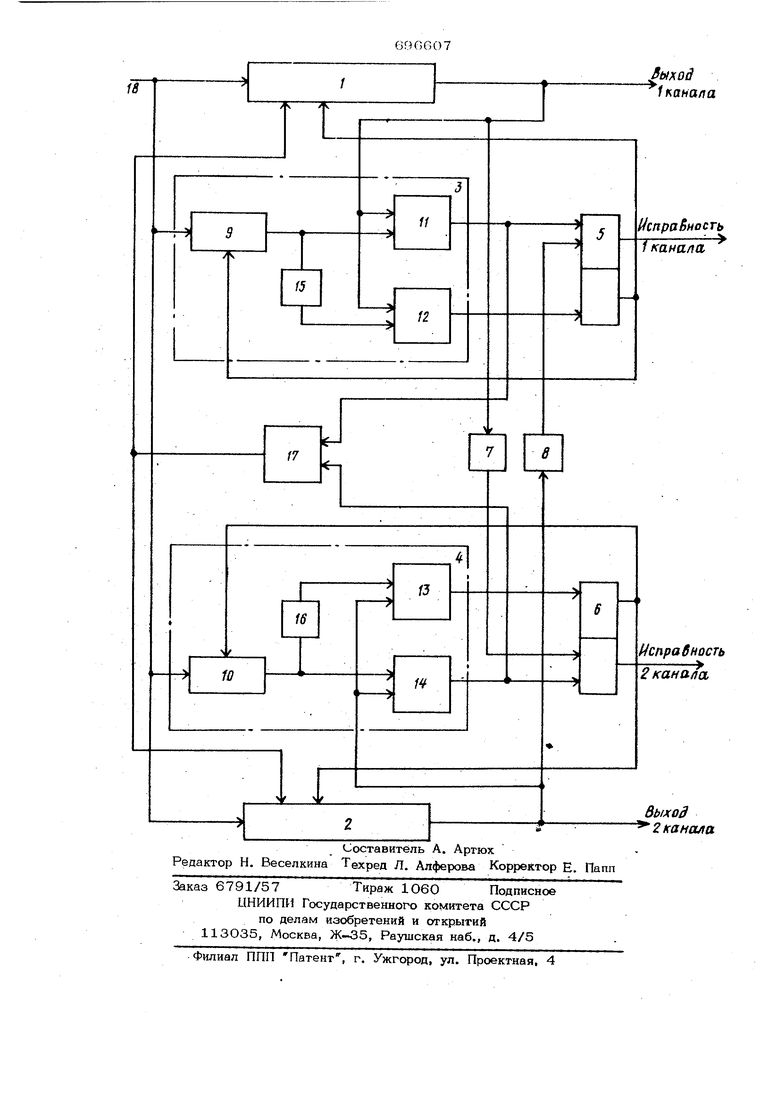

Структурная электрическая схема описываемого делителя приведена на 40f)T(;- же. Описываемый делитель частоты состоит из целителей частоты 1, 2, схем контроля 3, 4; элементов памяти 5, 6; элементов задержки 7, 8; контрольных делителей частоты 9, 10; логических элементов И 11-14; логических элементов НЕ 15, 16; логического элемента ИЛИ 17. Входной сигнал подан на входную шину 18. Резервированный делитель частоты работает слеодгющим образом. Поскольку оба канала работают аналогичным образом, рассмотрим работу одно канала деления. Входная последовательность импульсов поступает на входы делителя частоть 1 и затем на входы логических элементов И 11, 12, импульсы с выхода контрольного делителя 9 - на другой вход логического элемента И 11 и через логический элемент НЕ 15 на другой вход логического элемента И 12. При совпадении импульсов на выходах делителей 1 и 9 появдяется сигнал на выходе логического элемента И 11, который подтверждает состояние элемента памяти 5, соответствующее исправно му состоянию канала деления. При несовпадении импульсов, т. е. если сигнал с выхода делителя 1 появил ся раньше установленн н О времени, на выходе элемента И 12 появляется сигнал.,. который устанавливает элемент памяти 5 в состояние, соответствующее неисправному состоянию канала деления. На выходе элемента 5 появляется сигна который устанавливает целитель частоты 1 и контрольный делитель частоты 9 в исходное состояние в держит их в этоК состоянии (делители останавливаются). Если второй канал исправен, сигнал с выхода делителя частоты 2 через элеме задержки 8 устанавливает элемент памя . ти 5 в состояние, соответствующее исправному состоянию своего канала, сигнал на выходе логического элемента памяти 5 исчезает и первый канал деления начи нает работать. При этом начальное состояние делителей частоты 1, 2 и контрольных делителей частоты 9, 10 выбираются в соответствии с величиной задержки элементов задержки 7, 8. Иначе говоря, начальное состояние целителей таково, что после восстановления сбившегося канала по исправному оба канала работают синхронно, т. е. импульсы на выходах делителей 1 и 2 появляются одновременно. В случае сбоя делителя частоты 1 назад, т. е. когда сигнал на выходе делителя 1 отсутствует в установленное время, процесс коррекции протекает следующим образом. Если второй канал исправен, то при совпадении импульсов на выходах делителей 2, 10 появляется сигнал на выходе логического элемента И 14, который через логический элемент ИЛИ 17 устанавливает делитель 1 в исходное состояние и подтверждает начальную установку исправного делителя 2. При сбоях второго канала деления и исправном первом канале деления процесс коррекции протекает аналогично. Введение в резервированный делитель частоты элемента ИЛИ позволяет повысить надежность устройства за счет более раннего восстановления неисправного целителя по выходным сигналам исправ- joro делителя. Формула изобретения Резервированный делитель частоты по авторскому свидетельству № 499672, от л и ч а ю ш и и с я тем, что, с целью повьццения надежности, в него введен логический элемент ИЛИ, входы которого подключены к соответствующим выходам схем контроля, а выход - ко входам установки делителей частоты. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство NO 499672, кл. Н 03 К 21/34; 02.04.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты | 1978 |

|

SU752809A1 |

| Резервированный делитель частоты | 1974 |

|

SU499672A1 |

| Резервированный делитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU805496A2 |

| Резервированный делитель частоты | 1979 |

|

SU822375A1 |

| Резервированный двухканальный делитель частоты | 1982 |

|

SU1108625A1 |

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1984 |

|

SU1156570A1 |

| Многоканальный резервированный генератор | 1982 |

|

SU1072051A1 |

| Устройство ввода поправок в хранитель времени | 1984 |

|

SU1173382A2 |

| Резервированное счетное устройство | 1977 |

|

SU705687A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1978 |

|

SU767764A1 |

Авторы

Даты

1979-11-05—Публикация

1977-08-01—Подача