Изобретение относится к электротехнике и предназначено для использования при реализации вторичного электропитания электро- и радиоаппаратуры.

Целью изобретения является повышение надежности работы путем обеспечения ремонта без отключения потребителя.

На фиг.1 представлена функциональная схема многофазного параметрического стабилизатора напряжения постоянного тока; на фиг.2 - функциональная схема датчика отказа.

Стабилизатор содержит (фиг.1) преобразовательные модули 1-4, генератор 3 тактовых импульсов (в совокупности с опорным элементом), управляемый делитель 6 частоты с собствен4- но делителем 7 частоты, состоящим из счетчиков-делителей 8-10, двух- входовыми элементами И 11-13, двух- входовыми элементами И 14 и 15, четырехвходовым элементом И 16, первым четырехвходсзым элементом ИЛИ 17, вторым четырехвходовым элементом ИЛИ 18, триггером 19 управления сдвигом и регистром 20 сдвига, распределитель 21 тактовых импульсов, блок 22 логики переключения (совокупность ячеек с элементами И, ИЛИ,НЕ), предотвращающий пуск отказывающих преобразовательных модулей, формирователи 23-26 ширины импульсов, датчики 27О

to

00

о ел м

10

20

25

31628057

30 отказа с выходами 31.1-34.1, 31.2- 34.2, 31.3-34.3, 31.4-34.4.

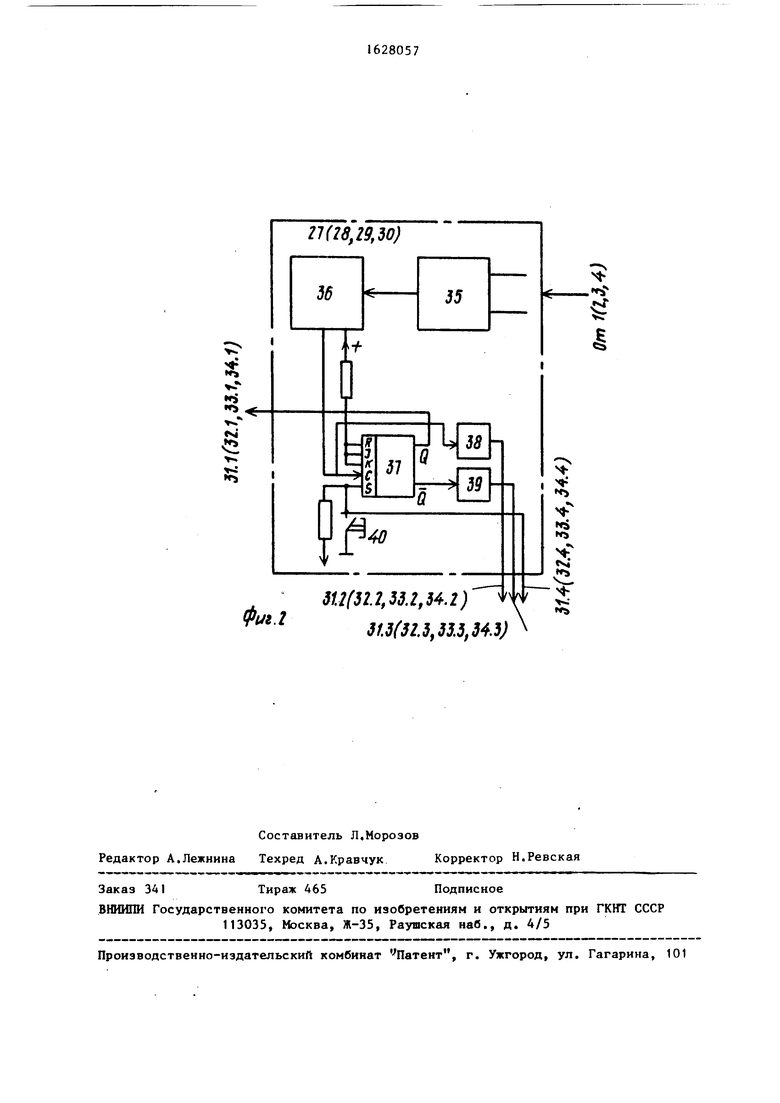

Каждый из датчиков 27-30 отказа включает двухполупериодный выпрямитель 35 (фиг.2), блок 36 доцускового контроля напряжения, триггер 37 установки, формирователи 38.и 39 коротких импульсов,и кнопку 40 установки.

Преобразовательные модули 1-4 включены параллельно между выводами для подключения первичного источника питания и нагрузки (не показаны). Каждый из преобразовательных модулей 1-4 состоит из последовательно соеди- jc ненных ключевого элемента и DLC- фильтра. Вход делителя 7 частоты подключен к выходу генератора 5 тактовых импульсов. Первые входы элементов И 11-13 соединены с соответствующими выходами делителя 7 частоты. Выходы регистра 20 сдвига подключены к вторым входам элементов И 11-13. Входы элемента ИЛИ 14 соединены с выходами элементов И 11-13. Тактирующий вход распределителя 1 тактовых импульсов подключен к выходу элемента ИЛИ 14. Входы формирователей ширины импульсов соединены с соответствующими выходами распределителя .21 тактовых импульсов, а выходы - с управляющими входами преобразовательных модулей 1-4. Каждый из датчиков 27-30 отказа первым выходок (31.1- 34.1) через блок 22 логики переключения подключен к соответствующему управляющему входу распределителя 21 тактовых импульсов, вторым выходом (31.2-34.2) соединен с одним из входов элемента ИЛИ 17. Вход двух- полупериодного выпрямителя 35 соединен с сигнальным выходом одного из преобразовательных модулей 1-4. Вход блока 36 допускового контроля напряжения подключен к выходу выпрямителя 35. Выход формирователя 38 коротких импульсов является вторым выходом (J31.2-34.2) датчиков 27-30 отказа. Входы элемента 16 И и элемента 1 8 ИЛИ соединены с третьими (31.3-34.3) и четвертыми (31.4-34.4) выходами датчиков 27- логической единицы, 30 отказа. Входы элемента ИЛИ 15 подключены к выходам элементов ИЛИ 17 и 18, а выход -к тактирующему входу регистра 20 сдвига. Тактирующий вход триггера 19 управления сдвигом соединен с выходом элемента ИЛИ 17, установочный вход -с выходом элемента И 16, а выходы - с управляющими входами

30

35

40

45

55

регистра 20 сдвига триггера 37 устано рователя 38 коротки чены к выходу блока контроля напряжения теля 39 коротких им с инверсным выходом новки. Первым выход датчиков 27-30 отка выход триггера 37 у выходом (31,3-34,3) вателя 39 коротких вертым выходом (31. ный вход триггера

Частота Јт генер импульсов определяе

fr V

где fM- частота пе вых транзи 1-4.

Например, для сх дулей п 4 fr 24

Коэффициент деле ков-делителей 8-10

кз;

Для данной схемы фициенты деления сч 8-10 соответственно

% 8; кэю 12.

Функционирование сматривается при

запуске и работе всеми исправными мо

работе стабилиза одного или нескольк

ремонте с замено время работы без от теля.

Подготовка устро осуществляется след

В исходном состо пряжения на выходе вого контроля каждо 30 отказа равен нап кого нуля. Триггеры ным нажатием кнопок единичное состояние 34.1 появляется на

ется до момента отк Через установочный триггер 19 устанавл ние, когда на его п следовательно, на у сдвига вправо SR ре ется логическая еди ном выходе Q (на уп

0

0

5

c логической единицы,

0

5

0

5

5

регистра 20 сдвига. Тактирующий вход триггера 37 установки и вход формирователя 38 коротких импульсов подключены к выходу блока 36 допускового контроля напряжения. Вход формирователя 39 коротких импульсов соединен с с инверсным выходом триггера 37 установки. Первым выходом (31.1-34.1) датчиков 27-30 отказа является прямой выход триггера 37 установки, третьим выходом (31,3-34,3) - выход формирователя 39 коротких импульсов, а четвертым выходом (31.4-34.4)-установочный вход триггера 37 установки.

Частота Јт генератора 5 тактовых импульсов определяется соотношением

fr V

где fM- частота переключения ключевых транзисторов модулей 1-4.

Например, для схемы с числом модулей п 4 fr 24 fM.

Коэффициент деления 1-го из счетчиков-делителей 8-10

кз;

Для данной схемы при п 4 коэффициенты деления счетчиков-делителей 8-10 соответственно равны Кде 6;

% 8; кэю 12.

Функционирование устройства рассматривается при

запуске и работе стабилизатора со всеми исправными модулями 1-4;

работе стабилизатора при отказе одного или нескольких модулей 1-4;

ремонте с заменой модулей 1-4 во время работы без отключения потребителя.

Подготовка устройства к запуску осуществляется следующим образом.

В исходном состоянии уровень напряжения на выходе блока 36 допускового контроля каждого из датчиков 27- 30 отказа равен напряжению логического нуля. Триггеры 37 кратковременным нажатием кнопок 40 переводятся в единичное состояние. На выходах 31.1- 34.1 появляется напряжение с уровнем

которое сохраняется до момента отказа данного модуля. Через установочный вход (не показан) триггер 19 устанавливается в состояние, когда на его прямом выходе Q и, следовательно, на управляющем входе сдвига вправо SR регистра 20 появляется логическая единица, а на инверсном выходе Q (на управляющем входе

сдвига влево SL) - напряжение логического нуля. На входах последовательной записи DR регистра 20 устанавливается логическая единица, на входе DL - логический нуль (на фиг.1 входы DR H DL не показаны). При подаче логического нуля на вход сброса R (не показан) на всех выходах регистра 20 появляется логический нуль. При подаче через элемент ИЛИ 15 на тактирующий вход С регистра 20 импульса положительной полярности последний переходит в состояние, когда на его первом выходе появляется логическая единица, а на остальных выходах сохраняется логический нуль. Последующей установкой на входе DR логического нуля регистр 20 подготовлен к сдвигу напряжения логической единицы по фронту положительного тактового импульса вправо, т.е. в сторону возрастания номеров выходов (при логической единице на входе SR и логическом нуле па входе SL) и влево (при логической единице на входе SL и логическом нуле H.I входе SR).

При включении генератора 5 тактовые импульсы поступают на входы счетчиков-делителей 8-10, которые делят частоту следования тактовых импульсов в соответствующее число раз. Поскольку напряжение логической единицы имеется лишь на входе элемента И II, на вход распределителя 21 поступают тактовые импульсы только со счетчик и 18 с периодом повторения Т/4.

Поступившие на вход расгрсцелите10

пульса на входе С триггера 19 вызывает переход триггера 19 в нулевое состояние (на выходе Q - логический

5 нуль, на выходе Q - логическая единица) . Датчик 28 отказа по выходу 32.1 переходит в нулевое состояние, а формирователь 39 коротких импульсов по выходу 32.3 генерируют короткий импульс напряжения с уровнем логической единицы. Импульс через элемент ИЛИ 18 и 15 поступает на тактирующий вход регистра 20 и своим фронтом осуществляет сдвиг логической единицы

5 вправо (с первого на второй вывод).

Так как на вход распределителя 21 поступают импульсы со счетчика- делителя 9, имеющего коэффициент деления для данной схемы, равный восьми, то период следования тактовых .импульсов составит Т/3. -Распределитель 21 и блок 22 логики переключения распределяют импульсы последовательно по модулям 1-4, минуя отказавший модуль. Следовательно, при отказе одного модуля период перекпючения ключевого транзистора модуля сохраняется, но временный сцвнг между процессами в модулях изменяется и становится

30 равным: Т/3.

20

25

При отказе еще одного модуля, например модуля 4, датчик 30 отказа данного модуля по выходу 34.1 переходит в нулевое состояние, а по вы- 35 ходу 34.1 генерирует короткий импульс. Фронтом импульса осуществляется сдвиг логической единицы с второго на третий выход регистра 20, при этом импульсы на тактирующий нход распредели- ля 21 импульсы распределяются по соот- лп ,

н и „, ителя 21 поступают со счетчика-делите- ветствующим формирователям 23-26

ля 10. Так как коэффициент деления счетчика-делителя 10 равен 12, то период следования тактовых импульсов составляет Т/2. Распределитель 21 и блок 22 логики переключения распределяют тактовые импульсы только по двум работоспособным модулям 1 и 4, частота переключений ключевых транзисторов модулей 1 и 4 не изменяется.

ширины импульсов с временным сдвигом Т/4. При запуске каждого из модулей 1-4 на выходах блоков 36 до- пускового контроля напряжения датчиков 27-30 отказа появляется напряжение с уровнем логической единицы, поступающее на тактовый пход триггера 19, при этом подтверждается его единичное состояние.

При отказах модулей 1-4 устройст- во работает следующим образом.

Отказ элементов силовой части одного из модулей 1-4, например модуля 2, вызывает изменение напряжения на выходе блока 36 допускового контроля напряжения датчика 28 отказа от уровня логической единицы до уровня логического нуля, при этом спад им

пульса на входе С триггера 19 вызывает переход триггера 19 в нулевое состояние (на выходе Q - логический

нуль, на выходе Q - логическая единица) . Датчик 28 отказа по выходу 32.1 переходит в нулевое состояние, а формирователь 39 коротких импульсов по выходу 32.3 генерируют короткий импульс напряжения с уровнем логической единицы. Импульс через элемент ИЛИ 18 и 15 поступает на тактирующий вход регистра 20 и своим фронтом осуществляет сдвиг логической единицы

5 вправо (с первого на второй вывод).

Так как на вход распределителя 21 поступают импульсы со счетчика- делителя 9, имеющего коэффициент деления для данной схемы, равный восьми, то период следования тактовых .импульсов составит Т/3. -Распределитель 21 и блок 22 логики переключения распределяют импульсы последовательно по модулям 1-4, минуя отказавший модуль. Следовательно, при отказе одного модуля период перекпючения ключевого транзистора модуля сохраняется, но временный сцвнг между процессами в модулях изменяется и становится

0 равным: Т/3.

0

5

ителя 21 поступают со счетчика-делите-

ля 10. Так как коэффициент деления счетчика-делителя 10 равен 12, то период следования тактовых импульсов составляет Т/2. Распределитель 21 и блок 22 логики переключения распределяют тактовые импульсы только по двум работоспособным модулям 1 и 4, частота переключений ключевых транзисторов модулей 1 и 4 не изменяется.

Ремонт устройства заменой отказавших модулей 1-4 исправными без отключения потребителя осуществляется следующим образом.

После замены отказавшего модуля 2 на исправили кратковременным нажатием кнопки 40 триггер 37 датчика 38 отказа переводится в единичное состояние (на выходе Q - логическая еди0

10

15

7 J628057

ница). На его выходе 32.1 появляется напряжение логической единицы, поступающее на вход блока 22 логики переключения и разрешающее подключение к распределителю 21 модуля 2. Одновременно на выходе 32.4 появляется импульс отрицательной полярности (в нажатом состоянии кнопки 40 уровень напряжения на выходе 32.4 равен логическому нулю). Так как на соответствующем входе элемента И J6 появляется логический нуль при логической единице при остальных входах, на выходе данного элемента И имеет место логический нуль. При поступлении логического нуля на установочный вход R триггер 19 изменяет состояние на противоположное (на выходе Q - логический нуль, на выходе Q - логическая единица).

Уровни напряжений на входах SR и SL регистра 20 изменяются (на входе SR - логический нуль, на входе SL - логическая единица), при этом регистр 25 20 подготовлен для сдвига логической единицы (в сторону уменьшения номеров выходов).

Очередной тактовый импульс, поступающий на модуль 2, включает модуль На выходе блока 36 допускового контроля напряжения датчика 28 отказа появляется напряжение логической единицы, поступающее на вход С триггера

37и на вход формирователя 38 коротких импульсов. Триггер 37 не меняет своего состояния, а формирователь

38генерирует по выходу 32.2 короткий импульс с уровнем логической единицы. 11мпульс через элемент ИЛИ 17 поступает на вход С триггера 19 и через элемент ИЛИ 15 на вход С регистра 20. Фронтом этого импульса осуществляется сдвиг логической единицы влево (с третьего выхода на второй). При этом тактовые импульсы поступают на вход распределителя 21 со счетчика-делителя 9 через элемент И 12. Поскольку период поступления тактовых

8

Замена второго отказавшего мод в данном случае модуля 4, и ввод в работу происходят аналогично, п этом осуществляется сдвиг логиче кой единицы с второго на первый вы регистра 20. Тактовые импульсы на распределитель 21 доступают со сче чика-делителя 8 с периодом поступ ления Т/4, сохраняя при этом пер переключения ключевых транзисторо модулей неизменным.

Схема может быть распространен на п модулей многофазного парамет ческого стабилизатора.

Таким образом, изобретение обес чивает работоспособность устройств при отказах всех, за исключением -двух, модулей и его ремонт заменой 2о на исправные модули без отключения потребителя, Ремонт может быть осу шествлен заменой всех или только части отказавших модулей.

Формула изобретени

30

Многофазный параметрический ста билизатор напряжения постоянного тока, содержащий п включенных пара лельно между выводами для подключе ния первичного источника питания и нагрузки преобразовательных модуле каждый из которых состоит из после довательно соединенных ключевого 35 элемента и DLC-фильтра, управляемы делитель частоты с собственно делителем частоты, вход которого под ключен к выходу генератора тактовы импульсов, п-1 двухвходовыми элеме тами И, первые входы которых соеди нены с соответствующими выходами делителя частоты, регистром сдвига выходы которого подключены к вторы входам двухвходовых элементов И, (п-I)-входовым элементом ИЛИ, вхо которого соединены с выходами дву входовых элементов И, и первым п- входовым элементом ИЛИ, распредели тель тактовых импульсов, тактирующ

40

45

импульсов равен Т/3 при трех работаю- gg вход которого подключен к выходу

(п-1)-входового элемента ИЛИ управ ляемого делителя частоты, п формирователей ширины импульсов, входы которых соединены с соответствующи 55 выходами распределителя тактовых

щих модулях, период переключения ключевых транзисторов модулей сохраняется. Спадом того же короткого импульса формирователя 38, поступившего на вход С триггера 19, последний переключается в исходное состояние (на выходе Q - логическая единица, на выходе Q - логический нуль), готовя регистр 20 к сдвигу вправо.

57

8

Замена второго отказавшего модуля, в данном случае модуля 4, и ввод его в работу происходят аналогично, при этом осуществляется сдвиг логической единицы с второго на первый выход регистра 20. Тактовые импульсы на распределитель 21 доступают со счетчика-делителя 8 с периодом поступления Т/4, сохраняя при этом период переключения ключевых транзисторов модулей неизменным.

Схема может быть распространена на п модулей многофазного параметрического стабилизатора.

Таким образом, изобретение обеспечивает работоспособность устройства при отказах всех, за исключением двух, модулей и его ремонт заменой на исправные модули без отключения потребителя, Ремонт может быть осу- шествлен заменой всех или только части отказавших модулей.

Формула изобретения

Многофазный параметрический стабилизатор напряжения постоянного тока, содержащий п включенных параллельно между выводами для подключения первичного источника питания и нагрузки преобразовательных модулей, каждый из которых состоит из последовательно соединенных ключевого элемента и DLC-фильтра, управляемый делитель частоты с собственно делителем частоты, вход которого подключен к выходу генератора тактовых импульсов, п-1 двухвходовыми элементами И, первые входы которых соединены с соответствующими выходами делителя частоты, регистром сдвига,, выходы которого подключены к вторым входам двухвходовых элементов И, (п-I)-входовым элементом ИЛИ, входы которого соединены с выходами двухвходовых элементов И, и первым п- входовым элементом ИЛИ, распределитель тактовых импульсов, тактирующий

вход которого подключен к выходу

(п-1)-входового элемента ИЛИ управляемого делителя частоты, п формирователей ширины импульсов, входы которых соединены с соответствующими выходами распределителя тактовых

импульсов, а выходы - с управляющими входами соответствующих преобразовательных модулей, п- датчиков отказа каждый из которых первым выходом ,

через блок логики переключения, предотвращающий пуск отказывающих прербразовательных модулей, подклю-. чен к соответствующему управляющему входу распределителя тактовых импульсов, вторым выходом соединен с одним из входов первого n-входового элемента ИЛИ управляемого делителя частоты и выполнен с двухполупернод- ным выпрямителем, соединенным входом с сигнальным выходом соответствующего преобразователя модуля, блоком допускового контроля напряжения, подключенным входом к выходу выпрямителя, и первым формирователем коротких импульсов, выход которого использован ъ качестве второго выхода датчика, отличающийся тем, что, с целью повышения надежности работы путем обеспечения ремонта без отключения потребителя, в управляемый делитель частоты введены п входовой элемент И, второй п-вхо- довой элемент ИЛИ, трехвходовой элемент ИЛИ и триггер управления сдвиго а каждый датчик отказа снабжен триггером установки и вторым форм ровв

0

8057

5

0

5

JO

телем коротких импульсов, причем входы n-входового элемента И и нторого nвходового элемента ИЛИ управляемого делителя частоты соединены с третьими и четвертыми выходами датчиков, отказа, входы трехвхрдового элемента ИЛИ подключены к выходам первого и второго n-входовых элементов ИЛИ( а выход - к тактирующему входу регистра сдвига, тактирующий вход триггера управления сдвигом соединен с выходом первого n-входового элемента ИЛИ, установочный вход - с управляющими входами регистра сдвига, в каждом датчике отказа тактирующий вход триггера установки и вход первого формирователя коротких импульсов подключены к выходу блока допускового контроля напряжения, вход второго форми- рователя коротких импульсов соединен с инверсным выходом триггера установки, первым выходом датчика использован прямой выход триггера установки, третьим выходом - выход второго формирователя коротких импульсов, а четвертым выходом - установочный вход триггера установки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления группой из @ объединенных по выходу тиристорных преобразователей | 1986 |

|

SU1394376A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Многофазный параметрический стабилизатор постоянного напряжения | 1989 |

|

SU1658130A1 |

| Устройство для @ -канального импульсного регулирования мощности в @ -фазной сети | 1985 |

|

SU1354359A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1985 |

|

SU1348801A1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ ОТКЛОНЕНИЙ ПАРАМЕТРОВ ПРИ ДОПУСКОВОМ КОНТРОЛЕ | 2016 |

|

RU2617982C1 |

| Устройство для управления многофазным импульсным преобразователем | 1990 |

|

SU1791943A1 |

| Многофазный импульсный стабилизаторпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU824161A1 |

Изобретение относится к электротехнике, в частности к источникам вторичного электропитания. Цель изобретения - повышение надежности работы путем обеспечения ремонта без отключения потребителя. Стабилизатор содержит преобразовательные модули, генератор тактовых импульсов, управляемый делитель частоты, распределитель тактовых импульсов, блок логики переключения, формирователи ширины импульсов, датчики отказа. В каждый из последних входят двухчолу- периодный выпрямитель, блок допуско- вого контроля напряжения, установки, формирователи коротких импульсов. При отказах и заменах модулей автоматически изменяется период следования тактовых импульсов с выхода управляемого делителя частоты. Это предопределяет и изменение временного сдвига между процессами в модулях. Работоспособность обеспечивается при отказах всех, за исключена м двух, модулей, 2 ил. о е ел

| Многофазный параметрический стабилизатор напряжения | 1985 |

|

SU1265742A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Многофазный параметрический стабилизатор постоянного напряжения | 1987 |

|

SU1483439A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-02-15—Публикация

1988-10-18—Подача