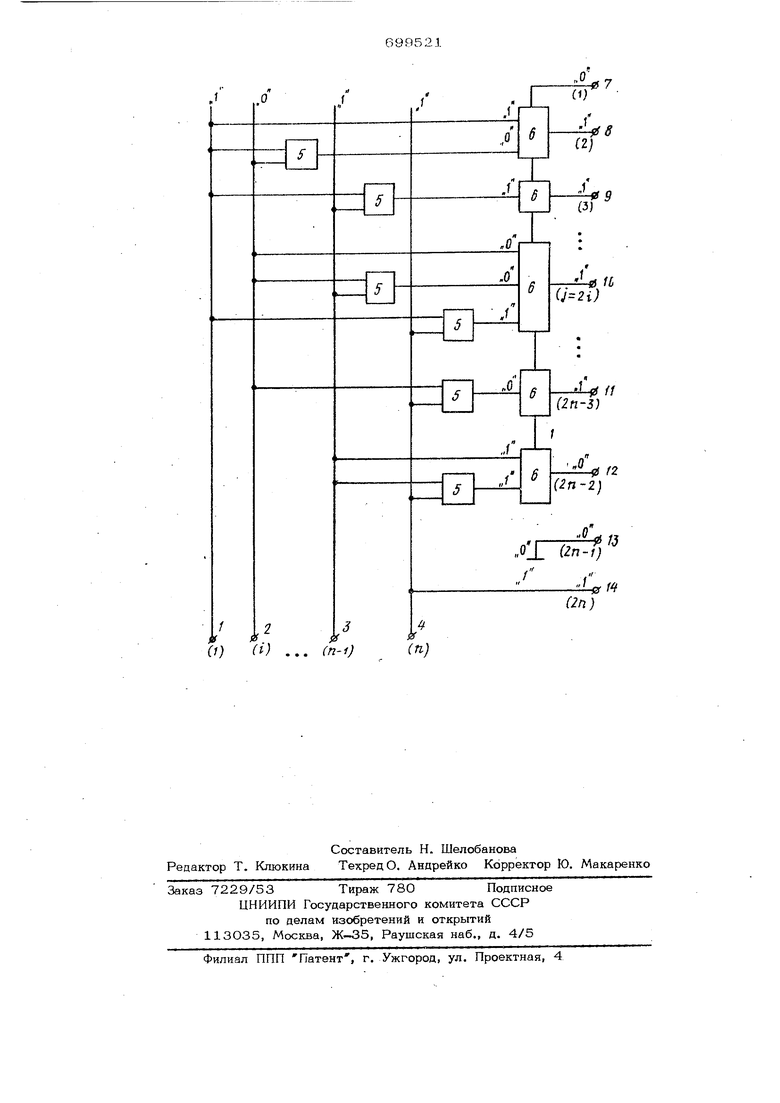

Изобретение относятся к цифровой вычислительной технике, предназначено для возведения в квадрат П -разрядных двоичных чисел и может быть использовано в информационно-измерительных системах в качестве решающего блока 1для оперативной обработки информации. Известны устройства, позволяющие получать на их выходах значение кода, равное квадрату входной величины, пред ставляющих собой совокупность логических схем, количество и связи между которыми определяют аппаратурные затраты и быстродействие всей схемы в целом l. Из известных устройств наиболее близким к изобретению по своей технической сущности является устройство для возведения в квадрат Irl - разрядных дв ичных чисел, содержащее одноразрядные сумматоры, последовательно соединенные межразрядными связями переноса, входы которых соединены с выходами элементов И, а выходы - с 3 -ыми ( 1 ... 211-2) выходами устройства, (2ть1)-ый и 2 tt-ый выходы устройства подключены соответственно к шине информационного нуля и к п-ому входу устройства 2. Недостатком данного устройства явля-, ются большие аппаратурные затраты. Цель изобретения - упрощение устрой- ства. Это достигается тем, что в устройстве для возведения в квадрат tl -разрядных двоичных чисеЛ( содержащем одноразрядные сумматоры, последовательно соединенные межразрядными связями переноса, входы которых соединены с выходами элементов И, а выходы - с -ыми ( i 1.,. 211-2) выходами устройства, ( 2 tl -1) и 2 tl ный выхойы устройства подключены соответственно к шине информационного нуля и к П-ому входу устройства, 1-ый вход (i .,. П- 1) устройства соединен непосредственно с входом одноразрядного сумматора, выход суммы которого соединен с 2i выходом устройства, 6-ый вход устройства (,3... 3 6995 ... -ц} соединен с первыми вхопами () -юго элементов И, вторые вхоцы которых аоаключены к ,-ому (к-1,2... -1) входу устройства. На чертеже представлена фуикционоль- з ная схема пгдадлагаемого устройства для случая возведения в квадрат четырехразрядных чисел (). ,, . Устройство содержит входы 1-4, элементы И 5, одноразрядные суммато- ° , ры о, выходы 7-14. Устройство работает следующим обра- . На вход 1- по ::тупает значение старше- го разряда возводимого в квадрат числа, а значение старшего разряда результата снимается с выхода /. На вход 4 поступает значение младшего разряда возводимого в квадрат числа, а значение младшего разряда результата снимается с выхода 14. Например, при поступлении на входы 1-4 устройства четырехразряд- J.- jv, 1 - 7 14 по иого кода - и . , окончанию переходных процессов в схеме . установится значение кода У О1111О01, соответствующее квадрату исходного значения входного кода X (состояния элементов схемы (см.на чертеже). Количество элементов И при. четырехразрядном представлении информации равно шести. При реализации известного устройства потребовалось бы девять апементов И-НЕ и шесть элементов НЕ. При ц-разрядном представлении информадии для реализации схемы известного устройства необходимо - элемен.тов И-НЕ и,2п-2 элементов НЕ. Предложенная схема устр ойства реализуется с использованием Д элементов И. ; 214 Таким обралом,-использовгишо-продло- же1гной схемы устройства, позволяет сущоственно уменьшить аппаратурные затраты, что, в свою очередь, позволяет повыситг. надежность работы и уменьшить по- требляемую мощность устройства в целом, ь Формула из обретения ,. Устройство для возведения в квадрат tl -разрядных двоичных чисел, содержа- щее одноразрядные сумматоры, последовательно соединенные межразрядными связями переноса, входы которых соеди выходами элементов И, а выходы . . 2п-2) выходами устJ (2-п-1) и 2|1-ый выходы устройства подключены соответственно информационного нуля и к tl-юму устройства, отличающее тем, что, с целью упрощения, i-ый / i - вход-{т 1...11-1) устройства соединен непосредственно с входом одноразрядно- сумматора, выход суммы которого соединен с 2, выходом устройства, g,.. Устройства (В 2,3... П) сое первыми входами ( Е-1)-ого элементов «И, вторые входы которых к i (,2... 6-1) входу „ - „о устройство. Источники информации, во внимание при экспертизе Прангишвили И, В. и др. Микроэлектроника и однородные структуры для построения логических и вычислительных устройств. . М., -Наука% 1967. с. 180. Авторское свидетельство СССР по , 2475297/24 от 31.10.77 (прототип).

.,0

(I) ... (n-i)

7

/J

nff

(2п)

0 (п)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат п-разрядных чисел | 1977 |

|

SU631918A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU888104A1 |

| Устройство для возведения в квадрат @ -разрядных двоичных чисел | 1980 |

|

SU951300A2 |

| Устройство для возведения в квадрат @ -разрядных чисел | 1984 |

|

SU1236469A2 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Устройство для возведения в квадрат @ -разрядных двоичных чисел | 1990 |

|

SU1784977A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для возведения п-разрядных чисел в квадрат | 1979 |

|

SU911520A1 |

| Устройство для возведения в квадрат | 1984 |

|

SU1239713A1 |

Авторы

Даты

1979-11-25—Публикация

1978-03-30—Подача