Изобретение относится к цифровой вычислительной технике, в частности к устройствам для обработки данных,- и может быть использовано в -системах моделирования, автоматического управ ления, в устройствах дискретной обработки сигналов.

Цель изобретения - расширение функциональных возможностей в. части обработки как положительных, так и отрицательных чисел, предста влен- ных в дополнительном коде.

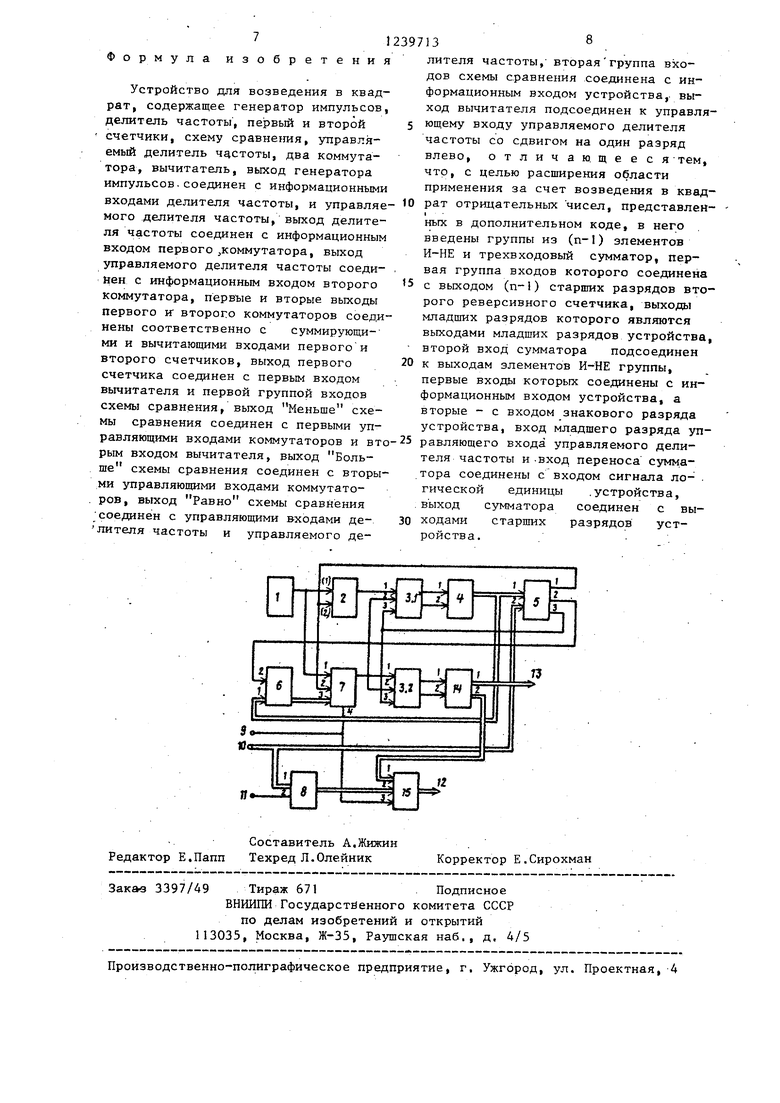

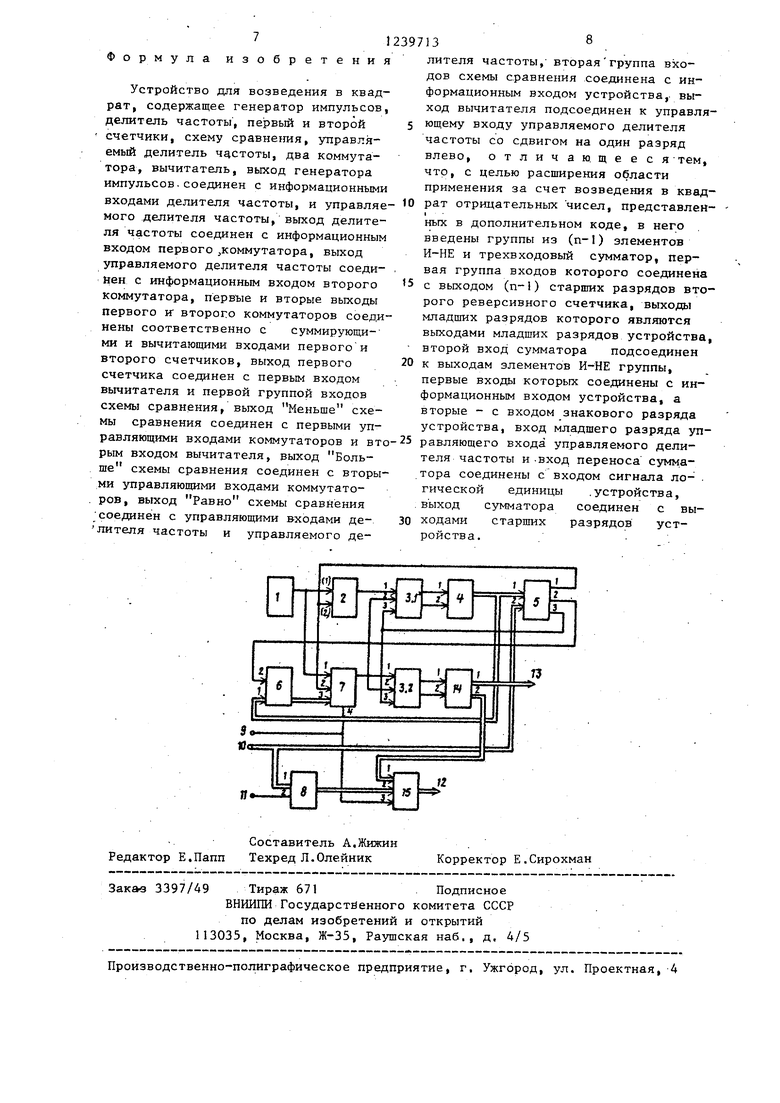

На чертеже представлена функцио- нальная схема предлагаемого устройства,

Устройство содержит генератор I импульсов я делитель 2 частоты, первый и второй коммутаторы.В,1 и 3,2, первый реверсивный счетчик 4, схему 5 сравнения, многоразрядньп вычита- тель 6, управляемый делитель 7 частоты, группу из (п-1) элементов И-- НЕ 8, вход 9 сигнала логической единицы, информационный вход 10, вход 1I знакового разряда, выход 12 старших разрядов, выход 13 младших разрядов, второй реверсивный счетчик 14, трехвходовый многоразрядный сумматор 15.

Устройство работает следующим об-

разом. I

В исходном состоянии делитель 2

частоты, управляемый делитель 7 .частты и реверсивные счетчики . и 14 обнулены. При поступлении на входы устройства кода аргумента X, представленного в дополнительном коде в виде ,Хд,,,.,Х, где X - значение- знакового разряда аргумента, Х ,и Хц - соответственно старший и младпий разряды мантиссы, причем Х- поступает на вход {1 знакового разряда устройства, а значения разрядов мантиссы X поступают на информационный вход 10 устройства, схема 5 сравне- ния. Вырабатывает на выходе Больше значение единицы до тех пор, пока код, поступающий на ее второй вход больше кода, по.ступающего на ее первый вход, в результате действия которой коммутатор 3.1 коммутирует свой первый вход с первым выходом и подключает выход делителя 2 частоты к суммирующему входу реверсивного счетчика 4, а выход управляемого делителя 7 частоты, коммутатор 3,2 подключает к суммирующему входу реверсивного счетчика 14. Когда на выходе

реверсивного счетчика 4 появляется значение кода X, равного коду мантиссы аргумента Х,..,,Х, на выходе Больше схемы 5 сравнения появляется значение логического нуля, а на выходе Равно появляется значение единицы, которое обнуляет делитель 2 частоты и управляемый делитель 7 частоты.

Время Т, за которое на выходе ре- версив ного счетчика 4 накопляется значение кода X,- численно равного коду мантиссы входного аргумента Х ,,,., равно.

Т

где 2

п

- коэффициент деления делителя 2 частоты;

f - частота генератора 1 импуль- . . сов,

На управляюш й вход вычИтателя 6 в течение всего времени Т поступает код О, а на информационньй вход с выхода первого реверсивного счетчика 4 - код у, передаваемый в данном слу- чае без изменения на выход вычитате- ля,

в соответствии со схемой соединения управляемого делителя 7 частоты минимальная частота на его выходе равна. ,

f «-.-.

. nun 2 а максимальная частота но равна

соответствен-.

2(Х-1}+1 2Х-1 тел 2 2

Средняя частота за время Т на выходе управляемого делителя 7 частоты равна

Ч

fmln ffn«i. 5 2 2

.

При этом количество импульсов, поступившее на суммирующий вход реверсивного счетчика 14, равно

пП

X

х

Таким образом, на выходах трех- , входового многоразрядного суммато- 55 ра 15 появляется значение (п-1) старших разрядов квадрата входного аргумента Х,.,.,Х, представленного в дополнительном коде, а на.выходе 13

. 3123

появляются младшие (п+1) разрядов квадрата входного аргумента Х, ., . ,Х. На этом начальный этап работы устройства закончен,

При поступлении на входы 10 и П. устр ойства следующего кода аргумента X ,Х,,,.,Хц схема работает следующим образом.

Если принять для определенности,

что новое значение кода мантиссы ,...,Х по абсолютной величине меньше предьщущего значения кода мантиссы Х ,...,Х на величину, равную ЛХ, т.е.

, тогда схема сравнения вырабатывает значение единицы на выходе Меньше, в соответствии с которым коммутатор 3.1 подключает выход делителя 2 частоты к вычитающему входу реверсивного счетчика 4, а коммутатор 3,2 подключает выход управляемого делителя 7 частоты к вычитающему входу реверсивного счетчика 14,

Схема 5 сравнения вырабатывает значение единицы на выходе Меньше до тех -пор, пока на выходе реверсивного счетчика 4 не появляется значение кода X , равного коду мантиссы аргумента Х,...,Х,. При равенстве их на выходе Меньше схемы 5 сравнения вырабатывается значение логического нуля, а на выходе Равно схемы 5 сравнения - значение единицы, которое, обнуляет делитель 2 частоты и управляемый делитель 7 частоты.

Время Т , за которое на выходе реверсивного счетчика 4 появляется значение кода х , численно равное коду мантиссы аргумента Х,,.,,Х, равно

,п

т 2(Х-х 2

. f , Г .

На управляюш ий вход многоразрядного вычитателя 6 в течение времени Т поступает код 1, в результате на выходе формируется код значения (у-1), код у - код, -поступаю ций на его ин формацирнный вход. Максимальная частота иа выходе управля- емого делителя 7 частоты равна

f 2(Х-1) + 1 2Х-1

2 2 а минимальная частота соответственно равна

f 2i lllll)il f- 2х .+ 1 lin 2

Средняя частота за время Т на . выходе управляемого делителя 7 частоты равна

f - f -Чр 9 I

Количество импульсов Z , поступившее за время т на вычитаюш 1Й вход реверсивного счетчика 14, равно

.x -(x )

Таким образом, на выходе.реверсивного счетчика 14 появляется значение кода, равное

(x -(x )) (x )S

у которог о (п+1) младших разрядов равны (п+1) младшим разрядам квадра-- та аргумента, представленного в дополнительном коде X ,Х ,,,.,Х, . а(п-1) старших разрядов квадрата аргумента, в соответствии со схемой соединения входов трехвходового многоразрядного сумматора 15, снимаются -С выхода 12 старших разрядов устройства.

Аналогично работает схема, если новое значение кода мантиссы X Х( по абсолютной величине больше предыдущего, значения кода мантиссы

V у

J

Работа схемы может быть пройллюстл

рирована также на конкретном численном примере, когда .тактовая часто- та работы генератора 1 импульсов равна 10 Гц, На-вход предлагаемого устройства поступает число ,

представленное в двоичном дополнительном коде с разрядностью мантиссы ,8 разрядов.

Х -220 100100100.

/ч/

При этом, , а численное значение мантиссы аргумента . Время . Т при этом равно

- ..36

f ТО

Средняя частота на выходе управляемого делителя 7 частоты равна

-|-- 10 Гц.

Количество импульсов, поступившее на суммирующий вход реверсивного счетчика 14 равно

Z

2 36

То

p.lo 1296.

.Двоичный код числа Z, представленный 2ц разрядами,- равен

ООООШО

(п-1)

старших разряда

(п+1)

младших

разряда

G выхода группы из (п-1) элементов И-НЕ 8 на второй вход трехвходо- вого многоразрядного сумматора 15 поступает инверсное значение (п-1) младших разрядов мантиссы аргумента, равное.1011011, На первый вход трех- входового многоразрядного сзгмматора 15 поступают значения (п-1) старших разрядрв выходного кода реверсивного счетчика 14 и с учетом того, что на вход переноса тp.exвxoдoвo o много разрядного сумматора 15 значение ло-- Гической единицы поступает только в младший п-й разряд, -на выходе многоразрядного сумматора 15 образуется следующий код 1011110 j так как

0000010 + . 101 101 1

- 1

1011110 ,

который равен старшим (п-1) разряда результата возведения числа в квадрат.

Таким образом

Х 1011110- . ,100010000, (-220) (п-1) стар- (п+1) младшие раз шие разряды ряды результата, результата, снимаемые с выхо- снимаемые с да 13 выхода. 12

При поступлении нового значения , представленного в двоичном дополнительном коде Х.00100000 -224, численное значение мантиссы аргумента , а значение ДХ равно

flX 36-32 4,

.При этом время работы устройства равно

,

2 . 4

с,

Средняя частота на выходе управ- ,ляемого делителя 7 частоты равна

36-4-32 2

О

68

о

10 Гц.

Количество импульсов,, поступившее на вычитающий вход реверсивного счетчика 14, равно

7-T f - e8-(f --1- ГСР YQ-J 2

Таким образом, на выходе- реверсивного .счетчика 14 появляется зна- чение кода, равное

Z 00000101 20Ш00009 (п-1) (п+1), старших младших

разряда,, разряда.

С выхода линейки из (п-1) .элементов И-НЕ на второй вход трехвходово- го многоразрядного сумматора 15 поступает инверсное значение (п-1) младших разрядов кода мантиссы аргумента , т „ е. 1 О П 1 1 1 .

В соответствии с этим на выходе трех входового многоразрядного сумматора 15 получают результат 1100010, так как

0000010

+ 1011111

1

1100010,

кото-рый равен старшим (п-1) разрядам результата возведения числа в квадрат.

Таким образом

- (Х )1 100015

(п- 1) старшие (п-ь 1) младшие .разряды резуль-разряды результата, снимае- тата, снимаемые мые с выхода 12 с выхода 13

В обоих случаях, так как квадрат положительных и отрицательных чисел всегда положительное число, то зна- ковый разряд результата всегда равен нулю.При возведении в квадрат положительных чисел устройство работает аналогично, однако при этом необходимо учитывать, что с выходов (п-1) элементов -И-НЕ всегда будет при этом сниматься код, равный 111111.

10

112397

Формула изобретения

Устройство для возведения в квадрат, содержащее генератор импульсов, делитель частоты, первый и второй 5 счетчики, схему сравнения, управляемый делитель частоты, два коммутатора, вычитатель, выход генератора импульсов.соединен с информационными входами делителя частоты, и управляемого делителя частоты, выход делителя частоты соединен с информационным входом первого коммутатора, выход управляемого делителя частоты соединен с информационным входом второго коммутатора, первые и вторые выходы первого И второго коммутаторов соединены соответственно с суммирующими и вычитающими входами первого и второго счетчиков, выход первого счетчика соединен с первым входом вьтитателя и первой группой входов схемы сравнения, выход Меньше схемы сравнения соединен с первыми управляющими входами коммутаторов и вто рым входом вычитателя, выход Больше схемы сравнения соединен с вторыми управляющими входами коммутато- ров, выход Равно схемы сравнения соединен с управляющими входами де- 30 лителя частоты и управляемого де15

20

Составитель А.Жижин Редактор Е.Папп Техред Л.Олейник

Заказ 3397/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-по.пиграфическое предприятие, г. Ужгород, ул. Проектная, 4

8

лителя частоты, вторая группа входов схемы сравнения соединена с информационным входом устройства, выход вычитателя подсоединен к управляющему входу управляемого делителя частоты со сдвигом на один разряд влево, отличаю, щеес я тем, что, с целью расширения области применения за счет возведения в квадрат отрицательных чисел, представлен- I ных в дополнительном коде, в него

введены группы из (п-1) элементов И-НЕ и трехвходовый сумматор, первая группа входов которого соединена с выходом (п-I) старших разрядов второго реверсивного счетчика, выходы младших разрядов которого являются выходами младших разрядов устройства, второй вход сумматора подсоединен к выходам элементов И-НЕ группы, первые входы которых соединены с информационным входом устройства, а вторые - с входом знакового разряда устройства, вход младшего разряда управляющего входа управляемого делителя частоты и-вход переноса сумматора соединены с входом сигнала ло- . гической единицы .устройства, выход сумматора соединен с выходами старших разрядов устройства.. .

Корректор Е.Сирохман

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для извлечения квадратного корня | 1982 |

|

SU1136155A1 |

| Устройство для деления | 1984 |

|

SU1226444A1 |

| Устройство для вычисления логарифмов чисел | 1981 |

|

SU972504A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1359778A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для отображения информации | 1972 |

|

SU458004A1 |

| Преобразователь комплексных сигналов | 1983 |

|

SU1104525A1 |

Изобретение.относится к облас ги цифровой вычислительной техники и может использоваться в различных систе1мах моделирования и автоматического управления, в системах с аппаратурной реализацией функций, где необходимо возводить в квадрат квантованные по времени и по уровню, функции. Цель изобретения - расширение функциональных возможностей в части обработки как положительных, так и отрицательных чисел, пред- ставленных в дополнительном коде. Устройство для возведения в квадрат содержит генератор импульсов, два реверсивных счетчика, делитель частоты нуправляемый делитель частоты, два коммутатора, схему сравнения, вычитатель, .сумматор, группу из (п- -1.) злементов И-НЕ. 1 ил.

| Квадратор | 1979 |

|

SU881739A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1198517, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-23—Публикация

1984-06-20—Подача