1

Изобретение относится к области цифровой вычислительной техники и предназначено для возведения.в квадрат двоично го аргумента.

Известны устройства ij, позволяющие полушть на юс выходах значение кода, равное квадрату от входной велнч1гны. Эти устройства представляют собой совокутгость известных логичестшх схем, число которых и связи менсду ними определяют аппаратурные затраты и быстродействие всей схемы в целом.

Из известных устройств наиболее близким но своей, технической сущности является устройство для возведения в квадрат YI -разрядных чисел, содержащее одноразрядные суг1маторъ, последЬватегхьно соед1-гаеннь е межразр.чдными связями пертноса, и двухвходовые элементы Й-НЕ, выходы которых соединены со входами Ьоответствующнх одноразрйД15ых сумматоров.

Известная схема может бьгть реализована с помощью шсбого известного в двоичной арифметике функционально полного набора элементов с использованием известных логических выражений, позволяюЩ1К представгггь 4ункцшо I логического умножения Б заданном базисе.

Однако при таком подходе для построения схемы прототипа с использованием базиса И-НЕ для реализан ш Я ячеек умноже шя требуется И схем, реализующих операцию И-НЕ и Я инверторов. Целью изобретения является упрощение уотройства.

Поставленная цель достигается тем, что предложенное устройство содержит (2ft -2) элементов НЕ, входы которых (начиная со второго) соединенБ с выходак1и сум5,ы одноразрядных сумматоров. . Выход перюноса старшего разряща одно- разрзшного сумматора соединен со входом первого элемента Не, а выходы всех sлe feнтoв Не явл$потся выхсэдами устройства, (2(t-l) - и и 2П -и выходы устройства соедт ены соответственно с нулевой и И -и входной шинами устройства. Первьш ачоды двухвходовых элементов И-Не (1 - . 1) соединены с i -и входной шиной, а вторые входы - с К-й входной шинсй (к «1, ..,,) устройства.

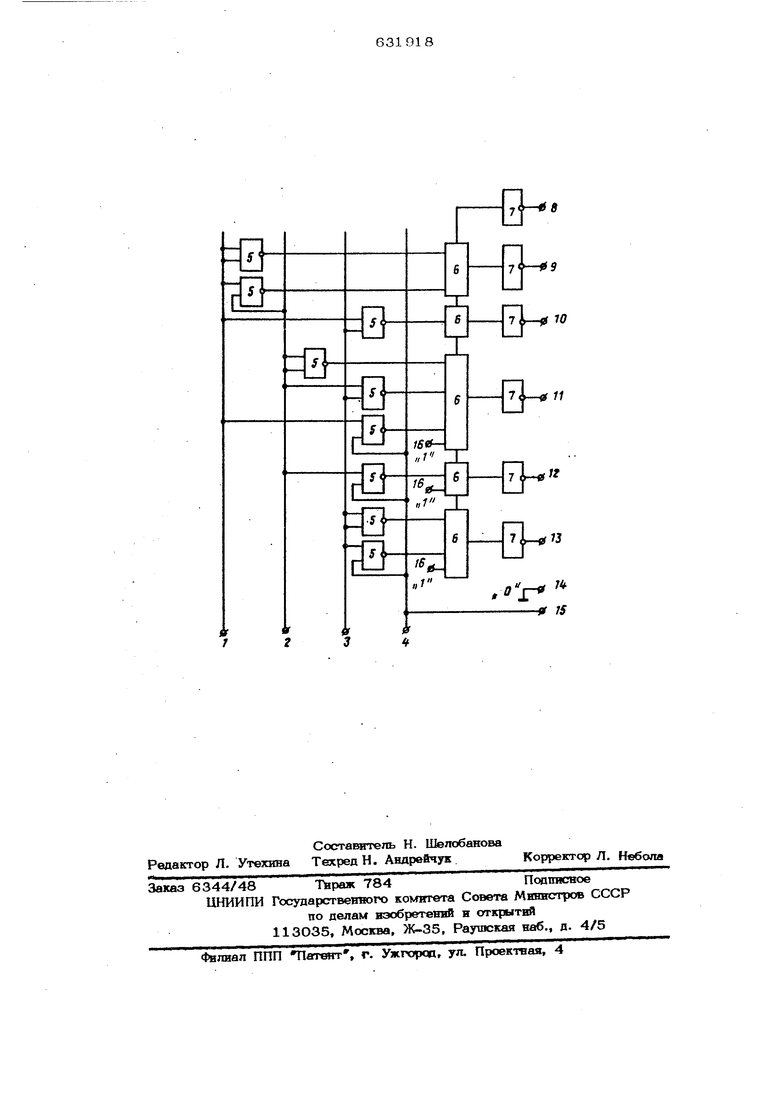

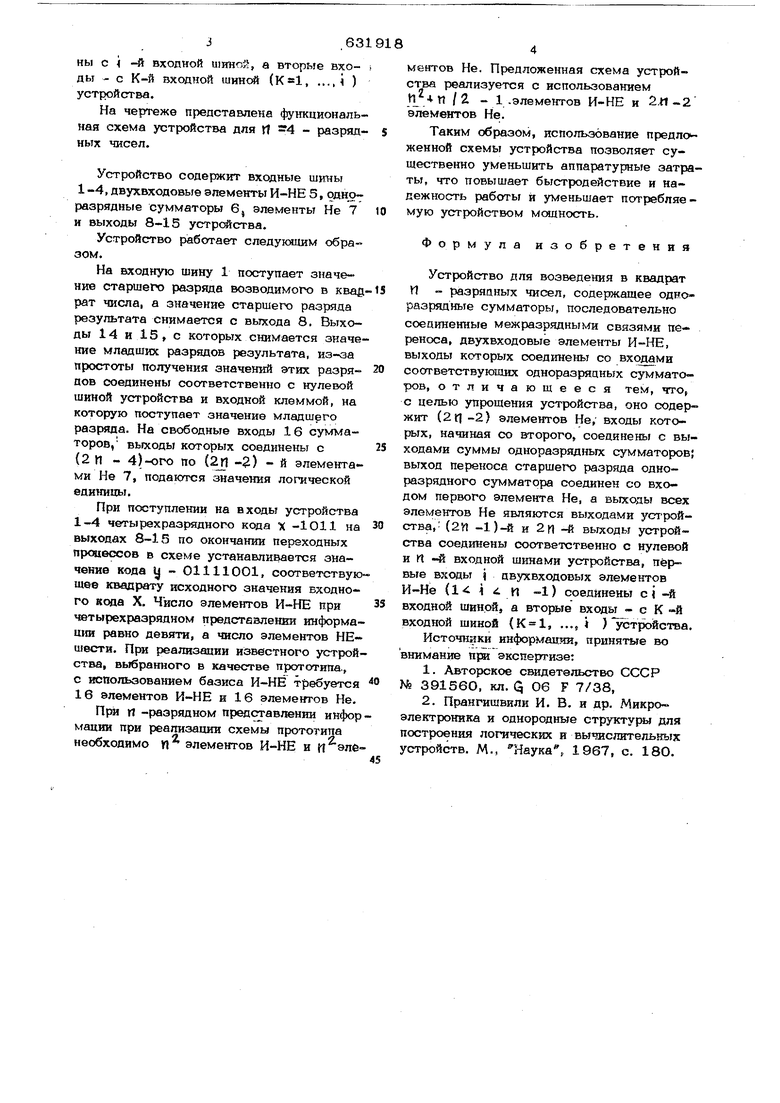

На чертеже представлена функциональная схема устройства для Ц -4 - paspsinных чисел.

Устройство содержит входные шины 1 -4, двухвходовые элементы И-НЕ 5, одно разрядные сумматоры 6, элементы Не 7 и выходы 8-15 устройства.

Устройство работает следующим обра зом.

На входную шину 1 поступает значение старшего разряда возводимого в кваврат числа, а значение старшего разряда результата снимается с выхода 8, Выходы 14 и 15 , с которых снимается значение младших разрядов результата, из-за простоты получения значений этих разрядов соединены соответственно с нулевой шиной устройства и входной клеммой, на которую поступает значение младшего разряда. На свободные входы 16 сумматоров, выходы которых соединены с (2 И - 4)-ого по (2j1 -2) - и элементами Не 7, подаются значения логической единицы.

При поступлении на входы устройства 1-4 четырехразрядного кода X -1011 на выходах 8-15 по окончании переходных процеесов в схеме устанавливается значение кода у - 011110О1, соответствующе© квадрату исходного значения входного кода X. Число элементов И-НЕ при четырехразрядном представлекви информации равно девяти, а число элементов НЕ шести. При реализации известного устройства, выбранного в качестве прототипа,, с кюпользованием базиса И-НЁ требуется 16 элементов И-НЕ и 16 элементов Не.

При rl -разрядном предсп-авлении информации при реализации схемы прототипа

необходимо П элементов И-НН и Ц элементов Не. Предложенная схема устройства реализуется с использованием /2 - 1-элементов И-НЕ и 2.«-2 элементов Не.

Таким образом, использование предло женной схемы устройства позволяет существенно уменьшить аппаратурные затраты, что повышает быстродействие и надежность работы и уменьшает потребляе мую устройством мсядность.

Формула изобретения

Устройство для возведения в квадрат И - разрядных чисел, содержащее одноразрядные сумматоры, последовательно соединенные межразрядными связями переноса, двухвходовые элементы И-НЕ, выходы которых соединены со входами соответствующих одноразрядных сумматоров, отличающееся тем, что с целью упрощения устройства, оно содержит (2Г1 -2) элементов Не, входы которых, начиная со второго, соединены с выходами суммы одноразрядных сумматоров выход переноса старшего разряда одноразрядного сумматора соединен со входом первого элемента Не, а выходы всех элементов Не являются выходами устройства, (2М -1)-й и 211-й выходы устройства соединены соответственно с нулевой и И -и входной шинами устройства, первые входы i цвухвходовых элементов И-Не (: i i и -1) сюедйиены ci -и входной шиной, а вторые входы - с К -и входной щиной (К 1, ...J i ) устройства

Источники информации, принятые во внимание при экспертизе:

1.Авторское сщадетельство СССР N9 391560, кл. Q Об F 7/38,

2.Прангишвили И. В. и др. Микро электроника и однородные структуры для построения логических и вы шслительных устройств. М., Наука , 1967, с. 180.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат п-разрядных двоичных чисел | 1978 |

|

SU699521A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU888104A1 |

| Устройство для возведения в квадрат @ -разрядных чисел | 1984 |

|

SU1236469A2 |

| Устройство для определения обратной величины числа | 1974 |

|

SU546881A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Устройство для нормализации двоичных чисел | 1979 |

|

SU783792A1 |

| Устройство для возведения в квадрат @ -разрядных двоичных чисел | 1980 |

|

SU951300A2 |

| Устройство для преобразования прямоугольных координат в полярные | 1979 |

|

SU781834A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Устройство сдвига | 1979 |

|

SU809387A1 |

Авторы

Даты

1978-11-05—Публикация

1977-04-08—Подача