Изобретение относится к вычислительной технике и может быть использовано в устройствах оперативной обработки информации.

Известны устройства для возведения в квадрат n-разрядных двоичных чисел, представляющие собой совокупность сумматоров и логических элементов и осуществляющие операцию возведения чисел в квадрат за один такт, например, 1,

Яедостатком этих устройств являются значительные аппаратурные затраты, быстро возрастающие с увеличением п.

По техническому решению наиболее близким к заявляемому устройству является устройство для возведения в квадрат п-разрядных двоичных чисел, которое содержит разрядные сумматоры, последовательно соединенные межразрядными связями переноса, и элементы И, входы сумматоров соединены с выходами элементов И, а выхо- 1, 2,..., 2п-2) выходами устройства, (2п-1)-й и 2п-й выходы устройства подключены соответственно к шине информационного нуля и к п-му Входу устройства, 1-й вход (,2,.... п-1) устройства соединены непосредственно со входом разрядного сумматора, выход суммы которого соединен выходом устройства, 1-й вход устройства (1 2,3п) соединен с первым входом

(И)-го элемента И, второй вход которого

подключен к k-му (k 1, 2 1-1) входу

устройства 2.

ч

00 4

xi

Х4

Недостатком этого устройства является то, что оно требует значительных аппаратурных затрат при больших значениях п.

Цель изобретения - сокращение аппаратурных затрат на реализацию устройства для возведения в квадрат n-разрядных двоичных чисел при больших значениях п.

Поставленная цель достигается тем, что в устройство йЪзведения в квадрат п- разряднйх двоичных чисел, содержащее элементы 1Л и цепочку иЗ последовательно сое диненн1ых1 hcf переносу разрядных сумматоров, выход суммы 1-го разрядного сумматора 0 1.22п-3) соединен с выходом

0+2)-го разряда устройства, выход последнего разряда которого соединен с выходом переноса последнего разрядного сумматора, выходы первого и второго разрядов устройства подключены ко входу первого разряда исходного двоичного числа и входу логического нуля устройства соответственно, вход k-ro разряда исходного двоичного

числа ( 2. 3п) соединен со входом 1-го

разрядного сумматора (I - 1. 3, 52п-3),

дополнительно введены (р-1) дешифраторов значений пар двоичных разрядов исходного числа (где р - п/2. округленное до ближайшего большего целого), блок предварительной обработки и блок формирования частичных квадратов, причем первый и второй входы (m-1)-ro дешифратора значений пар двоичных разрядов исходного числа

(т 2, 3 р; т - номер пары двоичных

разрядов исходного числа) соединены соответственно со входами (2гл-1) и 2m-ro разрядов исходного двоичного числа устройства, блок предварительной обработки содержит (2р-2) двоичных полусумматоров и цепочку из (2р-3)-х последовательно соединенных по переносу двоичных сумматоров, причем, вход переноса первого двоичного сумматора соединен со входом логического нуля устройства, вход первого разряда исходного двоичного числа устройства подкпючен к первому входу первого двоичного сумматора, вход r-го разряда исходного двоичного числа устройства (г 2, 3, .., 2р-3) соединен с первым входом г-го двоичного сумматора, вторым входом (г-1)- го двоичного сумматора и первым входом (г-1)-го двоичного полусумматора, вход (2р- 2)-го разряда исходного двоичного числа устройства подключен ко второму входу (2 р- 3)-го двоичного сумматора и первому входу (2р-3)-го Двоичного полусумматора, вход (2р-1)-го разряда исходного двоичного числа устройства соединен с первым входом (2р-2)-го двоичного полусумматора, выход переноса q-ro двоичного сумматора (q 1, 3.5,. , 2р-3)соединен со вторым

входом q-ro двоичного полусумматора, выход переноса которого подключен ко второму входу (q+1)-ro двоичного полусумматора, а блок формирования частичных

квадратов содержит элемент И и (р-1) линеек элементов И и ИЛИ, причем, каждая т-я

линейка (т 2, 3 р) состоит из (2т-1)

элементов ИЛИ и трех групп элементов И по (2т-2), (2т-2) и (2т+1) элементов И соответ0 ственно, в каждой линейке первые входы

а-х (а 1, 22т-2) элементов И первой и

второй групп соединен со входами а-х разрядов исходного двоичного числа устройства, а вторые входы подключены,

5 соответственно, к первому и второму выходам (m-1)-ro дешифратора значений пар двоичных разрядов исходного двоичного числа, выходы элементов И первой группы соединены со входами а-х элементов ИЛИ т-й

0 линейки, выходы элементов И второй группы подключены ко входам (а+1)-х элементов ИЛИ той же линейки, первый вход первого элемента И третьей группы соединен со входом первого разряда исходного двоичного

5 числа устройства, первые входы b-х элементов И третьей группы (Ь 2, 3, .... т-2) т-й линейки подключены к выходам сумм с-х двоичных сумматоров (с 1, 22т-3) блока предварительной обработки, ггервые

0 входы (2m-1)-ro и 2т-го элементов И третьей группы m-й линейки соединены с выходами сумм соответственно (2m-3)-ro и (2m-2)-ro двоичных полусумматоров блока предварительной обработки, первый

5 вход (2m+1)-ro элемента И третьей группы m-й линейки соединен с выходом переноса (2т-2)-го двоичного полусумматора блока предварительной обработки, вторые входы элементов И третьей группы m-й линейки

0 подключены к третьему выходу (т-1)-го дешифратора, выходы d-x элементов И

третьей группы (d 1,22m-1) соединены

со входами d-x элементов ИЛИ той же линейки, выходы которых подключены ко вхо5 дам h-x разрядных сумматоров (h 2m-2,

2m-1 4гл-4), выходы 2m-ro и (2m+1)-ro

элементов И третьей группы той же линейки соединены со входами, соответственно, (4m-3}-ro и (4т-2)-го разрядных сумматоров,

0 первый и второй входы элемента И блока формирования частичных квадратов соединены соответственно со входами первого и второго разрядов исходного двоичного числа устройства, а выход элемента И под5 ключей к входу первого разрядного сумматора, да

Дополнительно введенные элементы и связи в сочетании с известными позволяют при больших значениях п уменьшить в 1,3- 1,4 раза общие аппаратурные затраты на

реализацию устройства за счет сокращения количества входов в разрядных сумматоров в 1,6-1,9 раза и уменьшения аппаратурных затрат на построение этих, наиболее объемных узлов устройства, примерно в 2 раза.

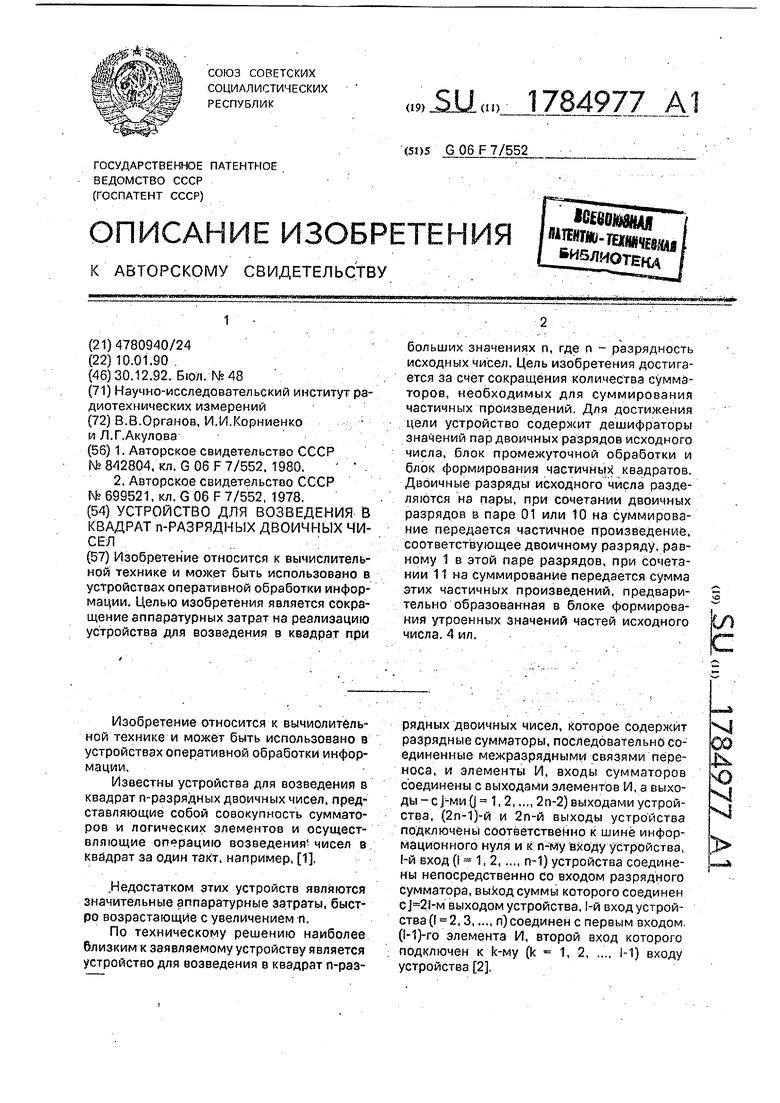

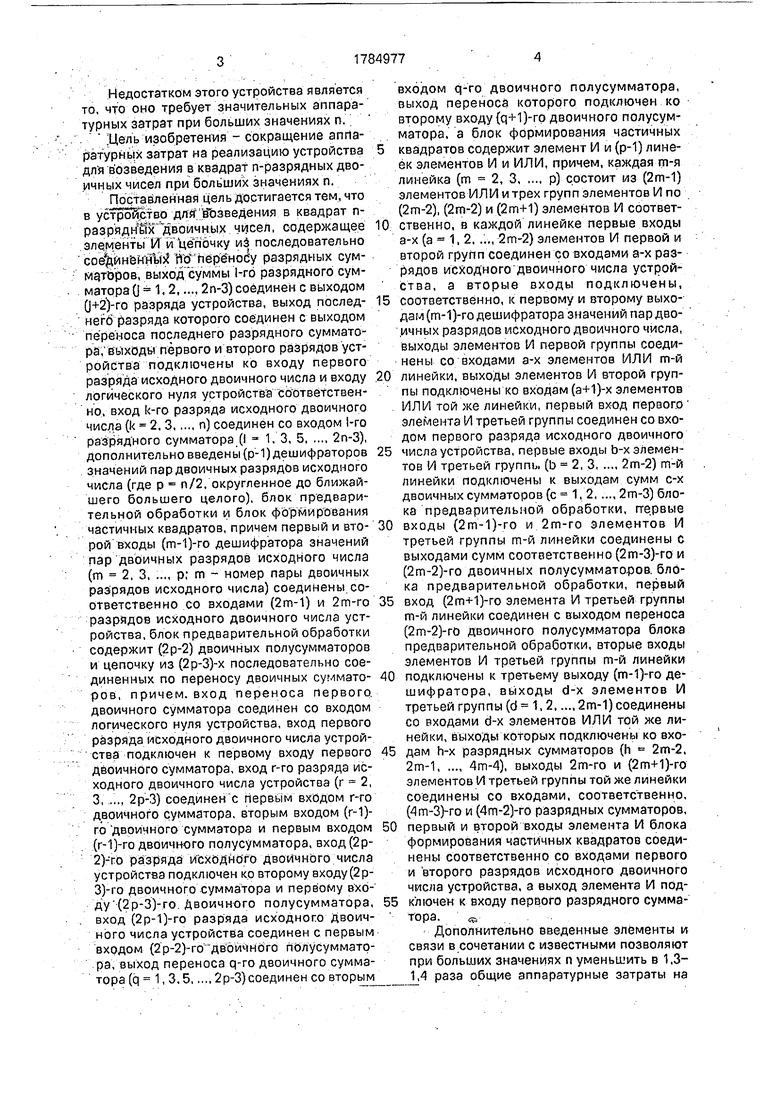

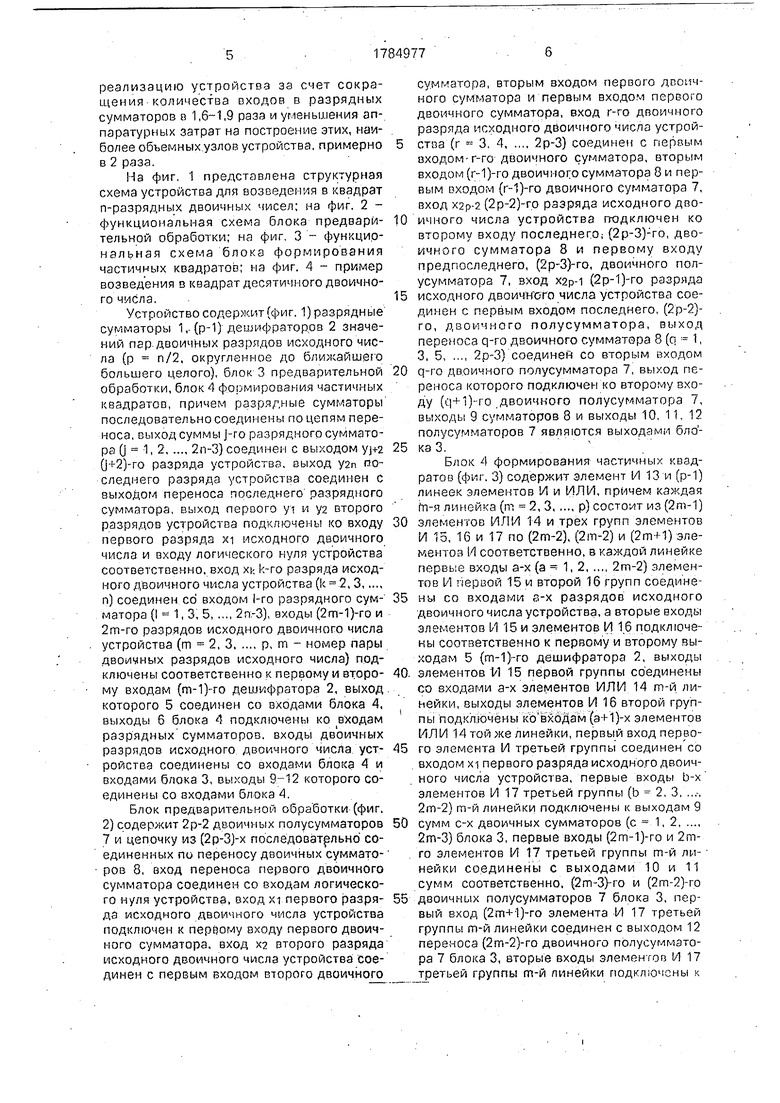

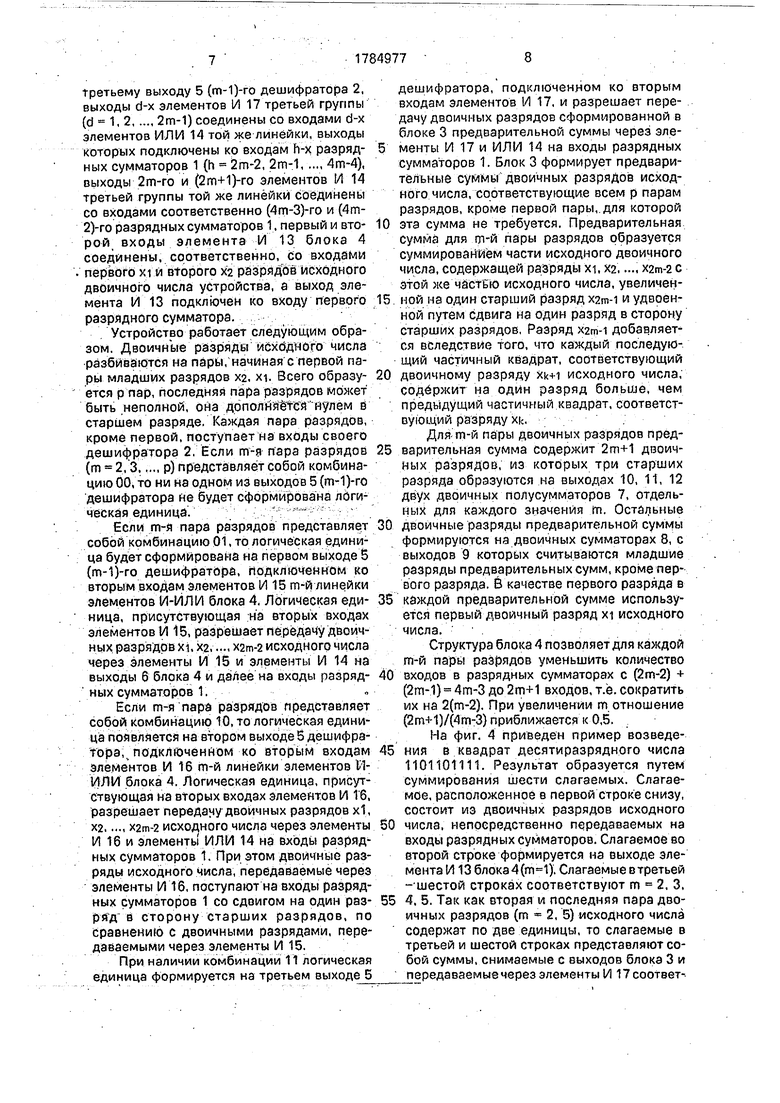

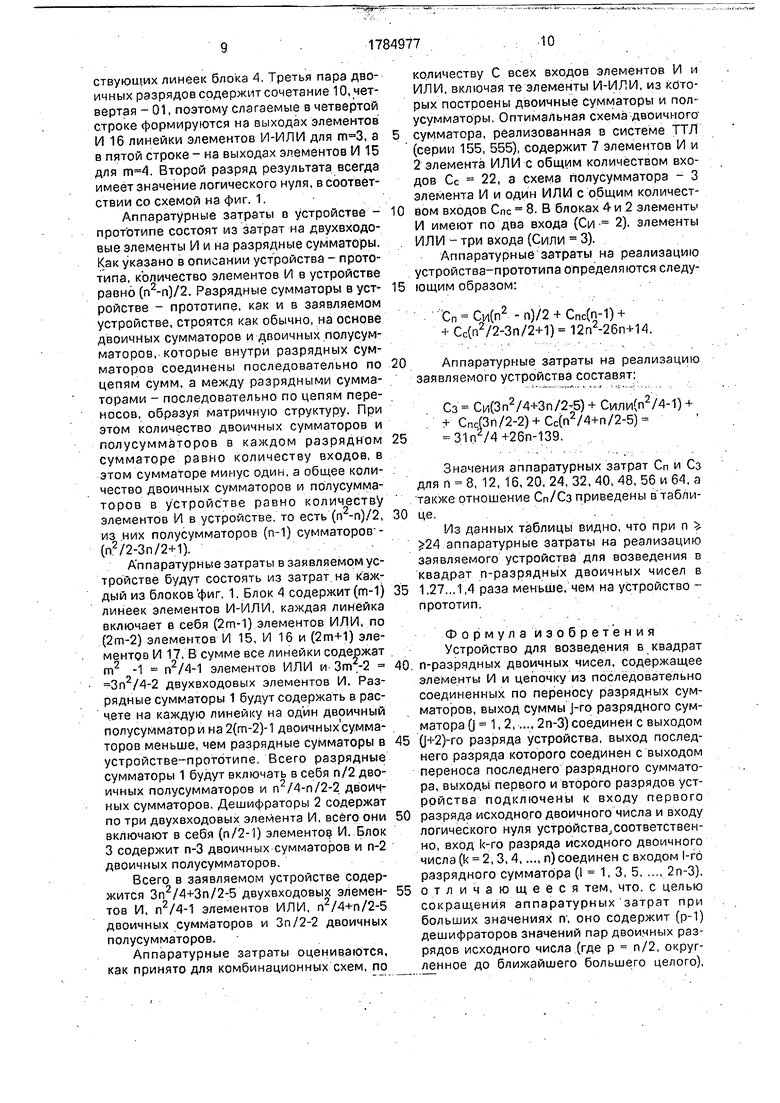

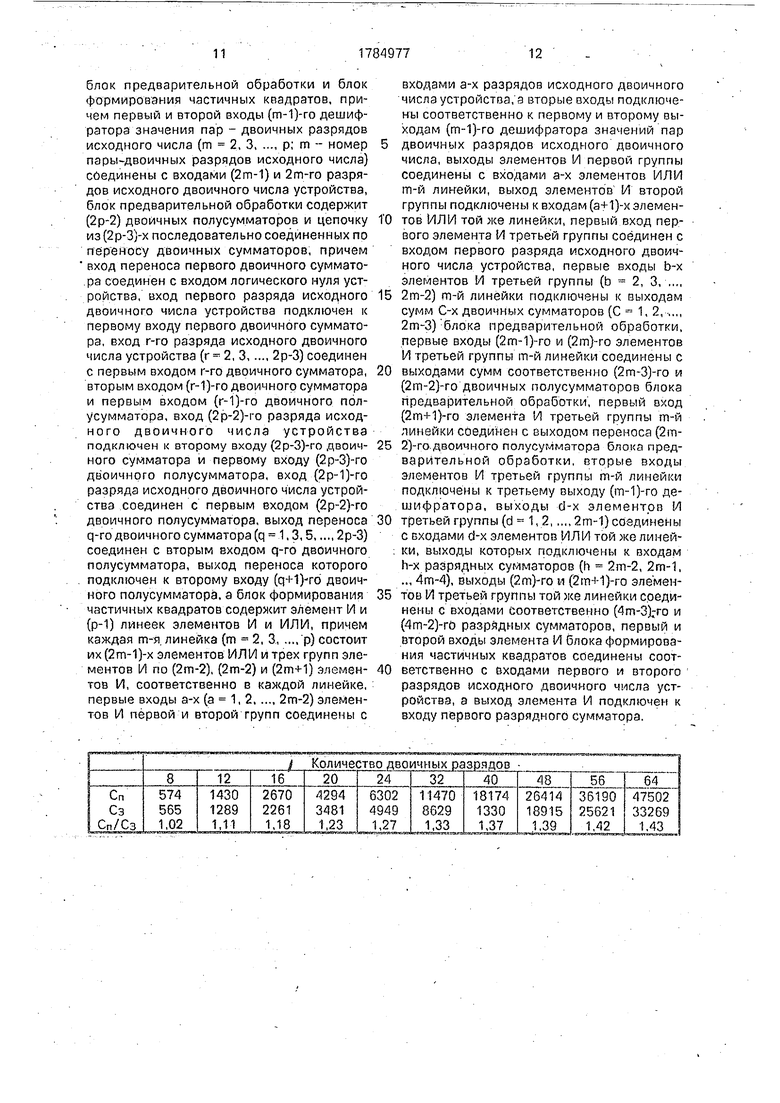

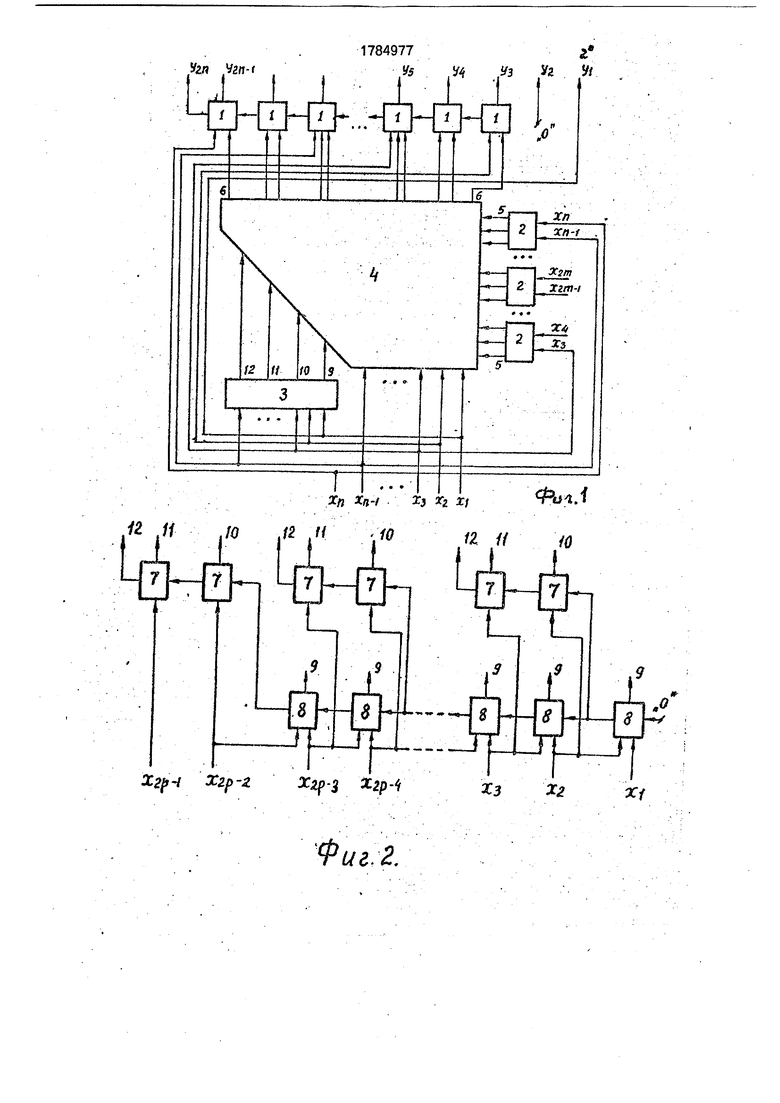

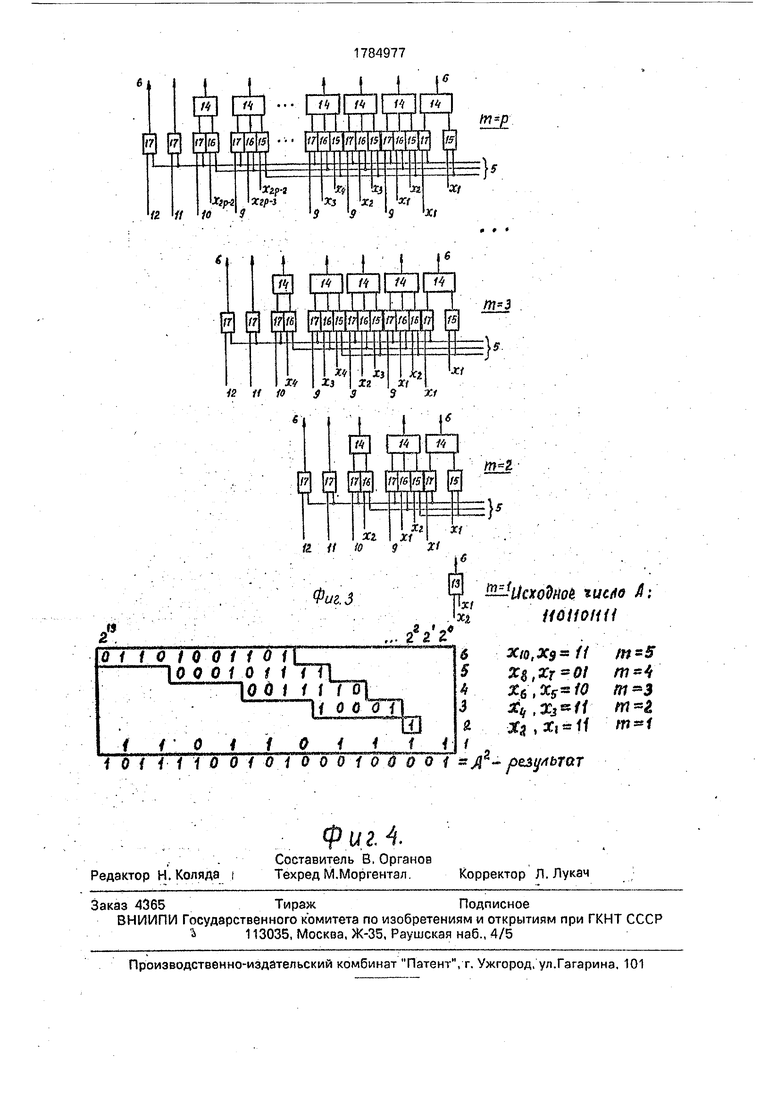

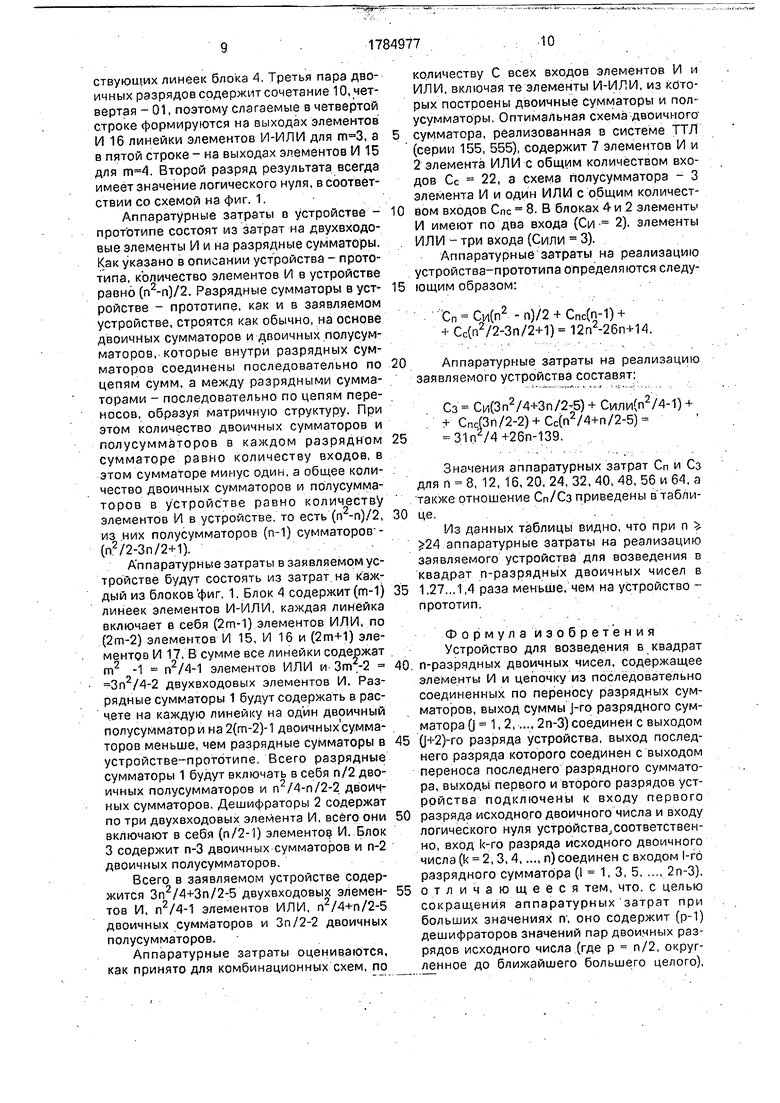

На фиг, 1 представлена структурная схема устройства для возведения в квадрат n-разрядных двоичных чисел; на фиг. 2 - функциональная схема блока предварительной обработки; на фиг. 3 - функциональная схема блока формирования частичных квадратов; на фиг. 4 - пример возведения в квадрат десятичного двоичного числа.

Устройство содержит (фиг. 1) разрядные сумматоры 1, (р-1) дешифраторов 2 значений пер двоичных разрядов исходного числа (р п/2. округленное до ближайшею большего целого), блок 3 предварительной обработ ки, блок 4 формирования частичных квадратов, причем разрядные сумматоры последовательно соединены по цепям переноса, выход суммы j-ro разрядного сумматора 0 1. 22п-3) соединен с выходом

Q-i-2)-ro разряда устройства, выход уап последнего разряда устройства соединен с выходом переноса последнего разрядного сумматора, выход первого yi и у2 второго разрядов устройства подключены ко входу первого разряда xi исходного двоичного числа и входу логического нуля устройства соответственно, вход хк k-ro разряда исходного двоичного числа устройства (k 2, 3,..., п) соединен со входом 1-го разрядного сумматора (I 1, 3, 5, ..., 2п-3), входы (2m-1)-ro и 2m-ro разрядов исходного двоичного числа

устройства (т 2, 3р, т - номер пары

двоичных разрядов исходного числа) подключены соответственно к первому и второму входам (m-l)-ro дешифратора 2, выход которого 5 соединен со входами блока 4, выходы б блока 4 подключены ко входам разрядных сумматоров, входы двоичных разрядов исходного двоичного числа устройства соединены со входами блока 4 и входами блока 3, выходы 9-12 которого соединены со входами блока 4.

Блок предварительной обработки (фиг, 2) содержит 2р-2 двоичных полусумматоров 7 и цепочку из (2р-3)-х последовательно соединенных по переносу двоичных сумматоров 8, вход переноса первого двоичного сумматора соединен со входам логического нуля устройства, вход xi первого разряда исходного двоичного числа устройства подключен к первому входу первого двоичного сумматора, вход Х2 второго разряда исходного двоичного числа устройства соединен с первым входом второго двоичного

сумматора, вторым входом первого двоичного сумматора и первым входом первого двоичного сумматора, вход r-го двоичного разряда исходного двоичного числа устрой5 ста а (г 3, 42р-3) соединен с первым

входом-г-го двоичного сумматора, вторым входом (г-1)-го двоичного сумматора 8 и первым входом (г-1)-го двоичного сумматора 7, вход х2р-2 (2р-2)-го разряда исходного дво0 ичного числа устройства подключен ко второму входу последнего, (2р-3):го, двоичного сумматора 8 и первому входу предпоследнего, (2р-3)-го, двоичного полусумматора 7, вход х2р-1 (2р-1)-го разряда

5 исходного двоичного числа устройства соединен с первым входом последнего, (2р-2)- го, двоичного полусумматора, выход переноса q-ro двоичного сумматора 8 (q 1, 3, 5, ..., 2р-3) соединен со вторым входом

0 q-ro двоичного полусумматора 7, выход переноса которого подключен ко второму вхо- ДУ (с|+1)-го двоичного полусумматора 7, выходы 9 сумматоров 8 и выходы 10, 11, 12 полусумматоров 7 являются выходами бло 5 каЗ.

Блок 4 формирования частичных квадратов (фиг. 3) содержит элемент И 13 и (р-1) линеек элементов И и ИЛИ, причем каждая fn-я линейка (т 2, 3р) состоит из (2т-1)

0 элементов ИЛИ 14 и трех групп элементов И 15, 16 и 17 по (2т-2). (2т-2) и (2т+1) элементов И соответственно, в каждой линейке первые входы а-х (а 1, 22гп-2) элементов И пероой 15 и второй 16 групп соедине5 ны со входами а-х разрядов исходного двоичного числа устройства, а вторые входы элементов И 15 и элементов И 16 подключены соответственно к первому и второму выходам 5 (m-1)-ro дешифратора 2, выходы

0 элементов 1/1 15 первой группы соединены со входами а-х элементов ИЛИ 14 m-й линейки, выходы элементов И 16 второй группы подключены ко вхоДам(эН)-х элементов ИЛИ 14 той же линейки, первый вход перво5 го элемента И третьей группы соединен со входом xi первого разряда исходного двоичного числа устройства, первые входы Ь-х

элементов И 17 третьей группы (Ь 2, 3

2т-2) m-й линейки подключены к выходам 9

0 сумм с-х двоичных сумматоров (с 1, 2, ..., 2т-3) блока 3, первые входы (2т-1)-го и 2т- го элементов И 17 третьей группы m-й линейки соединены с выходами 10 и 11 сумм соответственно, (2m-3}-ro и (2т-2)-го

5 двоичных полусумматоров 7 блока 3, первый вход (2т+1)-го элемента И 17 третьей группы m-й линейки соединен с выходом 12 переноса (2m-2)-ro двоичного полусумматора 7 блока 3, вторые входы элементов И 17 третьей группы m-й линейки подключены к

третьему выходу 5 (m-1)-ro дешифратора 2, выходы d-x элементов И 17 третьей группы

(d 1, 22m-1) соединены со входами d-x

элементов ИЛИ 14 той же линейки, выходы которых подключены ко входам п-х разрядных сумматоров 1 (h 2m-2, 2m-14m-4),

выходы 2m-ro и (2m+1)-ro элементов И 14 третьей группы той же линейки соединены со входами соответственно (4m-3)-ro и (4т- 2)-го разрядных сумматоров 1, первый и второй входы элемента И 13 блока 4 соединены, соответственно, со входами первого xi и второго Х2 разрядов исходного двоичного числа устройства, а выход элемента И 13 подключен ко входу первого разрядного сумматора.

Устройство работает следующим образом. Двоичные разряды исходного числа разбиваются на пары, начиная с первой пары младших разрядов Х2. XL Всего образуется р пар, последняя пара разрядов может быть неполной, она дополняется нулем в старшем разряде. Каждая пара разрядов, кроме первой, поступает на входы своего дешифратора 2. Если m-я пара разрядов (т 2,3р) представляет собой комбинацию 00, то ни на одном из выходов 5 (m-1)-ro дешифратора не будет сформирована логическая единица.

Если m-я пара разрядов представляет собой комбинацию 01, то логическая единица будет сформирована на первом выходе 5 (m-l)-ro дешифратора, подключенном ко вторым входам элементов И 15 m-й линейки элементов И-ИЛИ блока 4. Логическая единица, присутствующая на вторых входах элементов И 15, разрешает передачу двоичных разрядов xt, Х2,..., х2т-2 исходного числа через элементы И 15 и элементы И 14 на выходы 6 блока 4 и далее на входы разрядных сумматоров 1.

Если m-я пара разрядов представляет собой комбинацию 10, то логическая единица появляется на втором выходе 5 дешифра- Торач подключенном ко (вторым входам элементов И 16 m-й линейки элементов 11- 1/1ЛИ блока 4. Логическая единица, присутствующая на вторых входах элементов И 1 б, разрешает передачу двоичных разрядов х1, Х2...., х2т-2 исходного числа через элементы И 16 и элементы ИЛИ 14 на входы разрядных сумматоров 1. При этом двоичные разряды исходного числа, передаваемые через элементы И 16, поступают на входы разрядных сумматоров 1 со сдвигом на один разряд в сторону старших разрядов, по сравнению с двоичными разрядами, передаваемыми через элементы И 15.

При наличии комбинации 11 логическая единица формируется на третьем выходе 5

дешифратора, подключенном ко вторым входам элементов I/I 17, и разрешает передачу двоичных разрядов сформированной в блоке 3 предварительной суммы через элементы И 17 и ИЛИ 14 на входы разрядных сумматоров 1. Блок 3 формирует предварительные суммы двоичных разрядов исходного числа, соответствующие всем р парам разрядов, кроме первой пары, для которой

0 эта сумма не требуется. Предварительная сумма для m-й пары разрядов образуется суммированием части исходного двоичного

числа, содержащей разряды xi, X2Х2т-2 с

этой же часть ю исходного числа, увеличен5 ной на один старший разряд х2т-1 и удвоенной путем сдвига на один разряд в сторону старших разрядов, Разряд Х2т-1 добавляется вследствие того, что каждый последующий частичный квадрат, соответствующий

0 двоичному разряду хмч исходного числа, содержит на один разряд больше, чем предыдущий частичный квадрат, соответствующий разряду х|с.

Для m-й пары двоичных разрядов пред5 верительная сумма содержит 2т+1 двоичных разрядов, из которых три старших разряда образуются на выходах 10, 11, 12 двух двоичных полусумматоров 7, отдельных для каждого значения т. Остальные

0 двоичные разряды предварительной суммы формируются на двоичных сумматорах 8, с выходов 9 которых считываются младшие разряды предварительных сумм, кроме первого разряда. В качестве первого разряда в

5 каждой предварительной сумме используется первый двоичный разряд xi исходного числа.

Структура блока 4 позволяет для каждой т-й пары разрядов уменьшить количество

0 входов в разрядных сумматорах с (2т-2) + (2т-1) 4т-3 до 2т+1 входов, т.е. сократить их на 2(т-2). При увеличении т отношение (2m+1)/(4m-3) приближается к 0,5.

На фиг. 4 приведен пример возведе5 ния в квадрат десятиразрядного числа 1101101111. Результат образуется путем суммирования шести слагаемых. Слагаемое, расположенное в первой строке снизу, состоит из двоичных разрядов исходного

0 числа, непосредственно передаваемых на входы разрядных сумматоров. Слагаемое во еторой строке формируется на выходе элемента И13 блока4(). Слагаемые в третьей - шестой строках соответствуют m « 2, 3,

5 4, 5. Так как вторая м последняя пара двоичных разрядов (т 2, 5) исходного числа содержат по две единицы, то слагаемые в третьей и шестой строках представляют собой суммы, снимаемые с выходов блока 3 и передаваемые через элементы И 17соответствующих линеек блока 4. Третья пара двоичных разрядов содержит сочетание 10, четвертая - 01, поэтому слагаемые в четвертой строке формируются на выходах элементов И 16 линейки элементов И-ИЛИ для , а в пятой строке - на выходах элементов И 15 для . Второй разряд результата всегда имеет значение логического нуля, в соответствии со схемой на фиг. 1.

Аппаратурные затраты в устройстве - прототипе состоят из затрат на двухвходо- вые элементы И и на разрядные сумматоры. Как указано в описании устройства - прототипа, количество элементов И в устройстве равно (п2-п)/2. Разрядные сумматоры в устройстве - прототипе, как и в заявляемом устройстве, строятся как обычно, на основе двоичных сумматоров и двоичных полусумматоров, которые внутри разрядных сумматоров соединены последовательно по цепям сумм, а между разрядными сумматорами - последовательно по цепям переносов, образуя матричную структуру. При этом количество двоичных сумматоров и полусумматоров в каждом разрядном сумматоре равно количеству входов, в этом сумматоре минус один, а общее количество двоичных сумматоров и полусумматоров в устройстве равно количеству элементов И в устройстве, то есть (п2-п)/2, из них полусумматоров (п-1) сумматоров - (п2/2-Зп/2+1).

Аппаратурные затраты в заявляемом устройстве будут состоять из затрат на каждый из блоков фиг. 1. Блок 4 содержит (т-1) линеек элементов И-ИЛИ, каждая линейка включает в себя (2т-1) элементов ИЛИ, по (2т-2) элементов И 15, И 16 и (2т+1) элементов И 17. В сумме все линейки содержат т2 -1 п2/4-1 элементов ИЛИ и Зт -2 Зп2/4-2 двухвходовых элементов И. Разрядные сумматоры 1 будут содержать в расчете на каждую линейку на один двоичный полусумматор и на2{т-2)-1 двоичных сумматоров меньше, чем разрядные сумматоры в устройстве-прототипе. Всего разрядные сумматоры 1 будут включать в себя п/2 двоичных полусумматоров и п /4-П/2-2 двоичных сумматоров. Дешифраторы 2 содержат по три двухвходовых элемента И, всего они включают в себя (п/2-1) элементов И. Блок 3 содержит n-З двоичных сумматоров и п-2 двоичных полусумматоров.

Всего в заявляемом устройстве содержится Зп2/4+Зп/2-5 двухвходовых элементов И, п2/4-1 элементов ИЛИ, п2/4+п/2-5 двоичных сумматоров и Зп/2-2 двоичных полусумматоров.

Аппаратурные затраты оцениваются, как принято для комбинационных схем, по

количеству С всех входов элементов И и ИЛИ, включая те элементы И-ИЛИ, из которых построены двоичные сумматоры и полусумматоры. Оптимальная схема двоичного

сумматора, реализованная в системе ТТЛ (серии 155, 555), содержит 7 элементов И и 2 элемента ИЛИ с общим количеством входов Сс 22, а схема полусумматора - 3 элемента И и один ИЛИ с общим количеством входов Спс 8. В блоках 4 и 2 элементы И имеют по два входа (Си 2). элементы ИЛИ - три входа (Сили 3).

Аппаратурные затраты на реализацию устройства-прототипа определяются следующим образом:

Сп Си(п2 -п)/2 + Спс(п-1) + н Сс(п2/2-Зп/2+1)12п2-26п-И4.

Аппаратурные затраты на реализацию заявляемого устройства составят;

25

Сз Си(Зп2/4+Зп/2-5) + Сили(п2/4-1) + + Спс(Зп/2-2) + Сс(п2/4+п/2-5) -31п2/4+26п-139.

Значения аппаратурных затрат Сп и Сз для п 8, 12, 16, 20, 24, 32, 40, 48, 56 и 64, а также отношение Cn/Сз приведены в таблице.

Из данных таблицы видно, что при n f 24 аппаратурные затраты на реализацию заявляемого устройства для возведения в квадрат n-разрядных двоичных чисел в

1.27...1,4 раза меньше, чем на устройство - прототип.

Формула изобретения Устройство для возведения в квадрат

n-разрчдных двоичных чисел, содержащее элементы И и цепочку из последовательно соединенных по переносу разрядных сумматоров, выход суммы J-ro разрядного сумматора .2,.... 2п-3) соединен с выходом

(+2)-го разряда устройства, выход последнего разряда которого соединен с выходом переноса последнего разрядного сумматора, выходы первого и второго разрядов устройства подключены к входу первого

разряда исходного двоичного числа и входу логического нуля устройства,,соответственно, вход k-го разряда исходного двоичного

числа (k 2,3,4п) соединен с входом 1-го

разрядного сумматора (I 1, 3, 5, .. , 2п-3),

отличающееся тем, что, с целью сокращения аппаратурных затрат при больших значениях п, оно содержит (р-1) дешифраторов значений пар двоичных разрядов исходного числа (где р п/2, округленное до ближайшего большего целого),

блок предварительной обработки и блок формирования частичных квадратов, причем первый и второй входы (m-1)-ro дешифратора значения пар - двоичных разрядов

исходного числа (т 2, 3р; т - номер

пэры-двоичных разрядов исходного числа) соединены с входами (2т-1) и 2т-го разрядов исходного двоичного числа устройства, блок предварительной обработки содержит (2р-2) двоичных полусумматоров и цепочку из (2р-3)-х последовательно соединенных по переносу двоичных сумматоров, причем вход переноса первого двоичного сумматора соединен с входом логического нуля устройства, вход первого разряда исходного двоичного числа устройства подключен к первому входу первого двоичного сумматора, вход r-го разряда исходного двоичного

числа устройства (г - 2, 32р-3) соединен

с первым входом r-го двоичного сумматора, вторым сходом (М)-го двоичного сумматора и первым входом (М)-го двоичного полусумматора, вход (2р-2)-го разряда исходного двоичного числа устройства подключен к второму входу (2р-3)-го двоичного сумматора и первому входу (2р-3)-го двоичного полусумматора, вход (2р-1)-го разряда исходного двоичного числа устройства соединен с первым входом (2р-2)го двоичного полусумматора, выход переноса

q-ro двоичного сумматора (q 1,3,52р-3)

соединен с вторым входом q-ro двоичного полусумматора, выход переноса которого подключен к второму входу (q-M) ro двоичного полусумматора, а блок формирования частичных квадратов содержит элемент И и (р-1) линеек элементов И и ИЛИ, причем

каждая m-я линейка (т 2, 3р) состоит

их (2т-1)-х элементов ИЛ И и трех групп элементов И по (2m-2), (2m-2) и (2т+1) элементов И, соответственно в каждой линейке, первые входы а-х (а 1, 22т-2) элементов И первой и второй групп соединены с

входами а-х разрядов исходного двоичного числа устройства, з вторые входы подключены соответственно к первому и второму выходам (m-1)-ro дешифратора значений пар

двоичных разрядов исходного двоичного числа, выходы элементов И первой группы соединены с входами а-х элементов ИЛИ m-й линейки, выход элементов И второй группы подключены к входам (а+1)-х элементов ИЛИ той же линейки, первый вход первого элемента И третьей группы соединен с входом первого разряда исходного двоичного числа устройства, первые входы Ь-х элементов И третьей группы (Ь 2, 3, ....

2т-2) т-й линейки подключены к выходам

сумм С-х двоичных сумматоров (С 1, 2

2пл-3) блока предварительной обработки, первые входы (2m-1)-ro и (2m)-ro элементов И третьей группы m-й линейки соединены с

выходами сумм соответственно (2т-3)-го и (2т-2)-го двоичных полусумматоров блока предварительной обработки, первый вход (2т+1)-го элемента И третьей группы m-й линейки соединен с выходом переноса (2т2)-го двоичного полусумматора блока предварительной обработки, вторые входы элементов И третьей группы m-й линейки подключены к третьему выходу (nrH)-ro дешифратора, выходы ci-x элементов И

третьей группы (d 1,2, ...,2m-1) соединены с входами d-x элементов ИЛИ той же линейки, выходы которых подключены к входам h-x разрядных сумматоров (h 2m-2, 2m-1, .., 4m-4), выходы (2m)-ro и (2m+1)-ro эле ментов И третьей группы той же линейки соединены с входами соответственно (4m-3);ro и (4т-2)-го разрядных сумматоров, первый и второй входы элемента И блока формирования частичных квадратов соединены соответственно с входами первого и второго разрядов исходного двоичного числа устройства, а выход элемента И подключен к входу первого разрядного сумматора.

%я teiM

1784977 4s

Ц УЗ У2

Z

У/

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Устройство для возведения п-разрядных чисел в квадрат | 1979 |

|

SU911520A1 |

| Устройство для параллельного алгебраического сложения в знакоразрядной системе счисления | 1981 |

|

SU1003074A1 |

| Устройство для умножения элементов конечного поля GF(2 @ ) при м @ 3 | 1990 |

|

SU1728858A1 |

| Цифровая система программного управления | 1987 |

|

SU1411710A1 |

| Генератор псевдослучайных последовательностей | 1984 |

|

SU1228236A1 |

| Устройство для умножения | 1982 |

|

SU1123031A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU907548A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ОПЕРАЦИЙ С КОМПЛЕКСНЫМИ ЧИСЛАМИ | 1973 |

|

SU377769A1 |

| Дешифратор | 1980 |

|

SU890386A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах оперативной обработки информации. Целью изобретения является сокращение аппаратурных затрат на реализацию устройства для возведения в квадрат при больших значениях п, где п - разрядность исходных чисел. Цель изобретения достигается за счет сокращения количества сумматоров, необходимых для суммирования частичных произведений. Для достижения цели устройство содержит дешифраторы значений пар двоичных разрядов исходного числа, блок промежуточной обработки и блок формирования частичных квадратов. Двоичные разряды исходного числа разделяются на пары, при сочетании двоичных разрядов в паре 01 или 10 на суммирование передается частичное произведение, соответствующее двоичному разряду, равному 1 в этой паре разрядов, при сочетании 11 на суммирование передается сумма этих частичных произведений, предварительно образованная в блоке формирования утроенных значений частей исходного числа.4 ил. сл С

ЗГ/J Xrt-/ X) Г2 Xf

к ,// jo

ML

/2 f/ -10

I i vII

I-wLm. Л

43

a:2p- ar5

Фиг. 2.

/a # to

ЧЗп т

8 -E

Jn Vr

Jl 7b

т

a:/

m irm ir

1784977

«p пп шшшр гт ш. тпщптгт аз.

МйЫ/гщиvwjwm m

ШШтжпУir

и

/в

р-г

аггр-г

JT

Х3

/г /о

и // Ж

Фиг.3

г

001101 001Q 1 11

UMJJ f iTo

IL11JJ. о. i 10 il

to

и jfa.afieff «ла.

iO/fffOO/o ooofo Ј o/ ялл-Ј езультат

J9

л

гг

агг

JC/

л;/

XI

ш гиы А:

Х

HOHOHH

& xn,X9 f1m-5

§ %$,xr-oim«4

4 %6lxs toт-э

3 Л,ЭС} //W«

и jfa.afieffw f «ла.

/ ялл-Ј езультат

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Матричное устройство для возведенияВ КВАдРАТ | 1979 |

|

SU842804A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для возведения в квадрат п-разрядных двоичных чисел | 1978 |

|

SU699521A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-30—Публикация

1990-01-10—Подача