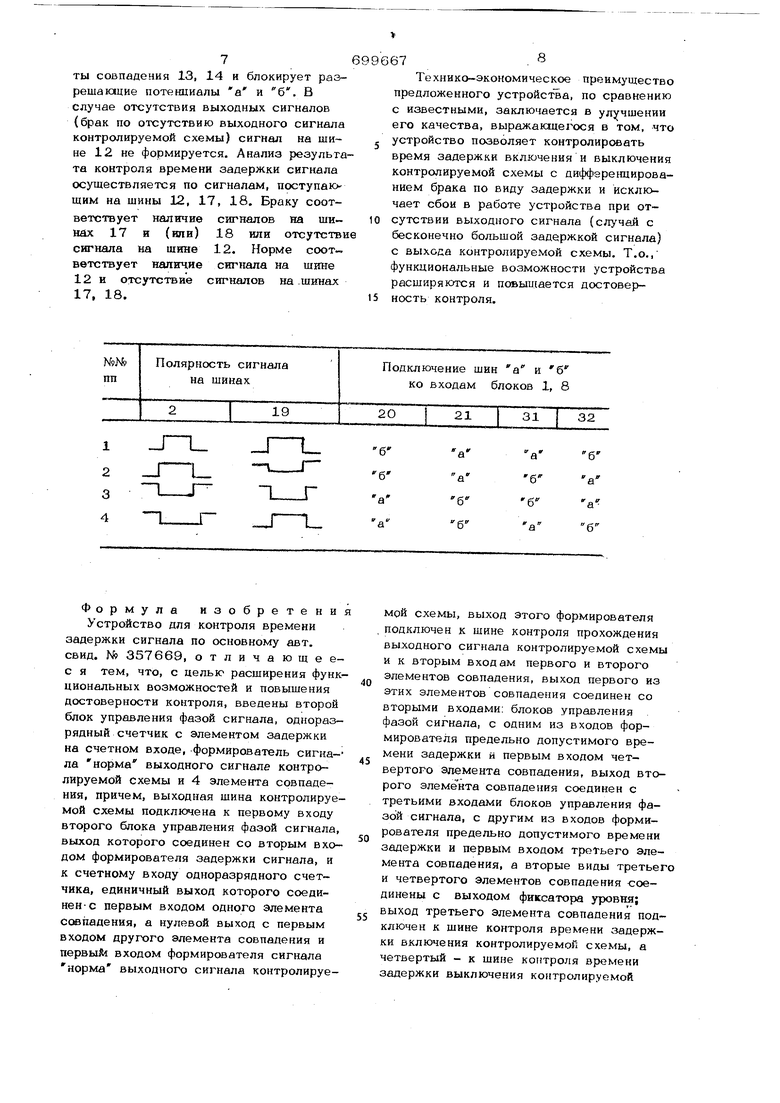

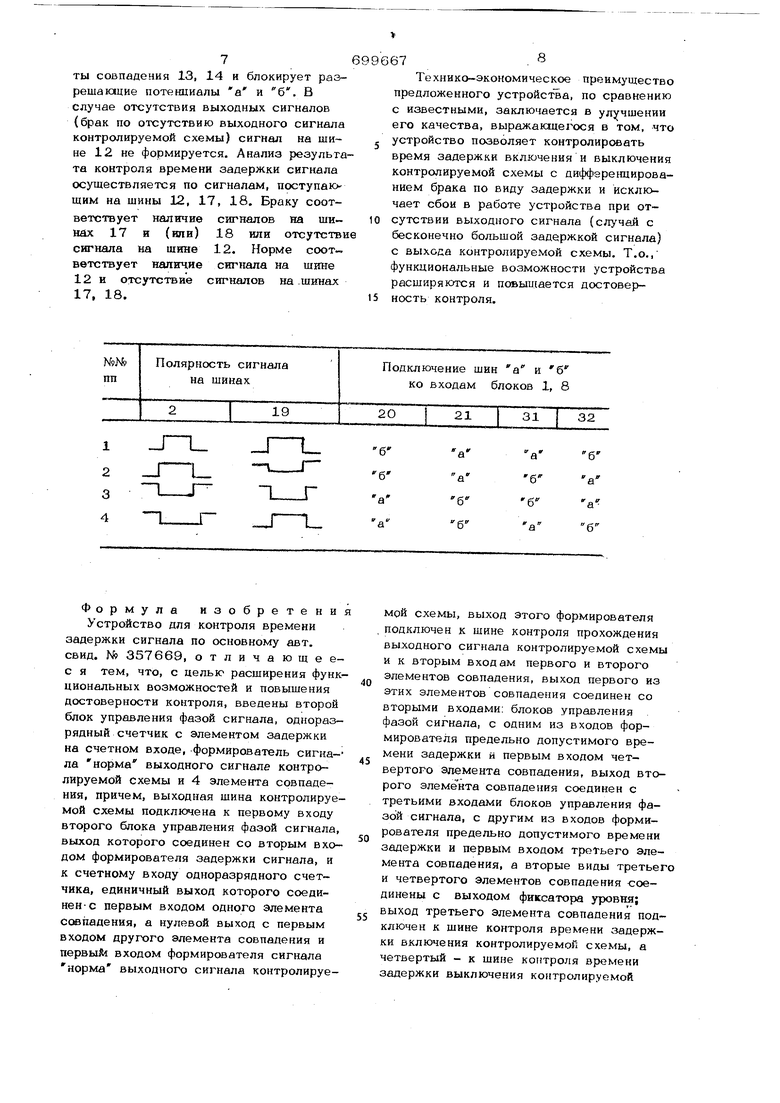

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ВРЕМЕНИ ЗАДЕРЖКИ СИГНАЛА сатора уровня, введены второй блок управления фазой сигнала, одноразрядный счетчик с Элементом задержки на счет ном входе, формирователь сигнала норма выходного сигнала контролируемой схемы и четыре элемента совпадения, причем выходная шина контролируемой схемы подключена к первому входу второго блока управления фазой сигнала, выход которого соединен со вторым входом формирователя задержки сигнала и к счетному входу одноразрядного счет чика, единичный выход которого соедине с первым входом первого элемента совп дения, а нулевой выход - с первым входом второго элемента совпадения и первым входом формирователя сигнала норма выходного сигнала контролируемой схемы, выход этого формиров теля подключен к шине контроля прохождения выходного сигнала контролируемой схемы и ко вторым входам первого и второго элементов совпадения, выход первого из этих элементов совпадения соединен со вторыми входами блоков управления фазой сигнала, с одним из входов формирователя предельно допустимого времени задержки и первым входом четвертого элемента совпадения, выход второго элемента совпадения - с третьими входами блоков управления фазой сигнала, с другим из входов формиров ате л ia предельного допустимого времени задержки и первым входом третьего элемента сбвпадення, вторые вход третьего и четвертого элементов совпадения соединены с выходом фиксатора уровня, выход третьего элемента совпадения подключен к шине контроля времени задержки включения контролируемо схемы, а четвертого - к шине контроля времени задержки выключения контролируемой схемы, шина исходное соедине на со входом установки в О одноразрядного счетчика и вторым входом формирователя сигнала норма выходного сигнала контролируемой схемы. Такая схема устройства позволяет расширить функциональные возможности устройства за счет одновременного (в одном цикле измерения) контроля задержек ВЫКЛ дифференцирования вида брака повысить достоверность контроля, исклю ложный результат контроля, фиксируемьШ устройством в случае отсутствия выходного сигнала контролируемой схемы. На-фиг. 1 представлена функциональная схема устройства; на фиг. 2 врем ные диаграммы, пояснякхние работу устройства. Устройство содержит первый блок 1 управления фазой сигнала, Входную шину 2 контролируемой схемы, фор миров ате ль 3 задержанного сигнала , н 1тегрирукхций конденсатор 4, формирователь 5 предельно допустимого времени задержки, входы 6 управления формирователя предельно допустимого времени задержки, фиксатор уровня 7, второй блок 8 уп- равле:1Ия фазой сигнала, одноразрядный счетчик 9 с элементом задержки на счетном входе, шину исходное 10, формирователь 11 сигнала норма выходного сигнала контролируемой схемы, шину 12 контроля прохождения выходного сигнала контролируемой схемы, элементы совпадения 134-16, шину 17 контроля времени задержки включения контролируемой схемы, шину 18 контроля времени задержки выключения контролируемой схемы, выходную шину 19 контролируемой схемы, входы 2О4-32, элемент И-НЕ 33, транзистор 34, транзисторные клю.чи 35, резисторы 36, триггер 37, элемент И-НЕ 38. Устройство работает следующим образом. С входа и выхода контролируемой схемы соответственно на шины 2 и 19 устройства поступают входные сигналы. Если при этом подаются сигналы разрешения на вход блока 1 управления фазой сигнала и вход 32 блока 8 управления фазой сигнала, то на выходные шины этих блоков поступают сигналы, совпадающие по фазе с входными. Если подаются сигналы разрешения на вход 2О блока 1 и вход 31 блока 8, то на входы 22 и 23 поступают сигналы, инверсные входным. Сигналы разрешения на входы 20, 21, 31, 32 подаются таким образом, что на входы 22 и 23 сигналы поступают всегда в противофазе. Сигнал на входе 23 отстает по времени от сигнала на входе 22 на время задержки сигнала контролируемой схемы. Задержки сигналов в блоке 1 управления фазой входного сигнала и в блоке 8 управления фазой выходного сигнала постоянны во всем диапазоне задержек и учитьшаются при калибровке устройства. При поступлении на входы 22 и 23 сигналов на выходе элементов 33 образуется отрицательный импульс, длительность которого равна длительности задержки сигнала контролируемой схемы. Причем, если элемент 33 являетс.1 элементом И-НЕ для .положительной логики, то при поступлении на вход 22 сигнала положительной полярности (высокий уровень) а на вход 23 - отрицательный полярности (низкий уровень), длительность отрицательного импульса на выходе элемента 33, соответствует задержке на включение контролируемой схемы фиг.2). При поступлении на входы 22, 23 противоположных по поЛ5фности сигналов длительность отрицательного импульса на выходе элемента. 33 соответствует задержке на выключение контролируемой схемы Транзистор 34 запирается на время длительности этого импульса, что обуславливает заряд интегрирующего конденсатора 4 через форми рователь 5 предельно допустимого времени задержки. На один из входов 6 фор мирователя 5 предельно допустимого вре мени задержки поступает сигнал, вводящ один из транзисторных ключей 35 в насыщение. Этим обеспеч1шается подключение источника питания к соответствующему резистору 36, которому соответствует своя, предельно допустимая для данной контролируемой схемы, задержка. Напряжение на интегрирующем конденсаторе 4 в каждый момент времени пропорционально длительности импульса на выходе формирователя 3 задержки сигнала контролируемой схемы и зависит от постоянной времени, которая определяется выбором одного из резисторов 36. Если длительность задержки контролируе мой схемы не превыщает предельно допустимого времени задержки, заданной путем выбора резисторов 36, то напрйжение на интегрируюцем конденсаторе 4 не достигает порога срабатывания фиксатора уровня 7. Если же задержка контролируемой схемы превысит предельно допустимое время задержки, то напряжение на интегрирующем конденсаторе 4.превысит порог срабатывания фиксатора уровня 7, который выдает сигнал ощибки. При контроле ощибки (брака) по контролируемой схемы разрешение подается на вход 30 элемента совпадения 15 и сигнал ошиб ки по5Шляется на шине 17. При контроле ощибки (брака) по С .ц д контролируемся схемы разрещение подается на вход 29 элемента совпадения 16 и сигнал ощибк появляется на щине 18, Формирование разрешающих сигналов а и б, посту676 пающих на входы 6, 20, 21, 29, 30, 31, 32 осуществляется с помощью одноразрядного счетчика 9. Подключение соответствующих входов 6 к шинам а и б выполняется в зависимости от предельно допустимой для данной контролируемой схемы задержки. Подключение входов 2О, 21, 31, 32 к входам а и б в зависимости от полярности сигналов на входных щинах 2 и 19 представлено в таблице 1. При соблюдении указанного подключения измеряется вначале Т .g| , а Временная диаграмма затем Т работы устройства привед:ена на фиг. 2 ДЛЯ случая: сигнал на щине 2 положительной полярности, сигнал на щине 19отрицательной полярности, что соответствует поз. 2 таблицы. По сигналу исход- ное, поступающему на щину 1О, однораэРЯДНЫЙ счетчик 9 и формирователь 11 сигнала норма устанавливаются в исходное состояние. В этом случае разрещающий потенциал появляется на входе а элемента совпадения 14, вход б при этом Заблокирован отрицательным потенциалом. При поступлении первого сигнала на щины 1 и 19 устройство осуществляет контроль Tgi.KOKTpoanpyeмой схемы и в случае брака выдает сигнал ощибки по -щине 17. По заднему фронту первого выходного сигнала, поступающего на щину 19, одноразрядный счетчик 9 переключается, фазы сигналов на его выходах (входы 27, 28) изменяются на противоположные и разрещающий потенциал появляется на вход б элемента совпадения 13; вход а при этом заблокирован отрицательным потенциалом. При поступлении второго сигнала на щины 1 и 19 устройство осуществляет контроль контролируемой схемы и, в случае брака, выдает сигнал ощибки по щине 18. Отрицательный сигнал, образованный на вхо де 28 после прохождения первого импульса, подается на единичный вход триггера 37 и переключает его; таким образом, на первом входе элемента 38 И-НЕ образуется положительный сигнал. После окончания вторрго выходного сигнала на щине 19 одноразрядный счетчик 9 переключается, на .входе 28 образуется положительный сигнал, что приводит к появлению отрицательного выходного сигнала на щине 12 означающего норму выходного сигнала контролируемой схемы. Образовавщийся на входе 28 отрицательный сигнап поступает, кроме того, на элементы совпадения 13, 14 и блокирует разрешающие потенциалы а и б, В случае отсутствия выходных сигналов (брак по отсутствию выходного сигнала контролируемой схемы) сигнал на шине 12 не формируется. Анализ результата контроля времени задержки сигнала осуществляется по сигналам, поступающим на шины 12, 17, 18. Браку соответствует наличие сигналов на шинах 17 и (или) 18 или отсутств сигнала на шине 12. Норме соответствует наличие сигнала на шине 12 и отсутствие сигналов на-ШИнах 17, 18.

Технико-экономическое преимущество предложенного устройства, по сравнению с известными, заключается в улучшении его качества, выражающегося в том, что устройство позволяет контролировать время задержки включения и выключения контролируемой схемы с диффэреш1ированием брака по виду задержки и исключает сбои в работе устройства при отсутствии выходного сигнала (случай с бесконечно большой задержкой сигнала) с выхода контролируемой схемы. Т.о., функциональные возможности устройства расширяются и повышается достоверность контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля времени задержки включения и выключения схемы | 1978 |

|

SU790229A2 |

| Устройство для контроля времени задержки включения и выключения контролируемой схемы | 1977 |

|

SU720712A1 |

| УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1990 |

|

RU2024906C1 |

| Выходное устройство тестера | 1988 |

|

SU1597794A1 |

| Устройство фазовой синхронизации | 1975 |

|

SU536593A1 |

| Устройство для контроля электрических параметров трансформаторов | 1982 |

|

SU1122984A1 |

| Устройство дл прогнозирования неисправностей радиоэлектронной аппаратуры | 1978 |

|

SU742958A1 |

| Программно-временное устройство | 1978 |

|

SU805257A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

Формула изобретени Устройство для контроля времени задержки сигнала по основному авт. свид. № 357669, отличающеес я тем, что, с целью расширения функциональных возможностей и повышения достоверности контроля, введены второй блок управления фазой сигнала, одноразрядный счетчик с элементом задержки на счетном входе, формирователь сигнала норма выходного сигнале контролируемой схемы и 4 элемента совпадения, причем, выходная шина контролируемой схемы подключена к первому входу второго блока управления фазой сигнала, выход которого соединен со вторым входом формирователя задержки сигнала, и к счетному входу одноразрядного счетчика, единичный выход которого соединен-с первым входом одного элемента совпадения, а нулевой выход с первым входом другого элемента совпадения и первым входом формирователя сигнала норма выходного сигнала контролируемой схемы, выход этого формирователя подключен к шине контроля прохождения выходного сигнала контролируемой схемы и к вторым входам первого и второго элементов совпадения, выход первого из этих элементов совпадения соединен со вторыми входами: блоков управления фазой сигнала, с одним из входов формирователя предельно допустимого времени задержки и первым входом четвертого элемента совпадения, выход второго элемента совпадения соединен с третьими входами блоков управления фазой сигнала, с другим из входов формирователя предельно допустимого времени задержки и первым входом третьего элемента совпадения, а вторые виды третье и четвертого элементов совпадения соединены с выходом фиксатора уровня; выход третьего элемента совпадения подключен к шине контроля времени задержки включения контролируемой схемы, а четвертый - к шине контроля времени задержки выключения контролируемой

схемы, шине исходное соединена со входом установки одноразр5шного счетчрка и входом формирователя сигнале норма выходного сигнала контролируемой схемы.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-11-25—Публикация

1977-10-05—Подача