фазой йходнотч) и вЫхбдйого снгнапов контролируемой схемы и фьрййрбватель . ггределБНО допустимого времени задержки, введены формирователь импульсов и блок йнали;за временного положения сигналов, первый вход которого соединен с выходом блока управления фазой выходного сигнала контролируемой схемы и первым входом формирователя импульсов, второй вход - с первым выходом формировате- io ля предельно допустимого времени задержки, второй выход которого подключен ко второму входу формирователя импульсов, третий йхУд - с пёрвбШ выходом формирователя импульсов, четвер- is тый вход - с вторым выходом формирователя импульсов, а пятый вход подключен к выходу блока управления фазой входного сигнала контролируемой схемы.

Причем блок анализа временного по- 20 ложения сигналов содеряшт формирователь сигнала исходное и два блока бпредёлёния очередности поступления сигналов, каждь1й из которых ветючает три т|эиггера, 1выход О первого тригге- 25 ра подключён к входу 1 второго триггера, выход О которого соединен с входом 1 nepBOfxi триггера, а выход 1 - с шиной норма времени задержки- включения контролируемой схемы, вы- 30 ход 1 первого триггера подключен к входу 1 третьего триггера, а выход О которого соединен с входом О первого триггера, а выход - с шиной брак

йрёйёни задёржкй включейия кбнтрблируе- 35

мой схемы; вход О первого триггера первого б вёЙШ|зёЙ®ТёНйа очередности поступления сигналов подключён к аёрвому входу бпб1ка анализа временного положения сигналов, второй40 вход 1 первого триггера первого бло ка оп ёдёления бчё(эёдйбстй поступленй сигналов подключен к второму входу блока аналимвременного положения сигналов, второй вход О первого триггера 45 второго блока определения очередности поступления сигналов подключён к третьему входу блока анализа временного положения сигналов, а второй вход первого триггера второго блока опреде- SO пений очередности поступления сигналов подключен к четвертому входу блока , flHiOJTOsa временроГ б положётшя сйг нйлов; выход второго триггера второго блока 6прёдр1пёнйяочёрелндс ти пВступле 55 ния сигналов соединен с Ш11ной. норма времени эпдоржТси&ыключеш1Я коитроли- руемой в1.1хоп 1 третьего триггера второго блока определения очередности поступления сигналов соединен с шиной брак времени задержки выключения контролируемой схемы; вход формирователя | сигнала исходное Подключен к пятому входу блока анализа временного положения сигналов, а его выход - к входам О второго и третьего триггеров о|боих блоков определения очерёдности поступления сигналов.

Такая схема устройства позволяет расширить функциональные возможности устройства за счет контроля времени задержки не перерывающихся во времени входного и выходного сигналов контролируемой схемы (при малых длительностях и ббльших задержках сигналов) и обеспечений контроля времени задержки при наличии входного и отсутствии выходного сигнала, соответствует бесконечно большому времени задержки сигнала; повысить точйость контроля, так как отсутствует преобразование длительности сигнала (задержки) в амплитуду, которое вносит дополнительную погрешность,

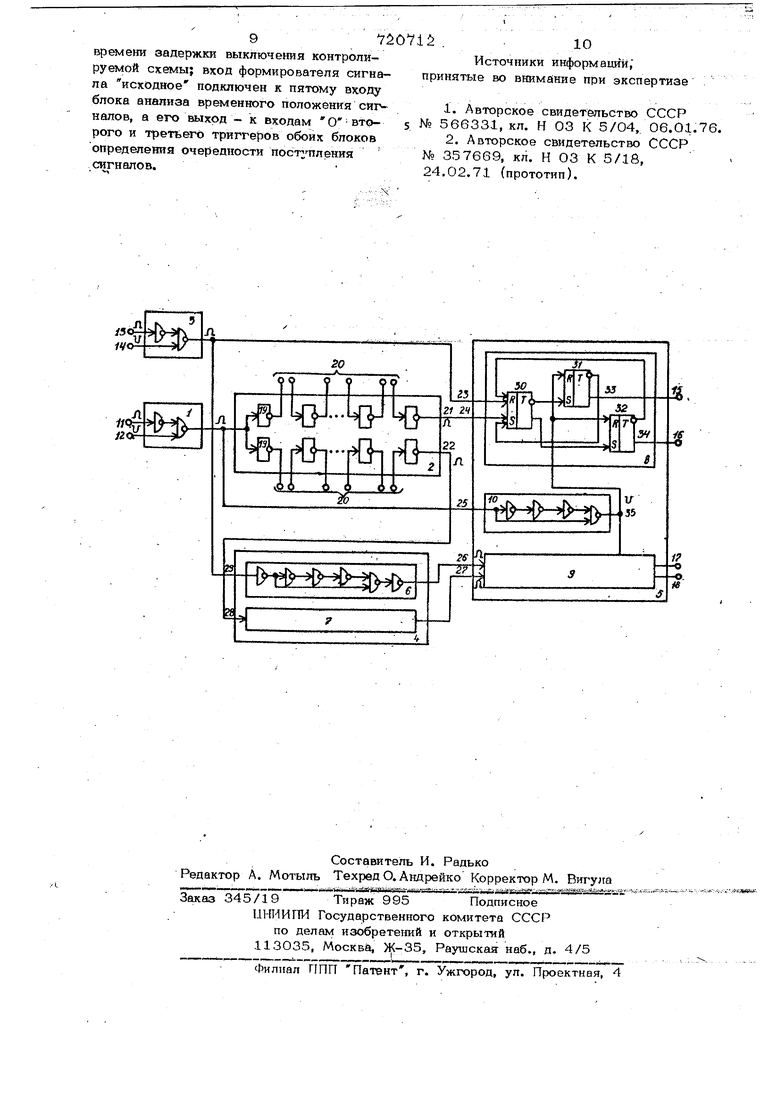

Ка чертеже представлена блок-схема устройства для контроля времени задержки включения к выключения контролируемой схемы.

Блок-схема устройства содержит блок 1 управления фазой входного сигнал контролируемой схемы; формирователь 2 предельно допустимого времени задержки; блок 3 управления фазой выходного сигнала контролируемой формирователь 4 импульсов; блок 5 анализа временного положения сигналов; первый блок 6 формирования импульса по заднему фронт у сигнала; второй блок 7 формирования импульса по заднему фрбпту . сигнала; первый блок 8 определения очередности поступления сигналов; второй блок 9 определения очередности поступления сигналов; формирователь 10 сигнала исходное ; вход 11 блока управления фазой для положительного (высокий уровень) входного сигнала контролируемой схемы; вход 1 2 блока управления фазой для отрицательного (низкий уровень) вводного сигнала контролируемой схемы; вход 13 блока управления фазой для-положительного выходного сиг I., А

нала контролируемой схемы; вход 14 блока управления фазой для отрицательного выходного сигнала контролируемой схемы; шина 15 норма времени задержки включения контролируемой схемы; шина 16 брак времени задержки включетш контролируемой схемы; шина 17 норма времени задержки выключения контролируемой схемы; шина 18 брак времени задержки выключения контролируемой схемы; элемент 19 задержки; установочные входы 20 формирователя предельно допустимого времени задержки; выход 21 1-ого формирователя предельно допустимого времени задержки; выход 22 2-ого формирователя предепьно допустимого времени задержки; первый вход 23 блока анализа временного положения сигналов; второй вход 24 бло ка анализа временного положения сигналов; пятый вход 25 блока анализа време кого положения сигналов; третий вход 26 блока анализа временного положения сигналов четвертый вход 27 блока анализа временного положения сигналов; вто рой вход 28 формирователя импульсов; первый .вход 29 формирователя импульсов; первый триггер 30; второй триггер третий триггер 32; выход 33 1 второ го триггера; выход 34 1 третьего три гера; выход 35формирователя сигнала исходное. Устройство может быть выполнено на потенциальных интегральных микросхемах Формирователь предельно допустимого времени задержки строится, например,с помощью последовательно соединенных интегральных инверторов или регулируемы задержек. С входа и выхода контролируемой схе мы соответственно на входные шинь 11 (12) и 13 (14) блоков управления фазо входного и выходного сигналов 1, 3 пос тупают контролируемые сигналы. С входа контролируемой схемы на шину 11 сигна лы подаются в случае положительного входного сигнала и на шину 12 - в случае отрицательного входного сигнала. Аналогично подаются сигналы с вькрда контролируемой схемы на шины 13 и 14 Таким образом при любой полярности входного и выходного сигнала контролируемой схемы на выходах блоков 1 и 3 формируются положительные сигналы. Сигнал на выходе блока 1 отстает по времени от сигнала на выходе блока 3. При поступлении сигнала на вход формирователя предельно дойустимого времени задержки 2 на выходе 21 (22) появляется положительный сигнал, задержанный на величину, допустимую для данной контролируемой схемы. Время задержки включения и выключения набирается на элементах задержки 19 с помощью установочных входов 20. , Сигнал с блока 3 поступает на вход 23 блока анализа временного положе1шя сигналов 5 и на вход 29 форг грователя импульсов 4. Сигналы с выходов 21, 22 формирователя 2 поступают соответственно на вход 24 блока анализа временного положения сигналов и на вход 28 формирователя импульсов. Анализ задержки включения контролируемой схемы производится первым блоком определения очередности блока 5. На В.ХОД 23 сигнал поступит раньше, чем на вход 24, и на выходе 15 блока анализа временного положения сигналов появится положительный сигнал норма, если длительность задержки включения контролируемой схемы не превышает предельно допустимого значения времени задержки включения. На вход 24 сигнал поступит раньше, чем на вход 23, и на выходе 16 блока5 появится положительный сигнал брак, если длительность задержки включения контролируемой схемы превысит допустимое значение времени задержки включения. Для анализа задержки выключения сигналы, поступающие на входы 28, 29 формирователя импульсов 4, дифференцируются по заднему фронту, а затем поступают на входы 26, 27 блока 5 на второй блок определения очередности сигналов 9.. На вход 26 сигнал поступит раньше, чем на вход 2 7-и на выходе 17 блока 5 появится положительный сигнал норма, если длительность задержки выключения контролируемой схемы не превышает предельно допустимого значения времени задержки выключения. На вход 27 сигнал поступит раньше, чем на вход 26, и на выходе 18 блока 5 появится положительный сигнал брак, если длительность задержки выключения контролируемой схемы превысит предельно допустимое значение времени задержки выключеггая. Оба блока определения очередности . поступления сигналов построены аналогично. В исходном состоянии триггеры 31, 32 находятся в состоянии О и на выходах 33„ 34 - отрицательный сигнал (низкий потенци ал). До прихода сигналов на входах 23 и 24 присутствует низкий уровень, в pfiультате чего на обоих выходах триггеpa 30 ймеетса йолржйтёпьный сигнал (вьюркий потенциал). При появлеши . пШожительнргб сигнала вначале на входе 23 срабатывает триггер ЗО и на его выходе О появляется отрицательный сигнал, который устанавливает триггер „ 31 в положение 1. На шине 15 появляется сигнал норма. Отрицательный потенциал с выхода О триггера 31 подтверждает состояние триггера 30. При поступлении затем сигнала на вход 24 блок 8 не реагирует до -прихода следующёГЧ) сигнад а с формирователя 2. По сигналу приходящему на вход 25, на выходе 35 блока 1О по переднему фронту появляется отрицательный сигнал устанавливающий блоки 8, 9 в исходное состояние. При наличии ВХОДНОГО) и отсутствии вщоднргр сигнала блок 5 форШруёт на шинах 16, 18 соответственно сигналы брак включения и брак №1кВю ения контрюлируемой схемы., Задержка, возникатбщая в блрках 1, 3 4 прстоянная во всем диапазоне задержек и учитывается при калибровке уст ройства. Технико-экономическое преимущество преТзлбжёНВОгЬ устройства по сравнению сизвестным заключается в улучшении ёГР качества, выражающееся в том, что рас11гаряются фуНкЦйбнШьйьге febsMOHtHocти устройствй за счёт контроля времени задержки не пёрек|)ываю1цйхся во времени iaxoflHoro и выходного сигналов контро лируемой схемы (при малых хшйтельнос; тях и больших задержках сигналов) и обеепёгенйй крнтреш ШМёркжи при наличии входндгЬ и отсутствии выходного сигналов (случай с бесконечно большой задержкой сигнала); повышаетс точность крнтроля, так как отЬутствует (задержки) в амплитуду сигй,а, которое внрсит дополнител ьнутю погрешность. Формула изоб р е тё н и я 1. Устройство для контроля времени задержки включения и вьтключения контролируемой схемы, содержащее блоки уп равления фазой входного и выходного сигналов контролируемой схемы и форми рователь предельно допустимого времени задержки, от л и ч а ю щ я те что, с целью расшпрения функциональных вЬаможностей и nea;nueiTffflтЬ ё Ьтй кРн 12в роля введены формирователь импульсов и блрк анализа временного положения сигналов, первый вход которого соединен с выходом блока управления фазой выходного сигнала контролируемой схемы и первым входом формирователя импульсов, второй вход - с первым выходом формирователя предельно допустимого времени задержки, второй выход котррого подключеН ко второму входу формирователя импульсов, третий вход - с первым выходом формирователя импульсов, четвертый вход - с вторым выходом формиррвателя импульсов, а пятый вход подкл1рчен к выходу блока управления фазой входного сигнала контролируемой схемы. 2, Устройство по п. 1, о т л и чающееся тем, что блрк анализа временнрго положения сигналов содержит формирователь сигнала исходное и два бДрка определения очередности поступления сигналрв, каждый из которых . включает три триггера, причем выход О первого триггера подключен к входу 1 второго триггера, выход О которого соединен с входом 1 первого триггера, а выход - с. шиной норма временизадержки включения контролируемой схемы, выход первого триггера подкл рчен к входу 1 третьего триггера, выход О которого соединен с входом О первого триггера, а выход 1 - с шиной брак времени задержки включения контролируемой схемы; второй вход О первЬго триггера первого блока определения очередности поступления сигналов подключен к первому входу блока анали завременного положения сигналов, второй вход первого триггера первого блока определения очередности поступления сигналов подключен к второму входу блока анализа временнрго положения сигналов, второй вход О первого триггера второго блока определения очередности поступления сигналов подключен к третьему входу блока анализа временного положения сигналов, а второй вход первого триггера второгр блока определения очередности поступления сигналов подключен к четвертому входу блока анализа временного положения сигналов; выход второго триггера второго блока определения очередности поступления сигналов соединен, с шиной норма времени задержки выключения контролируемой схемы, выход третьего триггера второго блока определения очерпдности поступления сигналов соединен с шиной брак

времени задержки выключения контролируемой схемы; вход формирователя сигнала исходное подключен к пятому входу блока анализа временного положения сигналов, а его выход - к входам О второго и третьего триггеров обоих блоков определения очередности nocT i-пления сигналов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 566331, кл. Н 03 К 5/04,. 06.01,76.

2.Авторское свидетельство СССР № 357669, кл. Н ОЗ К 5/18, 24,02.71 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля времени задержки включения и выключения схемы | 1978 |

|

SU790229A2 |

| Устройство для контроля времени задержки сигнала | 1977 |

|

SU699667A2 |

| УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1990 |

|

RU2024906C1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1667073A1 |

| СПОСОБ ВЫКЛЮЧЕНИЯ ЖИДКОСТНЫХ РАКЕТНЫХ ДВИГАТЕЛЕЙ СОСТАВНОЙ РАКЕТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2079690C1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для распознавания критических состояний объекта контроля | 1983 |

|

SU1090683A1 |

| Устройство для контроля счетчиков импульсов | 1985 |

|

SU1248061A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

)

Авторы

Даты

1980-03-05—Публикация

1977-12-20—Подача