1

Изобретение относится к электроизмерительной технике и может быть использовано для контроля времени Зсщержки включения и выключения интегральных микросхем.

Известны устройства, содержащие блок управления фазой сигнала, формирователь задержки сигнала, интегрирующий конденсатор, фиксатор уровня и формирователь предельно допустимого времени задержки 1 .

Недостатки известных устройств заключаются в низкой достоверности контроля и ограниченных функциональных возможностях.

По основному авт. св. № 720712 известно устройство для контроля времени задержки включения и выключения схемы, содержащее блок управления фазой входного сигнала контролируемой схемы, формирователь предельно допустимого времени задержки, блок управления фазой выходного сигнала контролируемой схемы, формирователь импульсов и блок анализа временного положения сигналов 2 .

Недостатками этого устройства также являются низкая достоверность контроля и ограниченные функциональные возможности, так как данное yctr

ройство не обеспечивает контроля времени задержки контролируемых схем со сложным законом функционирования и дифференциации брака контролируе5 мцх схем по виду.

Цель изобретения - повышение достоверности контроля и расширение фун кциональных возможностей.

Указанная цель достигается тем,

10.что в известное устройство, содержащее блок управления фазой входного сигнала контролируемой схемы, Ьходы которого соединены с соответствующими зажимами контролируемой схемы,

(5 а выход соединен с первым входом блока анализа временного положения сигналов и входом формирователя импульсов, выходы которого соединены соответственно со вторым и третьим

20 входами блока анализа временного положения сигналов, блок управления фазой выходного сигнала контролируемой схемы, входы которого соединены с соответствующими зажимами контро-.

25 лируемой схемы, а выход соединен с четвертым входом блока анализа временного положения сигналов и входом формирователя предельно допустимого времени задержки, выход которого соединен с пятым входом блока анализа

временного положения сигналов, введены блок контроля функционирования контролируемой схемы и четыре элемента совпадения, причем первые входы элементов совпадения соединены с первым выходом блока , контроля функционирования контролируемой схемы, .вторые входы - соответственно с вы-, ходами норма времени задержки включения, брак времени задержки включения, норма времени задержки в.ыключения,брак времени задержки выключения блока анализа временного положения сигналов, третьи входы ссУединены со вторым выходом блока контроля функционирования контролируемой схемы, а выходы .элементов совпадения соединены соответственно с шинами норма времени задержки включения, брак времени .задержки включения, норма времени задержки вы- . ключения и брак времени задержки выключения, первый вход блока контроля функционирования контролируемой схемы соединен с выходом блока управления фазой входного сигнала контролируемой схемы, второй вход соединен с шиной программного значения 1 выходного сигнала контролируемой схемы, третий вход - с шиной прогpaMiviHoro значения О выходного сигнала контролируемой схемы/ а четвертый вход - с выходом блока управления фазой выходного сигнала, при этом блок контроля функционирования контролируемой схемы.содержит три входных триггера, триггер нормы функционирования, триггер брака функционирования, инверторы, два входных и четыре выходных элемента совпадения, причем первый и второй входы 1 триггера брака функционирования соединены соответственно с выходами первого и второго выходных элементов .совпадения, а первый и второй входы 1 триггера нормы функционирования соединены соответственно с выходами третьего и четвертоговыходных элементов совпадения, первые входы всех выходных элементов совпадения соединены с выходом соответствующего инвертора, вход которого соединен с первым входом блока контроля функционирования контролируемой схемы и с первыми входами входных элементов совпадения, выходы которых соединены соответственно с уходами 1 второго и третьего входных триггеров, вторые входы первого и четвертого, выходных элементов совпадения соединены с выходом 1 первого входного триггера и с выходом блока контроля функционирования контролируемой схемы, а вторые входы второго и третьего выходных элементов совпадения соединены с выходом О первого входного триггера, третьи входы первого и третьего выходных элементов совпадения соединены с выходом 1. третьего входного .триггера, а третьи входы второго и четвертого выходных элементов совпадения соединены с выходом 1 второго входМого триггера, выход О которого соединен с первым входом О третьего входного триггера, второй вход блока контроля функционирования контролируемой схемы соединен со входом 1 первого входного триггера, третий вход блока контроля функционирования контролируемой схемы соединен со входом О этого триггера, четвертый вход блока контроля функционирования контролируемой схемы соединен со вторым входом первого входного элемента совпадения и через соответствующий инвертор - со вторымвходом второго входного элемента совпадения, выход 1 триггера брака функционирования подключен к шине брак функционирования, выход 1 триггера нормы функционирования соединен с шиной норма функционирования, а второй вход О третьего входного триггера и входы О второго и третьего входных триггеров и триггеров брака и норма функционирования соединены с соответствующим выходом блока анализа временного положения сигналов ,

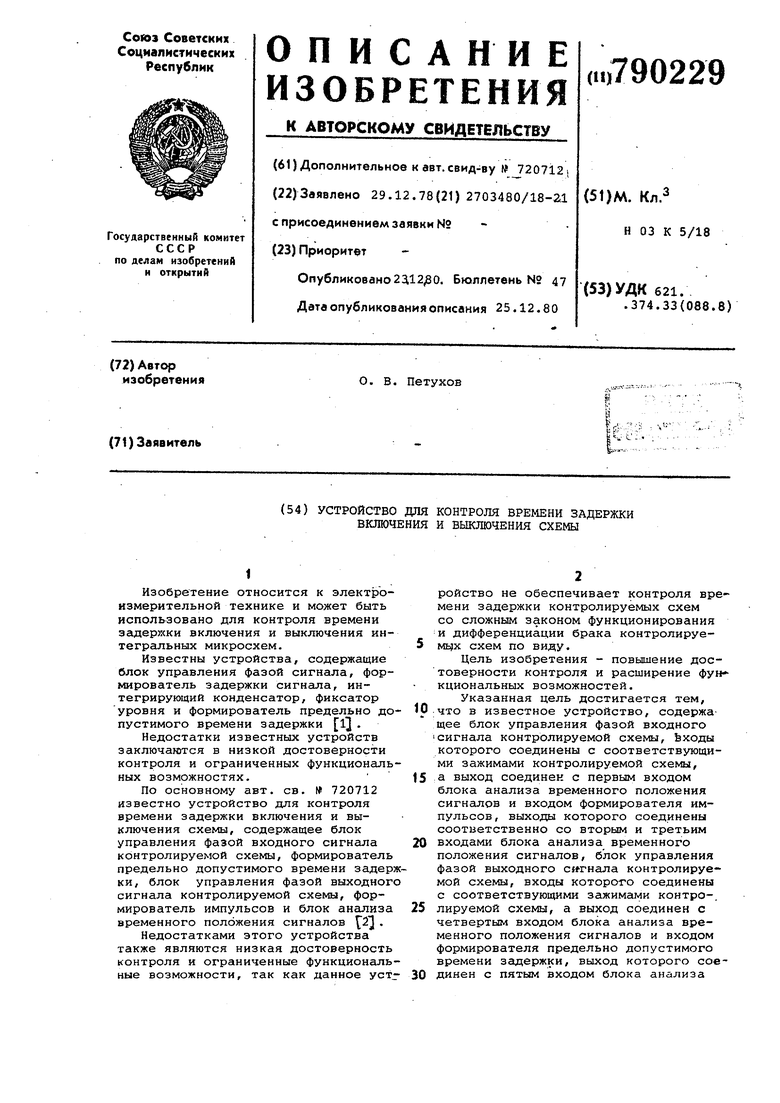

На чертеже представлена 6 noK--cxeма устройства.

Устройство содержит блок 1 управления фазой входного сигнала контролируемой схемы, формирователь 2 предельно допустимого времени задержки, блок 3 управления фазой выходного сигнала контролируемой схемы, формирователь 4 импульсов, блок 5 анали0 3 за временного положения сигналов, содержащий блоки б и 7 определения очередности сигналов и формирователь 8 сигнала исходное, элементы 9, 10, 11 и 12 совпадения блок 13 контроля функционирования контролируемой , содержащий входные триггеры 14, 15 и 16, триггер 17 нормы функционирования, триггер 18 брака функционирования, инверторы 19 и 20, входные элементы 21 и 22 совпадениЯу выходные элементы совпадения 23, 24, 25 и 26, шину 27 норма времени задержки включения, шину 28 брак времени задержки включения, -шину 29 норма времени задержки выключения, шину 30 брак времени задержки выключения, шину 31 брак функционирования, шину 32 норма функционирования,- шину 33 программного значения 1 выходного сигнала контролируемой -схемы и шину 34 программного значения О выходного сигнала контролируемой схемы

Устройство работает следующим образом.

С входа и выхода контролируемой схемы (на чертеже не показана) на входы блоков 1 и 3 управления фазой входного и выходного сигналов контролируемой схемы поступают контролируемые сигналы. При этом при любой полярности входного и выходного сигнала контролируемой схемы на выходах блока 1 управления фазой входного сигнала контролируемой схемы и блока 3 управления фазой выходного сигнала контролируемой схемы формируются положительные сигналы. Сигнал на .выходе блока 3 управления фазой выходного сигнала контролируемой схемы отстает по времени от сигнала на выходе блока 1 управления фазой входного сигнала контролируемой схемы.

При поступлении сигнала на вход формирователя 2 предельно допустимого времени задержки на его выходе появляется положительный сигнал, задержанный на величину, допустимую для данной контролируемой схемы.

Сигнал с блока 3 управления фазой выходного сигнала контролируемой схемы поступает на один из входов блока 5 анализа временного положения

сигналов и на вход формирователя 4 импульсов. Сигналы с выходов формирователя 2 предельно допустимого времени задержки поступают соответственно на соответствующий вход блока 5 анализа временного положения сигналов и на соответствующий вход

формирователя 4 импульсов.

Анализ времени задержки .включения контролируемой схемы производится блоком б определения очередности сигналов блока 5 анализа временного положения сигналов.

Если длительность времени задержки включения контролируемой схемы не превышает предельно допустимого значения времени задержки включения, то на первый вход блока б определения очередности сигналов сигнал посупит раньше, чем на еговторой вход оединенный с выходом формирователя 2 предельно допустимого значения задержки, и на выходе блока 5 анализа ременного положения сигналов, соеиненным с элементом 9 совпадения, появится положительный сигнал норма.

Если длительность времени задержки включения контролируемой схемы превысит предельно допустимое значение времени задержки включения, то на вход блока 5 анализа временного положения сигналов, соединенный с формирователя 2 предельно допустимого времени задержки, сигнал поступит раньше, чем на другой его вход, и на выходе блока 5 анализа временного положения сигналов, соединенном со вторым элементом 10, появится положительный сигнал брак.

Для анализа времени задержки выключения сигналы, поступающие на входы формирователя 4 импульсов, дифференцируются по заднему фронту а затем-поступают на соответствующие входы блока 7 определения очередности сигналов, блока 5 анализа -временного положения сигналов. , Если длительность времени задержки выключения контролируемой схемы не превышает предельно допустимого

0 значения времени задержки выключения, то на выходе блока 5 анализа временного положения сигналов, сбединенном с элементом 11 совпадения, появится положительный сигнал нор5ма . В противном случае на выходе блока 5 анализа временного йоложения сигналов, соединенном с элементом 12. совпад1 ния, появится положительный сигнал брак..

Выходные сигналы блоков 1 и 3 уп0равления фазой входного и выходного сигналов контролируемой схемы поступают также в блок 13 контроля функционирования контролируемой схемой, который осуществляет сравне5ние выходного сигнала контролируемой схемы с его программным значением О или 1, задаваемым по шинам программного значения 1 или О выходного сигнала контроли0руемой схемы 33 и 34 соответственно. Одновременно с сигналами О или 1 на соответствующий вход блока 13 контроля функционирования контролируемой схемы поступают такто5вые сигналы. По результатам сравнения блок 13 контроля функционирования контролируемой схемы в случае совпадения программного и действительного выходных сигналов контролируемой схемы выдает по шине 32

0 норма функционирования разрешающий сигнал корма функционирования на соответствующие входы элементов i9, 10, 11 и 12 совпадения.

Если при этом программное значе5ние выходного сигнала соответствовало 1, то с другого выхода блока 13 контроля функционирования «онтро:лируемой схемы .подается также разрешающий сигнал на те же элементы

0 9, 10, 11 и 19 совпадения и на шины норма времени задержки включения, брак времени задержки включения, норма времени задержки выключения и брак времени задержки вы5ключения 27, 28, 29 и 30 соответственно, выдается результат конт.роля задержек включения и выключения контролируемой схемы.

При несовпадении программного

0 и действительного значений выходного сигнала контролируемой cxeivbi блок контроля функционирования контролируемой схемы формирует на шине 31 брак функционировании сигнал брак функционирования, а сиг5

нал по шине 32 норма функционирования запрегцает выдачу сигналов с . ыходов блока 5 анализа временного положения сигналов на шину 27 нора времени задержки включения ину 28 брак времени задержки включения, шину 29 норма времени задержки выключения и шину 30 брак времени задержки выключения.

Блок 13 контроля функционирования онтролируемой схемы работает слеующим образом.

В исходном состоянии входные триггеры 15 и 16, триггер 17 нормы ункционирования и триггер 18 браа функционирования находится в состоянии О, а входной триггер 14 в роизвольном состоянии.

При поступлении тактового сигнала с выхода блока 1 управления фазой входного сигнала контролируемой схеы и сигнала программного значения О или 1 входной триггер 14 включается соответственно в состояние О или 1, а входной триггер 16 начинает переключаться в состояние 1 под действием входного сигнала с выхода входного элемента 22 совпадения, так как в первый момент времени сигнал на одном из входов входного элемента.22 совпадения отсутствует (из-за задержки выходного сигнала контролируемой схемы), а на другом входе.tвходного элемента 22 совпадения присутствует положительный (разрешающий) потенциал,

При поступлении затем выходного сигнал а блока- 3 управления фазой выходного сигнала контролируемой схемы срабатывает входной элемент 15 совпадения, и включается входной триггер 15, который отрицательным сигналом со своего выхода О сбрасывает входной триггер 16 в исходное состояние.

Сигналы с выходов входных триггеров 14, 15 и 16 подаются на выходные элементы 23, 24, 25 и 26 совпадения, ца входах которых во время действия тактового сигнала происходит установка всех сигналов. Затем по окончании тактового сигнала срабатывает один из четырех выходных элементов 23, 24, 25 и 26 совпадения, осуществляющих сравнение программных и действительных значений выходных сигналов коитролируемой схемы и включается триггер 17 нормы функционирования либо триггер 18 брака, функционирования. Сигналы с выходов 1 входного триггера 14 и триггера 17 нормы функц-ионирования управляют элементами 9J 10, 11 и 12 совпадения, через которые либо пропускаются сигналы с выходов блока 5 анализа временного полохсенйя сигналов, либо нет.

По переднему фронту тактового сигнала на выходе формирователя 8

сигнала исходное появляется отрицательный сигнал, устанавливающий 6 и 7 определения очередности сигналов и блок 13 контроля функционирования контролируемой схемы в исходное состояние.

При применении устройства повышается достоверность контроля за счет исключения режимов, при которых устройство фиксирует ложный результат и расширяются функциональные возможности устройства, так как оно позволяет контролировать интегральные схемы со сложным законом функционирования и дифференцировать брак по виду.,

Формула изобретения

1.Устройство для контроля времени задержки включения и выключения схемы по авт. св. № 720712, отличающееся тем, что, с целью повышения достоверности контроля и расширения функциональных возможностей, в него введены блок контроля функционирования контролируемой схемы и четыре элемента совпадения, причем первые входы элементов совпадения соединены с первым выходом

блока контроля функционирования

контролируемой схемы, вторые входы соответственно с выходами норма времени задержки включения, брак времени задержки включения, норма

времени задержки выключения, брак времени задержки выключения блока анализа временного положения сигналов, третьи входы соединены со вторым выходом блока контроля функционирования контролируемой схемы, а

выходы элементов совпадения соединены соответственно с шинами норма времени задержки включения, брак времени задержки включения, норма времени задержки выключения и брак

времени задержки выключения, первый вход блока контроля функционирования контролируемой схемы соединен с выходом блока управления фазой входного сигнала контролируемой схемы,

второй вход соединен с шиной программного значения 1 выходного сигнала контролируемой схемы, третий вход - с шиной программного значеш я О выходного сигнала контролиру емой схемы, а четвертый вход - с выходом блока управления фазой выходного сигнала,

2.Устройство по П.1, отличающееся тем, что блок контроля функционирования контролируемой схемы содержит три входных триггера, триггер нормы .функционирования, триггер брака функционирования, инверторы, два входных и четыре выходных элемента совпадения,

причем первый и второй входы 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля времени задержки сигнала | 1977 |

|

SU699667A2 |

| Устройство для контроля времени задержки включения и выключения контролируемой схемы | 1977 |

|

SU720712A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля счетчиков импульсов | 1985 |

|

SU1248061A1 |

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

| Устройство для контроля переходного сопротивления электрических контактов коммутационных изделий | 1983 |

|

SU1129566A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| УСТРОЙСТВО ДЛЯ ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1990 |

|

RU2024906C1 |

| Устройство для контроля модулей коммутации | 1984 |

|

SU1273931A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

Авторы

Даты

1980-12-23—Публикация

1978-12-29—Подача