1

Изобретение относится к области вычислительной техники и предназначено для npHMeHeHifflt в цифровых вычислительных машинах, работающих в системе остаточных классов.

. Известно устройство для обнаружения ошибок в системе остаточньтх классов по авт. св. MO 519714, содержащее два блока памяти, сумматоры, сумматоры по мо-.

блока памяти, выходы второго и третьего сумматоров через второй и третий преобразователи в дополнительный код соответственно соединены с первыми входами сумматоровпо модулям Рц и Р первого уровня, вторые входы которых роответственно соединены с контрольными входами устройства, а выходы - с первыми входами сумматоров по модулям

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в системе остаточных классов | 1974 |

|

SU519714A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1980 |

|

SU960823A1 |

| Устройство для формирования позиционных характеристик непозиционного кода | 1981 |

|

SU968802A1 |

| Устройство для сравнения чисел в системе остаточных классов | 1985 |

|

SU1282116A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| Преобразователь кода числа из системы остаточных классов в напряжение | 1982 |

|

SU1069155A1 |

| Таблично-алгоритмический функциональный преобразователь | 1979 |

|

SU860079A1 |

| Устройство для обнаружения ошибок в модулярном коде | 1985 |

|

SU1295528A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЛА ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД С КОРРЕКЦИЕЙ ОШИБКИ | 2006 |

|

RU2309535C1 |

| Арифметическое устройство в системе остаточных классов | 1980 |

|

SU881745A1 |

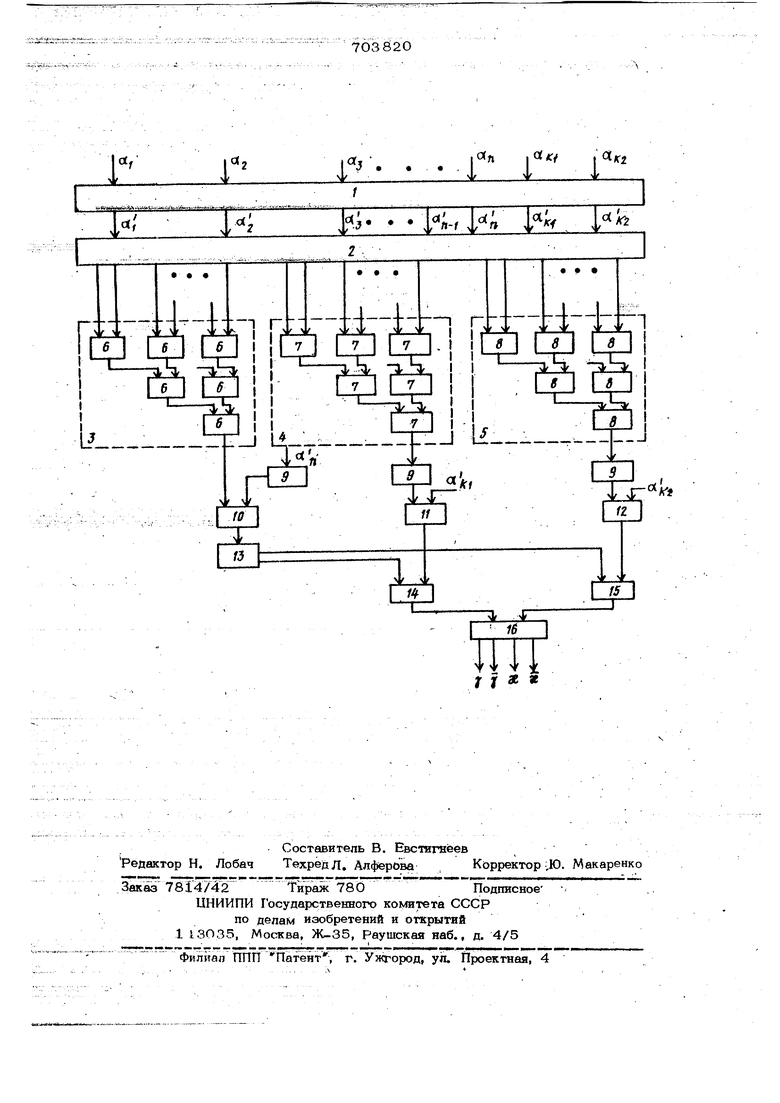

(№ « iuS4fe ffsfi - ;p. же нат1чие диапазона неоднозначности р спопоженнотх внутри диапазона представления, в результате чего числа, одно-, временно удовлетворяющие условию где А - контролируеА SX число и М . - минимальное псевдоортогональное число, сформированное по цифрр о(.|. при конгрйЛеих на правильность с помощью описанного устройства будут признаны ;неискаженными, хотя в действительности они искажены. При этом невозможно однозначно определить номер интервала , в котором р1асположёно контролируемое число. Целью изобретения является повышение точности определения ошибочного основания. . Поставленнай цель досгйгаётся Тем, что устройство дополнительно содержит. (:V1+2 ) входных сумматоров по модулям системы остаточных классов,- выходы первых ( Vl-1)- входных сумматоров соединены со входами первого блока памяти выход h-ro входного сумматора- - со входом первого преобразователя в допол-. нительный код, выходы ()-ro и {t1 + 2)-ro входных сумматоров соединены соответственно со вторыми входами Сумматоров по модулям R. и Р первого 14 «Ч уровня. На чертеже представлена блок-схема; устройства для обнаружения ошибок в си сте1Лё -остаточнь1Хклассов, л Устройство содержит )1i+ 2 входных Сумматоров 1, первый блок 2 памяти, су маторы , в сбстав которых входят сумматоры 6-8 соответственнЬ по модулям Р п РК РК преобразователи 9 в :дополнительныйкод, сумматоры 10 12 соответственно по модулям Р , Р|,. и Р /первого уровня, второй блок 13 памяти, сумматоры 14 и 15 соотЁ етственно по модулям Р - и Р ц второ го урЪвня, блок 16 формирования сигнала ошибки. ......1,.,,.-.,: -. Устройство работает следующим образом. , На входы устройства инфррмагшя, соответствующая представлени контролируемого числа в системе остаточ 11ых к1ассЬв Jib 1вс ёй оСНЬванияМ, ьключая контрольные. В сумматорах 1 исходный КОД кбнтгкэпируемого числа подвергается: модификации, соответствующей вычитанию из контролируемого Числа А постоянной величины В таким образом что на выходе преобразователя 9 образуется код. 0 соответствующий числу А А-В, где . (, .V При контроле чисел на правильность данньш способом числа, находящиеся в диапазоне к-Р. (к+1)- Р и отвечающие условию к- Р + М ггхсжх - Pfp , даНут по контрольному основанию цифру, соответствующую номеру диапазона к, а числа, отвечающие условию к-Р + с(кР)+Р, - цифру, соответствующую номеру (к+1).. удовлетворяющего условтао При вычйтан1йи из исходного числа, к- Р А (к+1) -Р- (М tncLf -Р). В получим число (к-1 )-Р + М так ДЧ к P-f Р , котброе при контроле даст пифру, соответствующую истинному номеру дйапазона к. Числа, удовлетворяющие условию (к+1)Р - ( )(к+1), сместятся при тбм в,диапазон (к-1)-Р1-Р , (к-1)-Р+ МтаЛ и составят диапазон неоднозначности, т.е. тем сЙМым диапазон неоднозначности смещается в конец диапазона представления и не использоваться.. Информация модифицированного кода, соответствующая Остаткам по основаниям Р| (1 1,2, ..., (п-1)). поступает на блок 2 памяти, где в зависимости от величин oCi соответствующих вычетов происходит формйрОВание следов минимальных псевдоортогональных чисел по основанию Ри и вепйчйн, равных остаткам каждо го минимального псевдоортогонального числа по контрольным основаниям Р иРка, сП ( . SVl /l T,, t w I JI I V/ ) ot oC,j C3L ct ct S.KZtt . 4i поступающих на сумматоры 3-5, в состав которых входят сумматоры 6-8 соответственно по модул йм Рд, Рц, и В результате суммирования по каждому модулю PY,, Р и Р 2,число тактов которого бпределяется как t i:togr,.(h-iy,где знак L 3 означает ближайшее целое, на выходе сумматоров 3-5 будут получены суммы соответствующих следов ч - V CL чг« ( V tS ., ,5 , S 5 --i 1r которыепередаются на сумматоры lOl 2 по модулям Р, РК-( Кг рво57формирующие на выходе лелйго уровня чины .-.n; S- K;s--u x. при этом cty, S,и S 2передаЮТСЯ через соответствующие преобразователи 9 в дополнительный код, а oCL является величиной с -го выхода сумматора 1. По величине ЛоС в блоке 13 памяти формируются величины, соответствующие остаткам ошибки представления чисел по основаниям, РК/ и 1, JAA HmodP),/VA (mod Р, которые поступают на сумматоры 14 и 15 по модулям Рц и Р,2 второго уровня, где происходит формирование цифр. , в .зависимости от величин этих цифр в , блоке 16 формирования сигнала ошибки исходит выработка сигналов или и Эб 0 или йе 1, которые несут информацию о знаке числа (у 0 соответствует числам ) и об егб правипьности ( соответствует неискаженным числам). Для выполнения операции обнаружения ошибок в предлагаемом устройстве требуется количество тактов сложения по моду. лю, определяемое выражением, 20 r--b- - Eo 2C -1 r и два такта обращения к блокам памяти. Использование сумматоров 1 позволяет существенно расширить диапазон правильных чисел, обеспечивает однозначное определение основания, по которому имеется факт искажения, ;и сдвиг диапазона неоднозначности и конец рабочего диапазона. Формула изобретения Устройство для обнаружения оишбок в системе остаточных классов по авт. св. № 519714, о. тличающееся , тем, что, с целью повышения точности определения ошибочного основания, устройство дополнительно содержит (п+2) входных сумматорой по модулям системы остаточных классов, выходы первых ( ) входных сумматоров соединены со входами первого блока памяти, выход rt-ro входного сумматора - со входом первого п юобразователя в дополнительный код, выходы (h+l)-ro и (Vi+2)-ro входных сумматоров соединены соответственно со вторыми входами сумматоров по моду . . . . . лям Р.КЧ и g. первого уровня, Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 519714, Q/06 F 11/О8, 1974 (прототип). b

I « I

ТПТ

т f « «

Авторы

Даты

1979-12-15—Публикация

1976-12-21—Подача