(54) УСТРОЙСТВО ДЛЯОБ;-.;АР5ОКЕ -ШЯ;О1.ШБОК В СИСТЕМЕ ОСТАТОЧНЫХ Ir; ПАССОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в системе остаточных классов | 1976 |

|

SU703820A2 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1989 |

|

SU1780191A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1988 |

|

SU1569996A1 |

| Устройство для обнаружения ошибок в модулярном коде | 1985 |

|

SU1295528A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для исправления ошибокВ СиСТЕМЕ ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU842820A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПЕРЕПОЛНЕНИЯ ДИНАМИЧЕСКОГО ДИАПАЗОНА, ОПРЕДЕЛЕНИЯ ОШИБКИ И ЛОКАЛИЗАЦИИ НЕИСПРАВНОСТИ ВЫЧИСЛИТЕЛЬНОГО КАНАЛА В ЭВМ, ФУНКЦИОНИРУЮЩИХ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2011 |

|

RU2483346C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИСПРАВЛЕНИЯ ОШИБОК В ИЗБЫТОЧНОМ МОДУЛЯРНОМ КОДЕ | 1991 |

|

RU2015620C1 |

| Устройство для вычисления сумм парных произведений в полиномиальной системе классов вычетов | 2016 |

|

RU2622881C1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1989 |

|

SU1633497A1 |

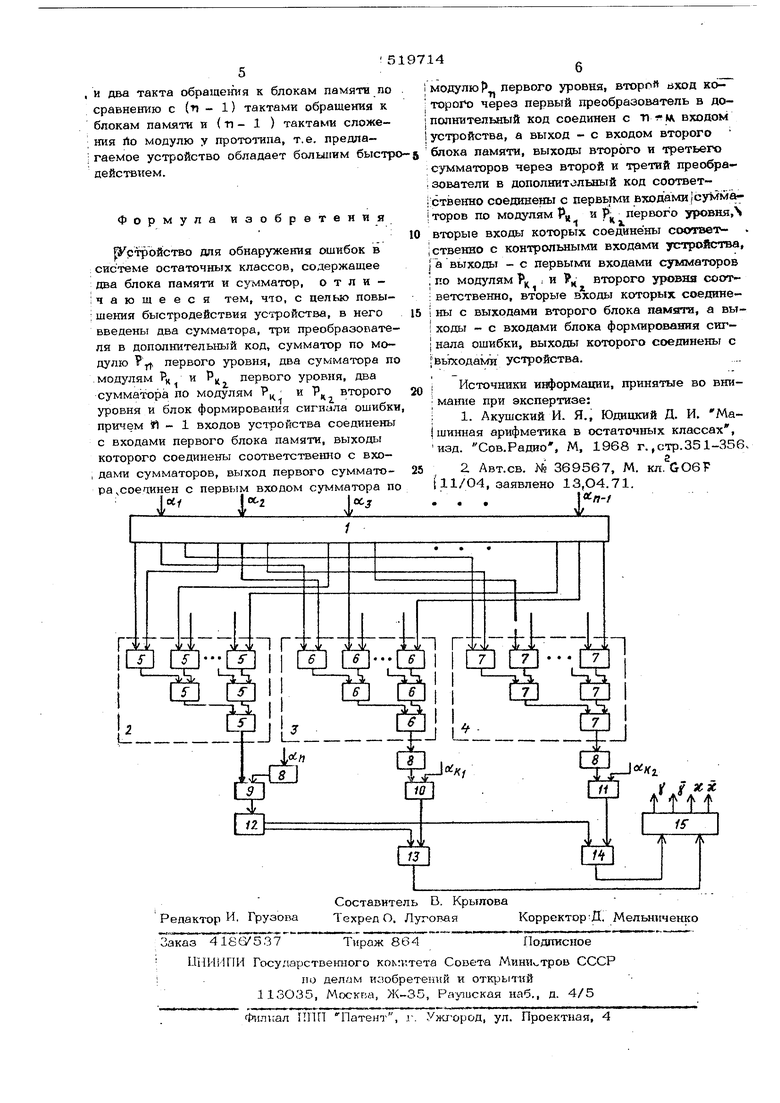

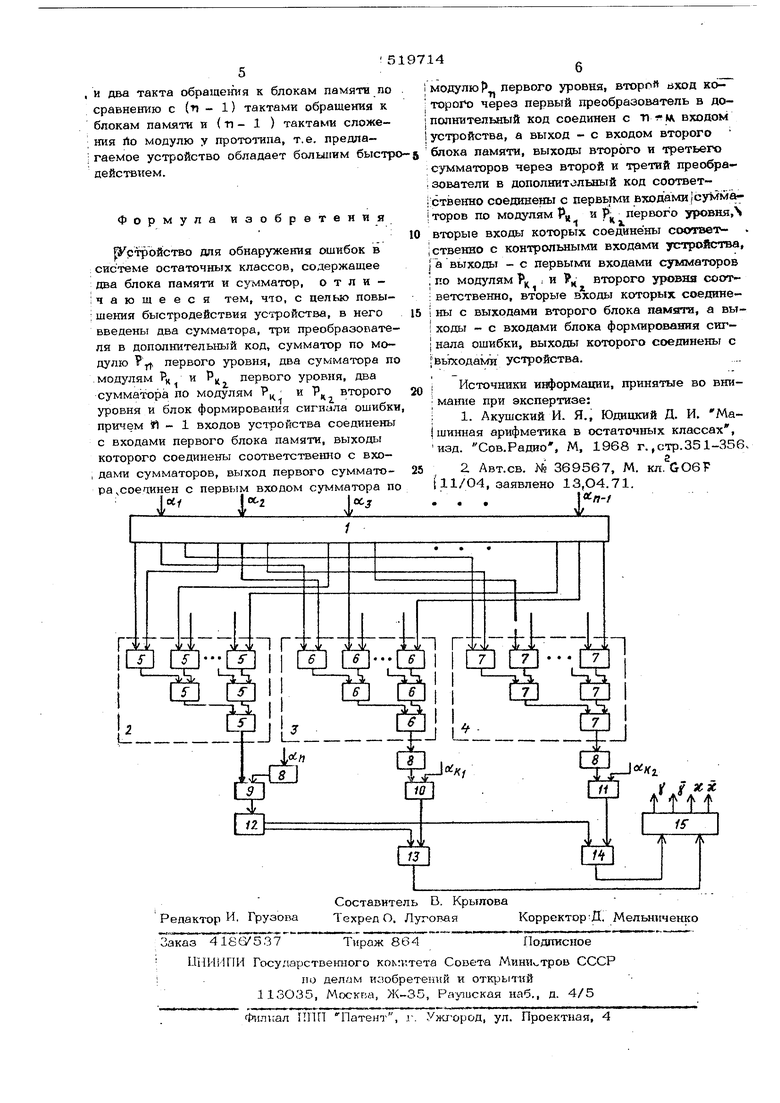

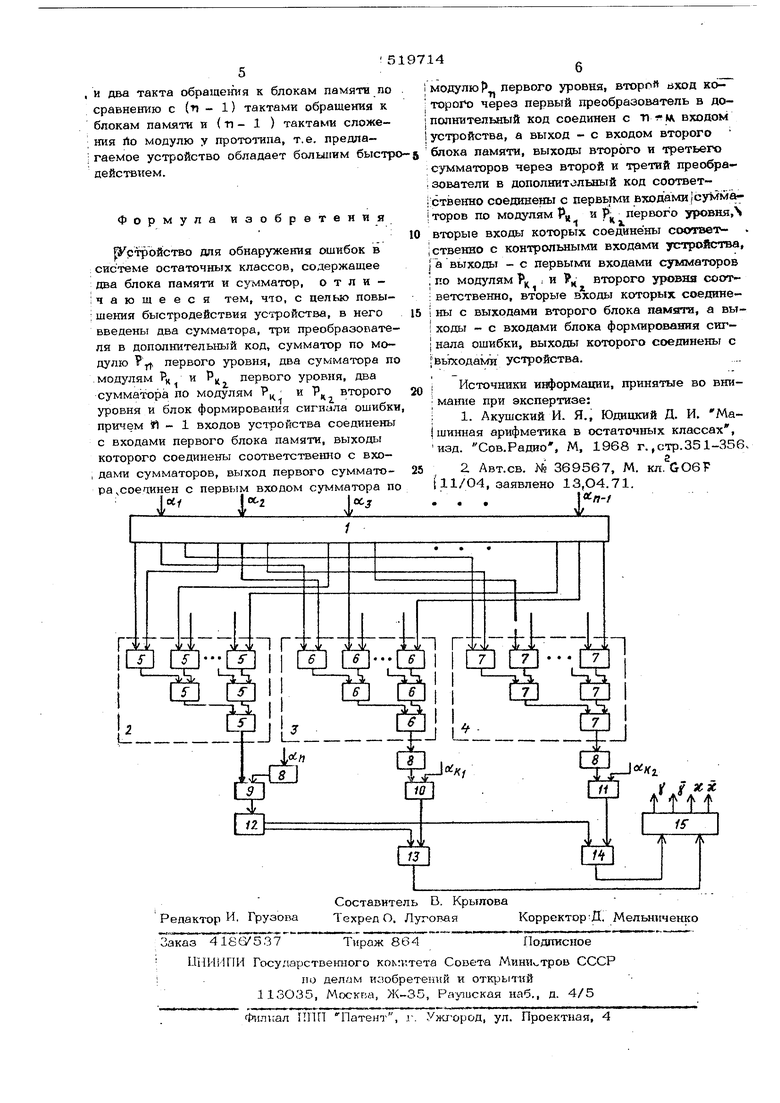

Изобретение относится к области нычис питепьной техшнга и предаазт13:9но для гцзй менен.ш в дифровык машинах испольэуюидих форь/г - преГ|Ст.аЕ.аевпйя --пг сел в системе остаточяьтх. классов. Известны устройства дкк обнар;Ж.екк/;: ошибок в системе остаточ гых классов, Одно из известных устройсГ.: ...-гдерл-шт блока памяти константлт./певкйадтгИ и ошибок, cyiviis aTOp : 1. Для контроля чисел в элом устпсястве используется метод 1шся8дс-Еа:еелы1Ой нул низании, когда 753 иеходлог;; числа, представленного з COKj вычитс.ются : :онс;«нты нулевЕзашги (шнимaльньJG чиег(а) вида . j.: где i ss- 1э 2,;- , (i-s i; га Hj-jie BsemiKj tl - колзче:;твс cr:vi,.3e.HKtj об; нрадстаале::-:ия ;; ОИЮВаШ : vHL,, При Еыколнехгчд оп-радии в устройс гвс псютупйют ocTavKi; ло сснованалы oof Ci e иваюшчивй-тотщи-л рабочий .диагшаон, к остатки .по КОНТОО51Ы-1ЫМ основаггаям. По таблицам мнтп рльнъ1х Каюёл: проводится формирование спзредных констант нулевизащга, 1к.отдрые, йСХтедовательтш вычитаются из исходного Iчкила. ; В реяу-льтате нулевиаашш по всем осно- I загг;1.:т., о6ес,,еч.ивающим рабочий диапазон, I сю коГлрольг1ым осиоваШШМ получаются цкфi :-ьТ; величина которых несет кн{)ормаи:ию о I она.ке числа и его правилы ости. ЬКедостаток такого устройства - низкое 6ь: ото Сдействие, так как операция контроля ;и определ91шя знака требует И тактов мо- j чуя з1юго вычитания и столько же тактов обрашеШЩ к таблгщам минимальных чисел. Наиболее близкие t техническим решением I- ттообретакгкс Евляется устройство, которое -:- .:vj/;r::T гоа блока памяти и сумматорp j. ; О;::ако это ycTpoiicTBo также имеет низliios бьютродействие. Цель изобретегшя -- повышеггае быстро тейстзик устройства, : Это достигается тьм, что в устройство взвденъ: два cyMi-;aropa, три преобразователя в дополнительный код, сумматор по МОмодулям р.. и р.. первого уровня, два 1 J -. сумматора по моду/. IM.PK , и Tnj, второго уровня и блок формирования ошибки; И - 1 входов устройства соединены с входаклг первого блока памяти, ( выходы которого связаны соответственно; с входами сумматоров, выход первого сумматора подключен к первому входу сумматора по модулю р„ первого уровня, второй вход ко торого через nepBbrfi преобразователь в дополнительный код соединен с П -м входом устройства , а выход it- с входом второго блока памяти. Выходы второго и третьего сумматоров через второй и третий преобразователи в дополнительный код соответстве но подключе1а1 к первым входам сумматоро по модулям Ptt и Fj, первого уровня, Кi К вторые входы которых соединены соответственно с контрольными входами устройства а выходы - с первыми входами сумматоров по модулям Р(4 и j второго уровня соответственно, вторые входы которых связаны с выходами второго блока памяти, а выходы с входами блока формирования сигнала ошибки. Выходы последнего соединены с вы ходами устройства. Схема устройства приведена на чертеже Устройство содержит блок 1 памяти, cyi.rMaторы 2, 3, 4, сумматоры 5 по модулю Р сумматоры 6 по модулю Pj , сумматоры по модулю Рц , преобразователи 8 в допол нительш й код, cyммa x)p 9 но К1одулю Р первого урог.ш, сумматоры 1О и 11 но мо дулю PJJ и Pg первого уровня, блок 12 памяти, сумматоры 13 и 14 по модулям Р и Р Бторого уровня, блок 15 формирования сигнала ошибки. Работает устройство следующим образом На входы устро 1ства подается ииформация, соответствующая представлению конт ролируемого числа в системе остаточных классов по всем основаниям, включая контрольшлте. При этом ит1формаш1я, соответству щая остаткам по основаниям р { i « 1,2.,--.tl nocTj naeT на блок 1 памяти, где в зависимости от соответствующих остатко ci-я происходит формир&Ьание следов минимальных псевдоортогоиальных чисел no осн ванию Р и величин, рапных остаткам каж до1о v.ИIП( пссвдоортогонлльного числа по контрольным основаниям и Р, т.е. s s пч Ki кг л t4 оторые поступают на сумматоры 2, 3, 4 , состав которых входят сумматоры по моулям р.. р.. , РК соответственно. результате суммирования по модулям число тактов которого определяется к ttog- di-i), де знак означает ближайшее большее цеое, на выходе сумматоров 2, 3, 4 будут поучены суммы соответствующих следов A i-i M.;i к, .А . oL Ii 1 : ss:; 1 которые передаются на сумматры по мо дулям PTI , Pj( , P|ii., первогч) уровня,. а выходе которых получаются величиньг. Г-п/ К1Kil А о(. оС - S . К1 А , кг-tiz. , с .ка При этом величины о1 s Б. ., S, передаются через соответствующие преобразогэтели .i допол1гательный код. По величие Л rfw я в блоке 12 памяти формиУЮ1СЯ величины, соответствующие остаткам} шибки представления чисел по ocHoaairaмк i А А (jjiod Р. ), U А (mod Р., ) которые поступают на сумматоры по модуля /Р и Р| второго уровня, где формируются цифры или л т., доС (mod Р. УК ДДА (modP В зависимости от величин этих цифр в блоке формирования сигнала ошибки происходит выработка сигналов fsQ или jf 1 и - О, X : 1, которые несут ин-формацию о знаке числа ( f « О соответствует числам ) и об их правильности ( Э SJ.Q соответствует неискаженным числам). Для выполнения операции обнаружения ошибок в предлагаемом устройстве требуется количество тактов сложения по модулю, определяемое выражением -Clog а(п-1)Л,; , и два такта обращения к блокам памяти по сравнению с {П - 1) тактами обращения к блокам памяти и (п - 1 ) тактакш сложения rto модулю у прототипа, т.е. предпа- ППМ «U iVH UJJLl ,Т . , .,, ..,-4 ; гаемое устройство обладает большим быстр действием. Формула изобретения |Устфойство для обнаружения ошибок в ; системе остаточных классов, содержащее два блока памяти и сумматор, о т л и :чающееся тем, ч1о, с целью повы; шения быстродействия устройства, в него введены два сумматора, три преобразователя в дополнительный код, сумматор по модулю F первого уровня, два сумматора п , модулям и ц первого уровня, два сумматора по модулям к, второго уровня и блок формирования сигнала ошибк причем Я - 1 входов устройства соединены с входами первого блока памяти, выходы которого соединены соответстве1шо с вхо, дами сумматоров, выход первого сумматора соеоинен с первым входом сумматора п F.|Л модулю Р первого уровня, второй БХОД к6торогЧ) через первый преобраэоватепь в дополнительный код соединен с п f ил входом устройства, а выход - с входом второго ., блоха памяти, выходы второго и третьего --. IV ,.. .j.fti Jtj сумматоров через второй и третий преобразователи в дополнитчзльный код соответ1:ственно соединены с первыми входами су1 ма1 торов по модулям Рц РК перЕюго уровня, вторые входы которых соединены соответ ;ственно с контрольными входами устройства, 1 а выходы - с первыми входами сумматоров по модулям : и ц второго уров соответственно, вторые которых соединены с выходами второго блока памягга, а выходы - с входами блока форкгароваяня сигнала ошибки, выходы которого соединены с вьЬсодамтя устройства. Источники информации, принятые во внимание при экспертизе: 1. Акушский И. Я., Юдицкий Д. И, Машинная арифметика в остаточных классах, изд. Сов.Радио , М. 1968 г.,стр.351-356 , 2. Авт.св. № 369567, М. кл.СОб ill/04, заявлено 13,04.71. -

Авторы

Даты

1976-06-30—Публикация

1974-08-13—Подача