Изобретение относится к электросвязи и может быть использовано для контроля состояния дуплексных дискретных кансопов в автоматизированных системах связи.

Цель изобретения - повышение достоверности контроля при изменеьшях полярности сигнала в дискретном кана ле связи.

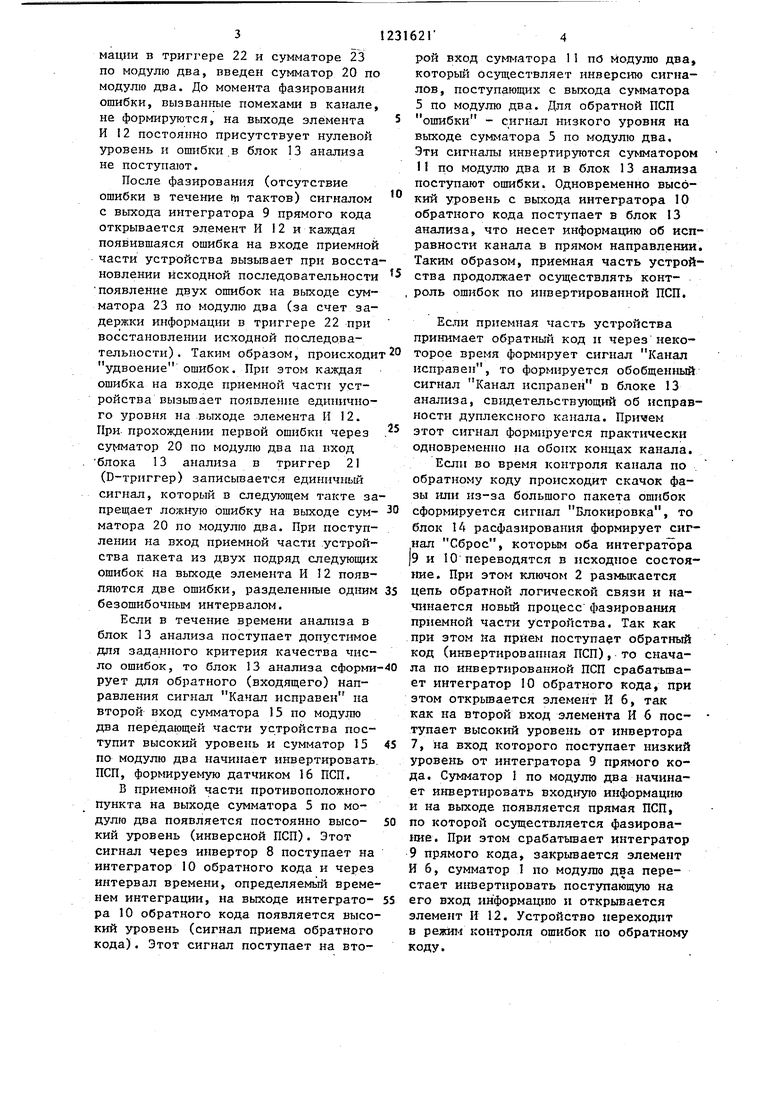

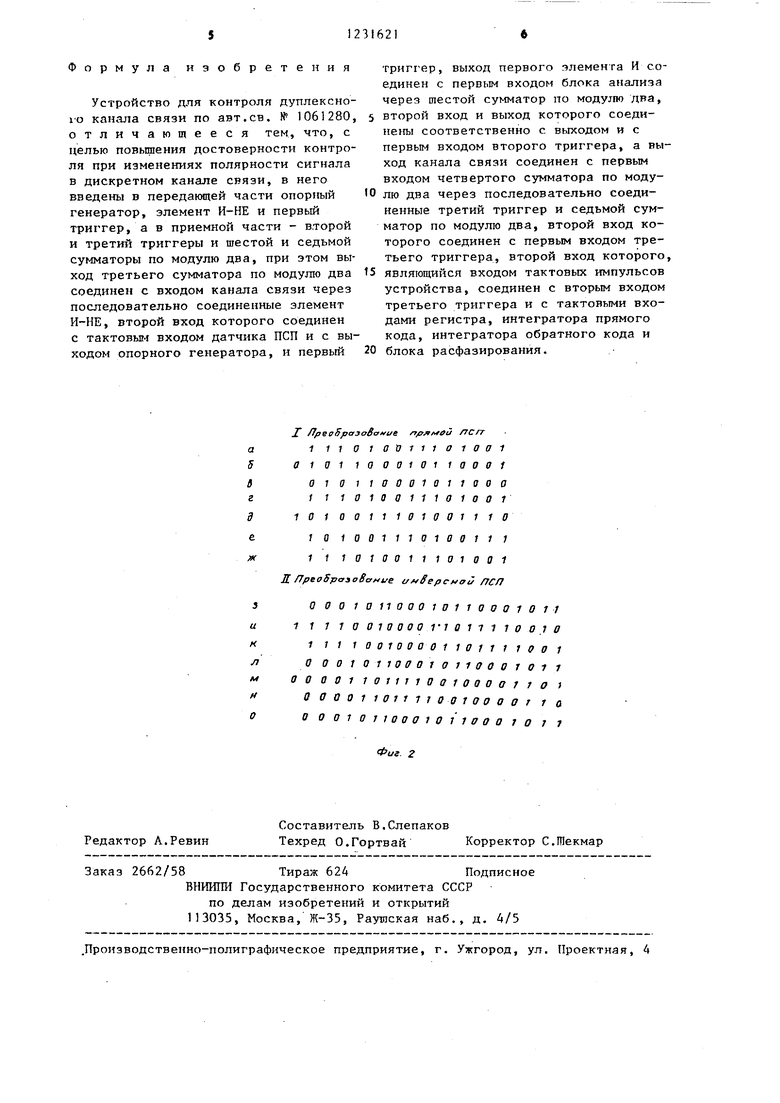

На фиг.1 изображена структурная электрическая схема устройства для контроля дуплексного канала связ.и, на фиг.2 - структура контрольной последовательности в различных .точках устройства.

Устройство содерлсит четвертый сумматор 1 по модулю два, ключ 2, регистр 3, второй сумматор 4 по модулю двг первьй сумматор 5 по модулю два, второй элемент И б, первьй 7 и второй 8 инверторы, интегратор 9 прямого кода, интегратор 10 обратного кода, пятый сумматор П по модулю .два, первый элемент И 12, блок 13 анали- за, блок 14 расфазирования, третий cyi-шатор 15 по модулю два, датчик 16 псевдослучайной последовательности СПСП), опориьп генератор 17, элемент И-НЕ 18, первьй триггер 19, шестой сум -1атор 20 по модулю два, второй 21 и третий 22 триггеры и седьмой сумматор 23 по модулю два.

Устройство работает следующим образом. °

Датчик 16 ПСП формирует прямую контрольную ПСП.(фиг.2а), которая после сумматора 15 по модулю два сохт раняется в прямом виде либо преобразуется в инверсную (фиг.2з) ПСП (со- ответственно при низком или высоком уровне на втором входе сумматора 15 по модулю два). Па выходе элемента И-ПЕ 18, на второй вход которого поступают сигналы тактовой частоты, фор- мируется импульсная последовательность, каждый импульс которой соответствует 1 в исходной ПСП, Задними фронтами сформированных в элементе И-ПЕ 18 импульсов осуществляется пе- реключение триггера 19, с выхода которого информация поступает в канал (фиг.26 и 2д - для прямой ПСП, фиг.2и и 2м - для инверсной ПСП) .Пафиг;-2б2г и соответственно на фиг.2д - 2ж приведены два варианта преобразования прямой ПСП в зависимости от начальной фазы триггера 19. Нафиг.2и2л и фиг.2м - 2о - то же, для инверсной ПСП.

В приемной части с помощью триггера 22 (фиг.2в и 2е или фиг.2к и 2н) И; сумматора 23 осуществляется преобразование поступающей на вход последовательности в последовательность, соответствующую исходной последовательности, формируемой датчиком 16 ПСП на передаче (фиг.2г и 2ж или фиг.2л и 2о).; На вход сумматора 1 поступает прямая или инверсная восстановленная ПСП. В исходном состоянии интегратор 9 прямого кода и интегратор IО обратного кода установлены на ноль, и на их выходах имеются низкие уровни напряжения.

Поступающая на вход сумматора 1 прямая ПСП не инвертируется и поступает через ключ 2 и регистр 3 на сумматор 4 по модулю два. На cyi iMaTope 5 по модулю два осуществляется сравнение входной информацрш с информацией, прошедшей через регистр 3 и сумматор 4 по модулю два. Если, поступающая на сумматор 1 информация соответствует закону формирования прямой ПСП, то на выходе сумматора 5 по модулю два не появляется сигнал Ошибка прямого кода. Если в течение т тактов ПСП поступает без ошибок, то на выходе интегратора 9 прямого кода появляется высокий уровень, который переводит ключ 2 в положение, при котором информация с выхода сумматора 4 по модулю два поступает на вход регистра 3. При этом регистр 3 и сумматор 4 по модулю два образуют эталонный синфазный датчик ПСП.На сум1 1ато- ре 5 по модулю два осуществляется сравнение входной информации с информацией, сформированной этим эталонным датчиком. Если во входной информации присутствуют ошибки, то эти ошибки через открытьш элемент И 12 поступают па вход сумматора 20. При этом для прямой ПСП опгабками является высокий уровень сигнала на выходе сумматора 5 по модулю два, а так как на выходе интегратора 10 обратного кода - низкий уровень, то сумматор 11 пропускает эти ошибки на вход элемента И 12 без инверсии.

Ошибки с выхода элемента И 12 поступают через сумматор 20 по модулю два на вход блока 13 анализа. Для исключения возможности удвоения ошибок, вызванных преобразованием инфорнации в триггере 22 и сумматоре 23 по модулю два, введен сумматор 20 по модулю два. До момента фазирований ошибки, вызванные помехами в канале, не формируются, на выходе элемента И 12 постоянно присутствует нулевой уровень и ошибки в блок 13 анализа не поступают.

После фазирования (отсутствие ошибки в течение in тактов) сигналом с выхода интегратора 9 прямого кода открывается элемент И 2 и калздая появившаяся ошибка на входе приемной части устройства вызьгеает при восстановлении исходной последовательности появление двух ошибок на выходе сумматора 23 по модулю два (за счет задержки информации в триггере 22 при восстановлении исходной последовательности) . Таким образом, происходи удвоение ошибок. При этом каждая ошибка на входе приемной части устройства вызьшает появление единичного уровня на выходе элемента И 12. При прохождении первой ошибки через cyt maTop 20 по модулю два на вход блока 13 анализа в триггер 21 (D-триггер) записывается единичный сигнал, который о следующем такте запрещает ложную ошибку на выходе сум- матора 20 по модулю два. При поступлении на вход приемной части устройства пакета из двух подряд следующих ошибок на выходе элемента И I2 появляются две ошибки, разделенные одним безошибочным интервалом.

Если в течение времени анализа в блок 13 анализа поступает допустимое для заданного критерия качества число ошибок, то блок 13 анализа сформи рует для обратного (входящего) направления сигнал Канал исправен па второй вход сумматора 15 по модулю два передающей части устройства поступит высокий уровень и сумматор 15 по модулю два начинает инвертировать ПСП, формируемую датчиком 16 ПСП.

В приемной части противоположного пункта на выходе сумматора 5 по модулю два появляется постоянно высо- кий уровень (инверсной ПСП). Этот сигнал через инвертор 8 поступает на интегратор 10 обратного кода и через интервал времени, определяемый временем интеграции, на вьпсоде интеграто- ра 10 обратного кода появляется высокий уровень (сигнал приема обратного кода). Этот сигнал поступает на второй вход сумматора 11 псз модулю два, который осуществляет инверс1-по сигналов, поступающих с выхода сумматора 5 по модулю два. Для обратной ПСП ошибки - сигнал низкого уровня на выходе сумматора 5 по модулю два. Эти сигналы инвертируются сумматором 11 по модулю два и в блок 13 анализа поступают ошибки. Одновременно высокий уровень с выхода интегратора 10 обратного кода поступает в блок 13 анализа, что несет информацию об исправности канала в прямом направлении Таким образом, приемная часть устройства продолжает осуществлять контроль ошибок по инвертированной ПСП.

Если приемная часть устройства принимает обратный код и через некоторое время формирует сигнал Канал исправен, то формируется обобщенный сигнал Канал исправен в блоке 13 ана:шза, свидетельствующий об исправности дуплексного канала. Причем этот сигнал формируется практически одновременно на обоих концах канала.

Если во время контроля канала по обратному коду происходит скачок фазы или из-за большого пакета ошибок сформируется сигнал Блокировка, то блок 14 расфазирования формирует сигнал Сброс, которым оба интегратора 9 и 10 переводятся в исходное состояние. При этом ключом 2 размьпсается цепь обратной логической связи и начинается новый процесс фазирования приемной части устройства. Так как при этом На прием поступает обратный код (инвертированная ПСП), то сначала по инвертированной ПСП срабатывает интегратор 10 обратного кода, при этом открьшается элемент И б, так как на второй вход элемента И б поступает высокий уровень от инвертора 7, на вход которого поступает низкий уровень от интегратора 9 прямого кода. Сумматор 1 по модулю два начинает инвертировать входную информацию и на выходе появляется прямая ПСП, по которой осуществляется фазирование. При этом срабатывает интегратор 9 прямого кода, закрывается элемент И б, сумматор 1 по модулю два перестает инвертировать поступающую на его вход информацию и открьшается элемент Н 12. Устройство переходит в контроля ошибок по обратному коду.

Формула изобретения

Устройство для контроля дуплексно- i o канала связи по авт.св. № 1061280, отличающееся тем, что, с целью повышения достоверности контроля при изменениях полярности сигнала в дискретном канале связи, в него введены в передающей части опорный генератор, элемент И-НЕ и первый триггер, а в приемной части - второй и третий триггеры и шестой и седьмой сумматоры по модулю два, при этом выход третьего сумматора по модулю два соединен с входом канала связи через последовательно соединенные элемент И-НЕ, второй вход которого соединен с тактовым входом датчика ПСП и с выходом опорного генератора, и первый

JC ffpGo5jya3o8offlJ& f7flAf t ij /7С/Т

1 11 010011101001

а 1 а 1 100010110001 от а 110001011000

1 1 1010011101001

1010011101001110

1 о 100111010011 1

1 1 1010011101001

ж fJpsoSpaaoBctHue имЗерснаи ПСП

О 00 laiiaooioiiooaioji 1 1 1 т а о 7 о о о о 1-1 о 1 т 1 1 о о J о

1 100100001101111001 о OOIQ 11000 10110001 011

oooiioiiiioaioooofjoj

о о о о 1 101 1 1 j о о 1 00 о о г г и

о о о 1 о t 1 о о о

1011000 10

1 1

Редактор А.Ревин Заказ 2662/58

Составитель В.Слепаков

Техред О.Гортвай Корректор С.Шекмар

Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раутаская наб., д. 4/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

трип ер, выход первого элемента И соединен с первым входом блока анализа через тестой сумматор по модулю два, 5 второй вход и выход которого соединены соответственно с выходом и с первым входом второго триггера, а выход канала связи соединен с первым входом четвертого сумматора по моду10 лю два через последовательно соединенные третий триггер и седьмой сумматор по модулю два, второй вход которого соединен с первым входом третьего триггера, второй вход которого

15 являющийся входом тактовых импульсов устройства, соединен с вторым входом третьего триггера и с тактовыми входами регистра, интегратора прямого кода, интегратора обратного кода и

20 блока расфазирования.

1011000 10

1 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дуплексного канала связи | 1982 |

|

SU1061280A1 |

| Устройство для передачи и приема дискретной информации | 1985 |

|

SU1298942A2 |

| Устройство фазирования псевдослучайных последовательностей | 1986 |

|

SU1381726A1 |

| Устройство для контроля дискретного канала | 1984 |

|

SU1298930A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Система телемеханики | 1986 |

|

SU1363282A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| Приемник биимпульсного сигнала с обнаружением ошибок | 1989 |

|

SU1658401A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

Изобретение относится к электросвязи. По отношению к авт. св. № 1061280 поБьппается достоверность контроля при изменениях полярности сигнала в дискретном канале связи. Устройство содержит в приемной части шесть сумматоров (С) 1, 4, 5, П, 20 и 23 по модулю два, ключ 2, регистр 3, два элемента И 6 и 12, два инвертора 7 и 8, интегратор 9 прямого кода, интегратор 10 обратного кода, блок расфазирования 14 и два триггера (Т) .. 21 и 22; в передающей части - С 15 по модулю два, датчик 16 псевдослучайной последовательности, опорный генератор 17, элемент И-НЕ 18 и Т 19, а также блок анализа (БА) 13. Ошибки, присутствующие во входной информации, поступают через открытый элемент И 12 и С 20 на вход БА 13. Для исключения возможности удвоения ошибок, вызванных преобразованием информации в Т 22 и С 23, введен С 20. Если в течение времени анализа в БА 13 поступает допустимое для заданного критерия качества число ошибок, то БА 13 формирует для обратного направления сигнал Канал исправен и высокий уровень поступает на вход С 15, который начинает инвертировать псевдослучайную последовательность, формируемую датчиком 16. Цель достигается введением опорного генератора 17, элемента И-НЕ 18, Т19,21и22 и С 20 и 23. 2 нл. о (Л I jO 35 to ISJ

| Устройство для контроля дуплексного канала связи | 1982 |

|

SU1061280A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-05-15—Публикация

1983-07-27—Подача