1

Изобретение относится к технике связи и может использоваться для декодирования сигналов, передаваемых по линейньн- трактам цифровых ситем передачи в кодг1Х КВП-п .

Известен преобразователь кода, содержащий блок разделения полярностей, выходы которого подключены к , входам двух регистров сдвига, два дешифратора и элемент ИЛИ U.«

Однако этот преобразовате.ль ко да обладает низкой помехоустойчивостью. ,

Целью изобретения является повышение помехоустойчивости.

Для этого в преобразователе кода, содержащем блок разделения полярностей, выходы которого подключены к входам двух регистров сдвига, два дешифратора и элемент ИЛИ, выходы (п-1) разрядов первого регистра сдвига и один из выходов второго дешифратора подключены к соответствующим входам первого дешифратора, выходы которого подключены к входам установка соответствующих разрядов первого регистра сдвига и. к одному из входов второго дешифратора, к другим входам

которого подк.гаочены выходы (п-1) разрядов второго рег-йстра сдвига, к входам установка нуля соответствующих разрядов подключены соответствующие выходы второго дешифратора, а выходы п-ых разрядов первого и второго регистров сдвига подключены к входам элемента ИЛИ.

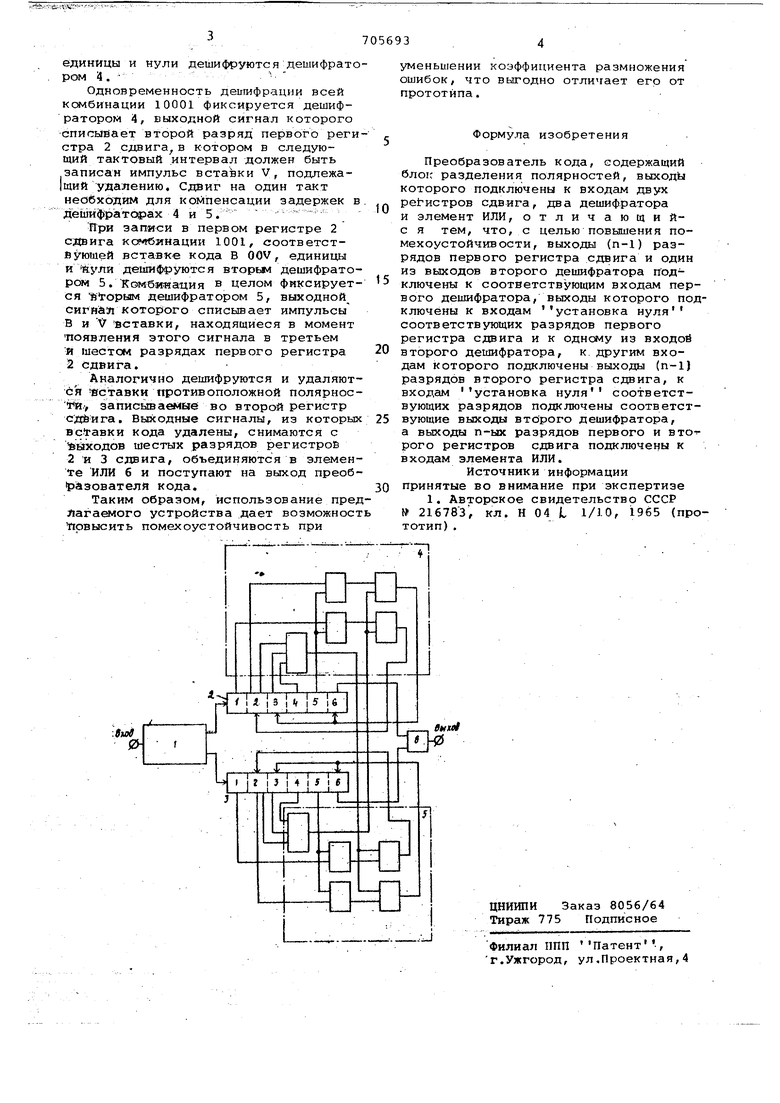

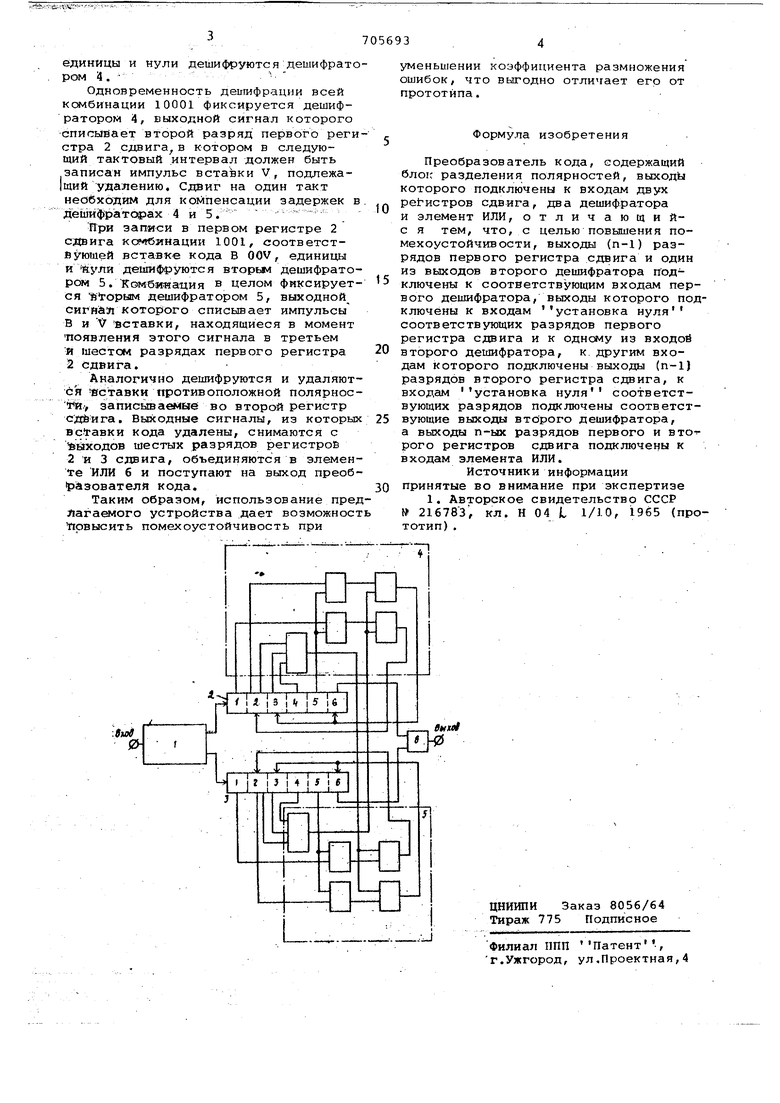

На чертеже приведена функциональ0ная электрическая схема предлагаемого устройства.

Преобразователь кода содержит блок 1 разделения полярностей, два регистра сдвига 2 и 3, два дешифра5тора 4 и 5 и элемент ИЛИ б.

Устройство работает следующим образом.

В блоке 1 разделения полярностей входной биполярный цифровой сигнал

б с вставками кода КВП-3 разделяется на два цифровых потока, соответствующих полярностей входного сигнала и Находящимся в противофазе относительно друг друга. Эти потоки эа5писываются в регистры 2 и 3 сдвига и.продвигаются с тактовой частотой сигнала. При записи в первом регистре 2 сдвига комбинации 10001, соответствующей вставке кода OOOV,

единицы и нули дешифруютсяДешифратором 4 .

Одновременность дешифрации всей ксмбинации 10001 фиксируется дешифратором 4, выходной сигнал которого списыйает второй разряд первого регистра 2 сдвига в котором в следующий тактовый интервал должен быть записан импульс вставки V, подлежащий удалению. Сдвиг на один такт необходим для компенсации задержек в дешифраторах 4 и 5. - /.

-При записи в первом регистре 2 сдвига кс «бинации 1001, соответствующей вставке кода В OOV, единицы и йули дешифруются вторьм дешифраторам 5. Комбинация в целом фиксируется йгорым дешифратором 5, выходной сигнал которого списывает импульсы В и V вставки, находящиеся в момент появления этого сигнала в третьем И шестом разрядах первого регистра 2 сдвига.

Аналогично дешифруются и удаляются «ставки противоположной полярнос№ записываемые во второй регистр сдйига. Выходные сигналы, из которых вс-гавки кода удалены, снимаются с йходов шестых разрядов регистров 2 И 3 сдвига, объединяются в элементе ИЛИ б и поступают на выход преоб|рйзователя кода.

Таким образом, использование предЛагаетлого устройства дает возможност Повысить помехоустойчивость при

г

705693

уменьшении коэффициента размножения ошибок, что выгодно отличает его от прототипа.

Формула изобретения

Преобразователь кода, содержащий блогс разделения полярностей, выходЬ которого подключены к входам двух регистров сдвига, два дешифратора и элемент ИЛИ, отличающийс я тем, что, с целью повышения помехоустойчивости, выходы (п-1) разрядов первого регистра сдвига и один из выходов второго дешифратора подключены к соответствующим входам первого дешифратора, выходы которого подключены к входам установка нуля соответствующих разрядов первого регистра сдвига и к однсму из входой второго дешифратора, к. другим входам которого подключены выходы (п-1) разрядов второго регистра сдвига, к входам установка нуля соответствующих разрядов подключены соответствующие выходы второго дешифратора, а выходы п-ых разрядов первого и второго регистров сдвига подключены к входам элемента ИЛИ.

Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР 216783, кл. Н 04 i 1/10, 1965 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода | 1980 |

|

SU965001A1 |

| Преобразователь кода | 1981 |

|

SU1054916A2 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Устройство для преобразования цифрового сигнала | 1982 |

|

SU1109925A1 |

| Кодер совместимых кодов высокойплОТНОСТи | 1979 |

|

SU843223A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И УСТРАНЕНИЯ ФАЗОВОЙ НЕОДНОЗНАЧНОСТИ СИГНАЛОВ СИСТЕМ СВЯЗИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2010 |

|

RU2444849C2 |

| Устройство для формирования многопозиционныхбиОРТОгОНАльНыХ шуМОпОдОбНыХСигНАлОВ | 1979 |

|

SU841091A1 |

| Устройство для обнаружения ошибок цифрового сигнала в контролируемых кодах | 1981 |

|

SU959289A1 |

| Преобразователь кода КВП- @ | 1985 |

|

SU1347189A1 |

| Устройство для передачи и приема дискретных сигналов | 1987 |

|

SU1494024A1 |

i

Тг |з U |5 U

1, ,

1Г

.Ч1ЕШ1Ш

Ф

SMUt

h0

Авторы

Даты

1979-12-25—Публикация

1978-06-26—Подача