( УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК ЦИФРОВОГО

: .. .

f , Изобретение относится к технике связи и может быть использовано в цифровых линиях связи для контроля линейного сигнала в кодах.

Известно устройство для обнаружения ошибок цифрового сигнала в Контролируемых кодах, содержаи(ее пбследоват(ельно соединенные блок па мяти и накопитель, а также два блока совпадения Пт.

Однако известное устройство обладает низкой достоверностью обнар о|(ения ошибок.

Цель изобретения - повышение досп товерности обнаружения ошибок при увеличении числа контролируемых ко: дов.:; . . ... .;. ;, :;/: :

Для этого в устройство для обнару. жения ошибок цифрового сигнала в контролируемых кодах, содержащее последовательно соединенные блЬк па Мити и накопитель, а также два блока совпадения, введены регистр сдвиСИГНАЛА В КОНТРОЛИРУЕМЫХ КОДАХ

га, объединенные по первому входу два блока управления, два дешифратора и формирователь сигнала ошибок, к входам которого подключены выходы двух блоков совпадения , к первым : входам которых, а также к входам блока памяти подключены выходы первого и второго дешифраторов, а к вторым входам блоков совпадения подключены выходы накопителя, при

10 этом первый вход регистра сдвига является первым входом устройства, второй вход регистра сдвига объединен с первыми входами пешифраторов и третьим входом накопителя, а выхо

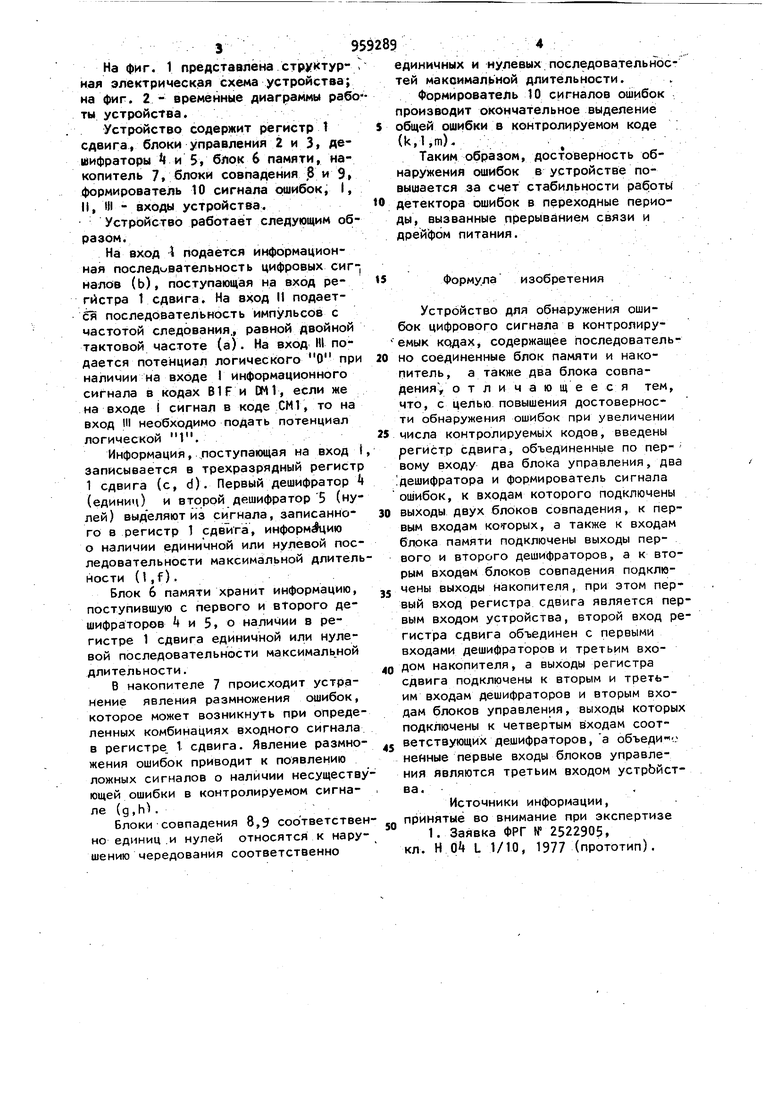

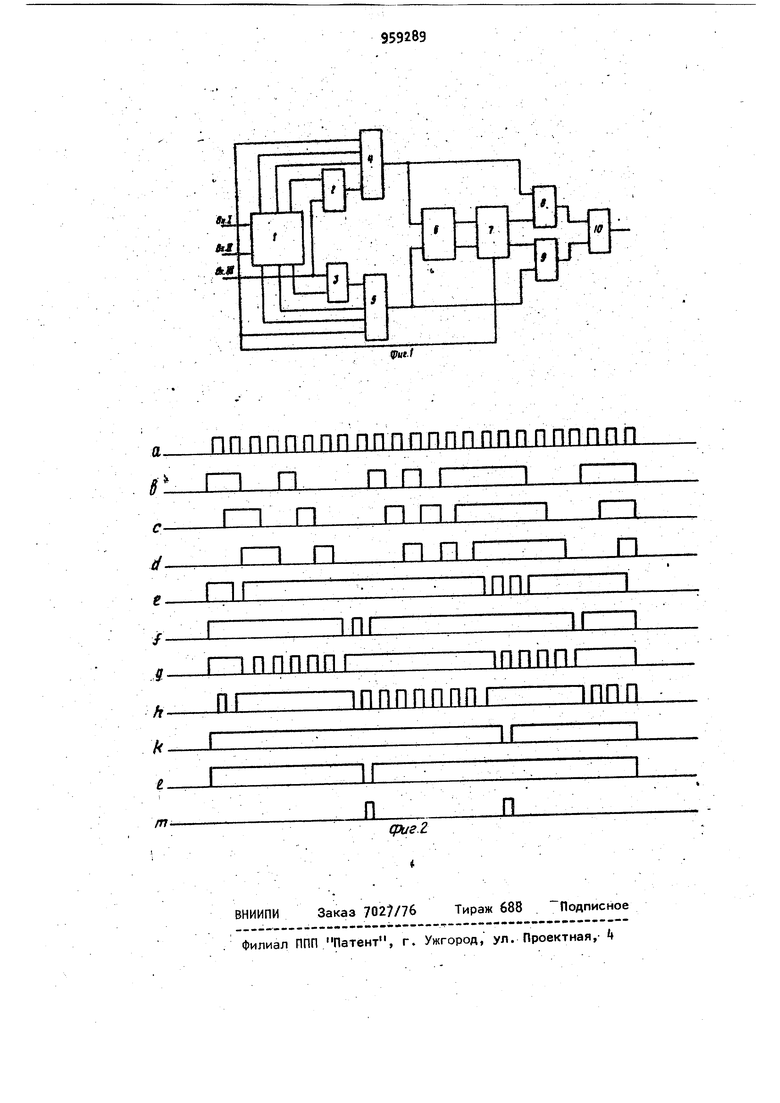

15 ды регистра сдвига подключены к вторым и третбим входам дешифраторов . и вторым входам блоков управления, выходы которых подключены к четвер20тым входам соответствующих дешифра-, торов, а объединенные первые входы, .блоков управления являются третьим входом устройства. 39 На фиг. 1 представлена структурнал электрическая схема устройства; на фиг. 2 временные диаграммы рабо ты устройства. Устройство содержит регистр t сдвига, блоки управления 2 и 3 дешифраторы и 5, блок 6 памяти, накопитель 7, блоки совпадения 8 и 9, формирователь 10 сигнала ршибок, I, II, Ш - входы устройства. Устройство работает следующим образом. На вход подается информационная последовательность цифровых сиг-; налов (Ь), поступающая на вход регистра 1 сдвига. На вход И подается последовательность импульсов с частотой следования., равной двойной тактовой частоте (а). На вход HI подается потенциал логического О при наличии на входе I информационного сигнала в кодах B1F и DM 1, если же на входе I сигнал в коде СМ 1, то на вход 111 необходимо подать потенциал логической t. Информация, поступающая на вход I записывается в трехразрядный регистр 1 сдвига (с, d). Первый дешифратор (единим) и второй дешифратор5 (нулей) выделяют из сигнала, записанного в регистр 1 сдвига, информ ию о наличии единичной или нулевой последовательности максимальной длитель ности (1,f). Блок 6 памяти хранит информацию, поступившую с первого и второго дешифраторов Ц и 5, о наличии в регистре 1 сдвига единичной или нулевой последовательности максимальной длительности. В накопителе 7 происходит ycTpiaнение явления размножения ошибок, которое может возникнуть при определенных комбинациях входного сигнала в регистре. 1 сдвига. Явление размножения ошибок приводит к появлению ложных сигналов о наличии несуществу ющей ошибки в контролируемом сигнале (g,hK Блоки совпадения 8,9 соответствен но единиц .и нулей относятся к нарушению чередования соответственно единичных и нулевых последовательностей макоимальной длительности. Формирователь 10 сигналов ошибок производит окончательное выделение общей ошибки в контролируемом коде (k,l,m). Таким образом, достоверность обнаружения ошибок в устройстве повышается за счет стабильности работы детектора ошибок в переходные периоды, вызванные прерыванием связи и дрейфом питания. Формула изобретения Устройство для обнаружения ошибок цифрового сигнала в контролируемык кодах, содержащее последовательно соединенные блок памяти и накопитель, а также два блока совпадения, отличающееся тем, что, с целью повышения достоверности обнаружения ошибок при увеличении числа контролируемых кодов, введены регистр сдвига, объединенные по первому входу два блока управления, два дешифратора и формирователь сигнала ошибок, к входам которого подключены выходы двух блоков совпадения, к первым входам которых, а также к входам блока памяти подключены выходы первого и второго дешифраторов, а к вторым входам блоков совпадения подключены выходы Накопителя, при этом первый вход регистра сдвига является первым входом устройства, второй вход регистра сдвига объединен с первыми входами дешифраторов и третьим входом накопителя, а выходы регистра сдвига подключены к вторым и третьим входам дешифраторов и вторым входам блоков управления, выходы которых подключены к четвертым входам соответствующих дешифраторов,а объеди-ч... ненные первые входы блоков управления являются третьим входом устрЬйства. Источники информации, принятые во внимание при экспертизе 1. Заявка ФРГ № 2522905, кл. Н О L 1/10, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок цифрового сигнала в контролируемых кодах | 1984 |

|

SU1290539A1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для контроля информации | 1983 |

|

SU1174928A2 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для контроля неисправностей в цифровой системе связи | 1983 |

|

SU1104574A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство для обнаружения ошибок цифрового сигнала | 1981 |

|

SU1012451A1 |

Авторы

Даты

1982-09-15—Публикация

1981-02-25—Подача